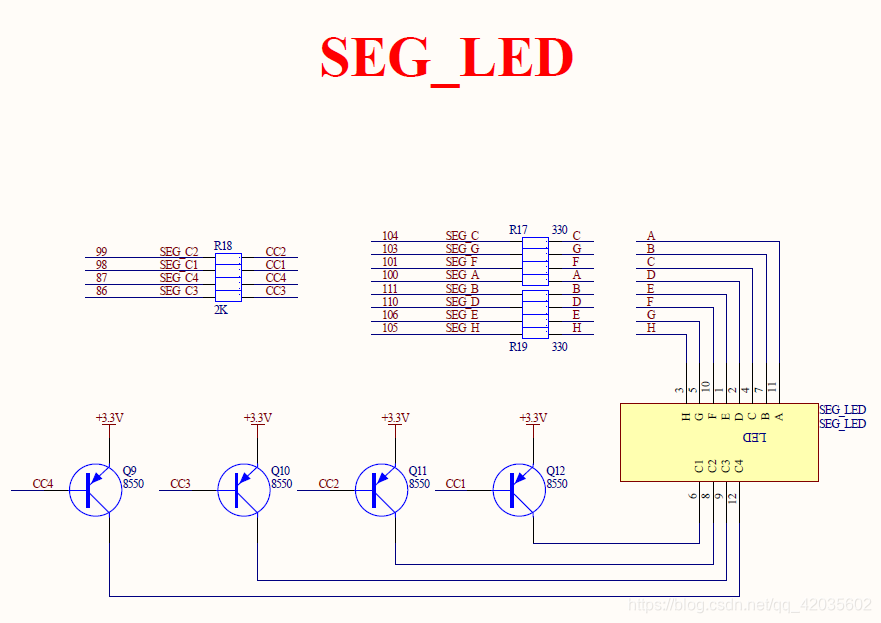

一、硬件设备是FPGA入门开发板EP4CE6E22C8,数码管的原理图如下:

段选信号abcdefh是低电平有效,其中h是数码管右下角的小数点。CC1-CC4为四个数码管的片选信号,也是低电平有效。

二、数码管段选信号abcdefgh与数字0-9的对应表如下:

| abcdefgh电平 | 数字字符 |

| 0000 0011 | 0 |

| 1001 1111 | 1 |

| 0010 0101 | 2 |

| 0000 1101 | 3 |

| 1001 1001 | 4 |

| 01001001 | 5 |

| 0100 0001 | 6 |

| 0001 1011 | 7 |

| 0000 0001 | 8 |

| 0000 1001 | 9 |

三、设计思路:

由于四个数码管的段选信号是并联在一起的,所以要做到四个数码管能分别显示不同的字符,那么就控制片选信号CC1-CC4在一个时间点,只有一个片选信号有效,即一个时间节点只有一个数码管显示字符。将片选信号CC1-CC4选择使能的时间加快,利用人眼的视觉暂留现象,就可以四个数码管同时显示了。单个数码管的刷新频率大于50Hz就可以达到效果,四个数码轮流刷新,所以整体刷新频率为200Hz。

1、计数模块 2、显示(译码)模块 3、刷新显示模块

1、计数模块:

本实验要达到间隔1s计数,那么需要一个1Hz的时钟,时钟源为50MHz。

--1s时钟模块

Module_1Hz : process(clk)

begin

if(clk'event and clk='1')then

if(cnt_50MHz=49999999)then

cnt_50MHz<=0;

else

cnt_50MHz<=cnt_50MHz+1;

end if;

if(cnt_50MHz<=24999999)then

clk1Hz<=1;

else

clk1Hz<=0;

end if;

end if;

end process module_1Hz;--1s计数模块,四个数码管累加显示数字,范围0000-9999

Module_cnt : process(clk1Hz)

begin

if(clk1Hz'event and clk1Hz=1)then

if(cnt_One=9)then

if(cnt_Ten=9)then

if(cnt_Hundred=9)then

if(cnt_thousand=9)then

cnt_thousand<=0;

cnt_Hundred<=0;

cnt_Ten<=0;

cnt_One<=0;

else

cnt_thousand<=cnt_thousand+1;

cnt_Hundred<=0;

cnt_Ten<=0;

cnt_One<=0;

end if;

else

cnt_Hundred<=cnt_Hundred+1;

cnt_Ten<=0;

cnt_One<=0;

end if;

else

cnt_T

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1112

1112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?