今天遇到了一个问题,在tb中写入:

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars;

end然后进行vcs仿真,用了两个vcs仿真指令,有一个可以通过仿真生成fsdb文件,另一个始终报undefined system task call $fsdbDumpfil(大概是这样的一个log信息)。上网搜这个log信息是因为verdi的地址没有配置正确,但是不同的vcs指令另一个可以跑通,显然不是这个原因。因此想了解一下vcs仿真dump出波形的方法,并且看看错误究竟在哪里?

原因没有加-full64

fsdb #FSDB文件是Verdi 支持的波形文件,通过verilog的PLI接口,$fsdbDumpfile,$fsdbDumpvars等函 数来实现。

1. $fsdbDumpfile 函数

语法解析:

$fsdbDumpfile(fsdb_name[,limit_size])

含义:

指定波形文件名,第二个参数可选择用来限制波形的大小(MB)。

例如:

$fsdbDumpfile(“tb_top.fsdb”,10240);

其中文件名可能被$fsdbDumpvars覆盖。

2. $fsdbDumpvars 函数

语法解析:

$fsdbDumpvars([depth, instance][, “option”])

含义:

depth:表示要加载波形的层次;0表示当前instance下的所有变量以及其它module实例的波形,1表示当前instance中的变量的波形,不包括当前instance中的其它module实例的波形,2表示包含当前instance以及其中的第一级子instance的波形;以此类推。

instance:指定要加载波形的module名。

option:加载波形的选项,如:

| +all | 加在以下所有选项。。。 |

| +IO_Only | 只加载IO port信号 |

| +Reg_Only | 只加载reg类型信号 |

| +mda | 加载all memory signals 和MDA信号 |

| +packedmda | 加载packed MDA |

| +struct | 加载structs(默认开启) |

| +power | 加在power 相关信号(默认开启) |

| +parameter | 加载parameter |

| +strength | 使能strength dumping |

| +fsdbfile+filename | 指定fsdb文件名字 |

举例:

$fsdbDumpvars(0,“tb_top”,"+power","+struct","+mda");verilog仿真中几种生成fsdb波形的方式 - 知乎(待试验一下)是否如此

如何用vcs输出fsdb格式的波形 - 尚码园![]() https://www.shangmayuan.com/a/10afe7c42ec04e089064a8d1.html

https://www.shangmayuan.com/a/10afe7c42ec04e089064a8d1.html

定义这个宏这么重要

好吧 ,上面都是废话,用最简单的例子记录一下

testbench中增加

仿真命令

full64一定要有,pli可以没有

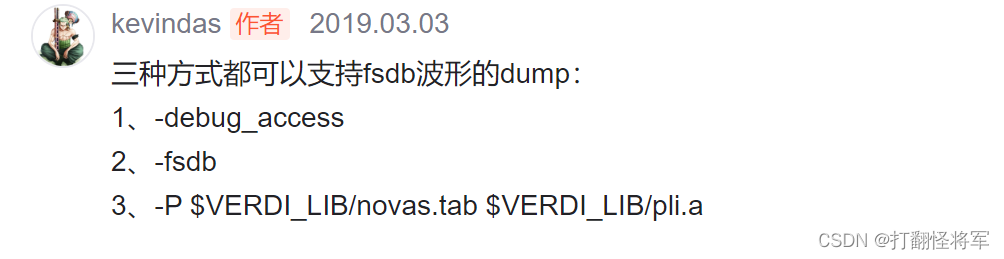

vcs -R -sverilog test_wire.sv wire.sv -full64 -debug_access -P ${LD_LIBRARY_PATH}/novas.tab ${LD_LIBRARY_PATH}/pli.a

1363

1363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?