传播延时:时钟沿到来时,到触发器能够输出的时间。中间经历了寄存器数据的采样、逻辑运算、然后输出,相当于时钟上升沿到数据能输出的那段时间。

建立时间:时钟沿到来之前,输入数据至少需要保持稳定的时间

保持时间:时钟沿到来之后,输入数据至少需要保持稳定的时间

针对这三个时间,首先我理解,对于一个触发器来说,他的传播延时应该大于保持时间。引起如果自己的传播延时小于自己的保持时间,要这么大的保持时间根本没有意义。

其次,建立时间、保持时间和传播延时和logic延时概念上不同。建立和保持时间,是人为定义出的时间,是一个参考的量,是一个标准,是寄存器对于输入信号的一个要求。而传播延时和logic延时是真正耗费的时间,是器件在运转中真正需要的时间,是现实的时间。理解了这个概念,会对后面的计算很有帮助。

1、保持时间的理解(难理解)

1)保持时间

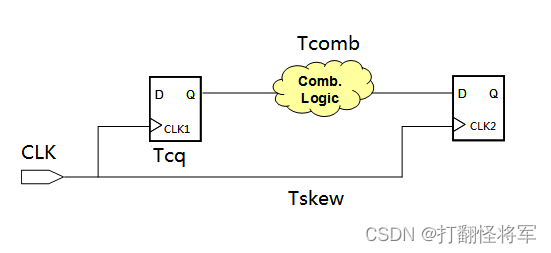

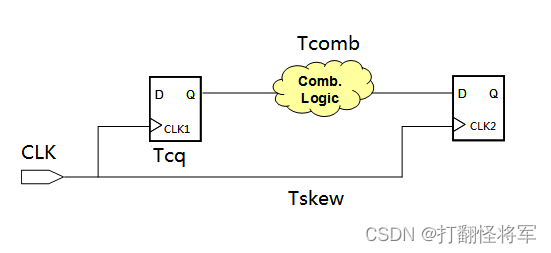

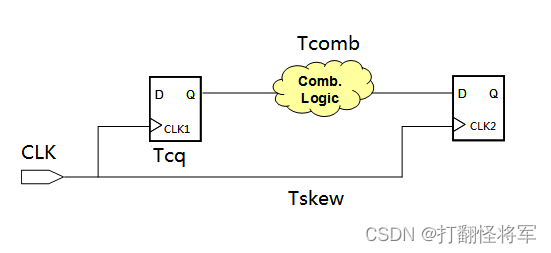

针对保持时间来看,要保证的是D2的输入信号要保持一段时间,而不至于被D1产生的新信号改变。也就是说D1产生的新信号要在D2输入信号的保持时间达到之后来到。

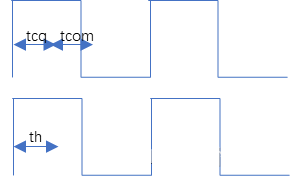

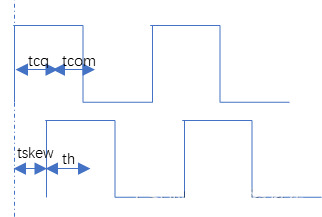

由图,分别为D1和D2,D1触发器产生的新信号会经过D1的传播延时和D1和D2之间组合逻辑即Tcq_d1+Tcomb后,才改变logic输出的值到D2输入上。所以只要要求保持时间小于Tcq_d1+Tcomb,就能满足D2触发器的保持时间。

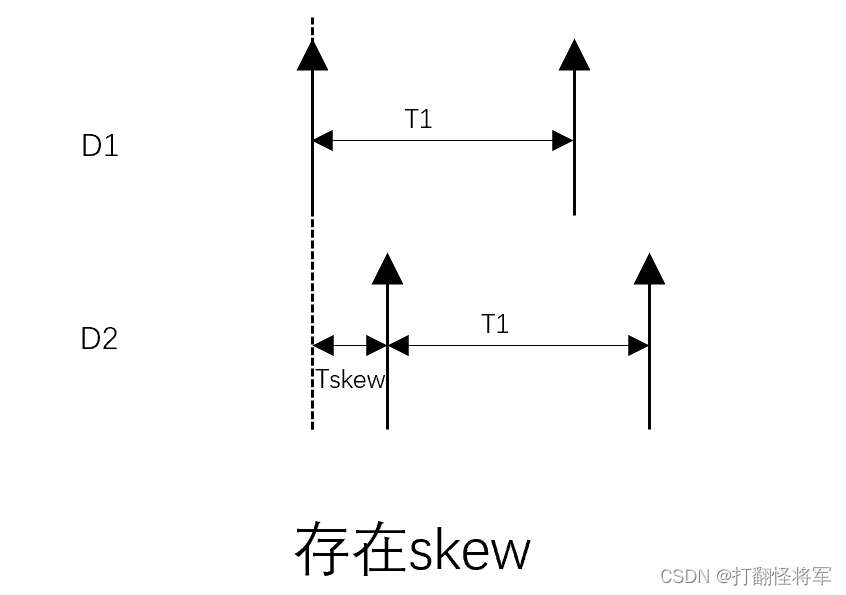

2)clk存在skew的保持时间

首先,理解skew,指的是由于线路中布线的影响,使得时钟信号到达不同的触发器的时间不同。

同样的,还是要求D1产生的新信号要在D2输入信号的保持时间结束时到来,这样就要求了:Tcq+Tcom > Tskew+Th,这样可以看出如果D2存在skew的话,会对保持时间要求更严格了。同时也可以看出时钟频率和保持时间无关,时钟频率不影响保持时间。

3)存在jitter

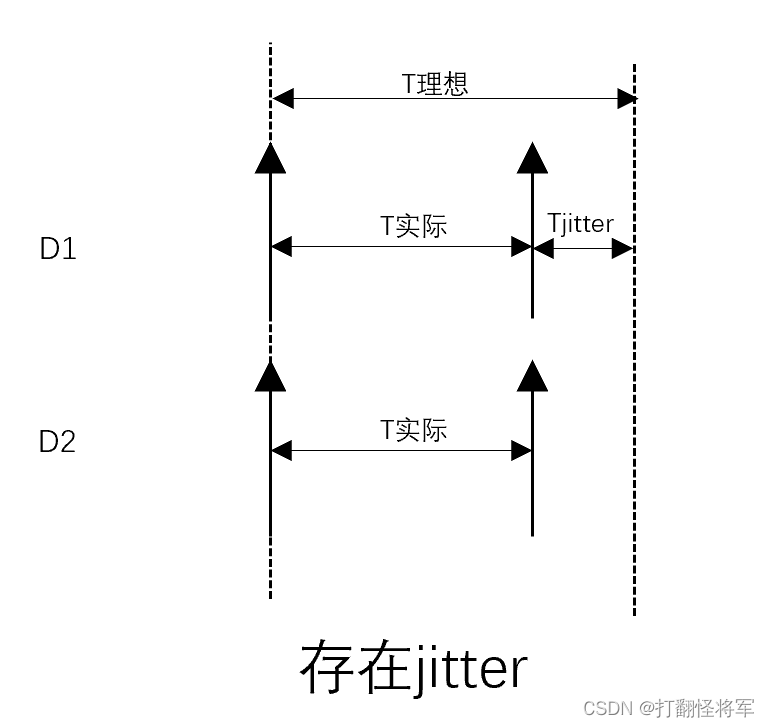

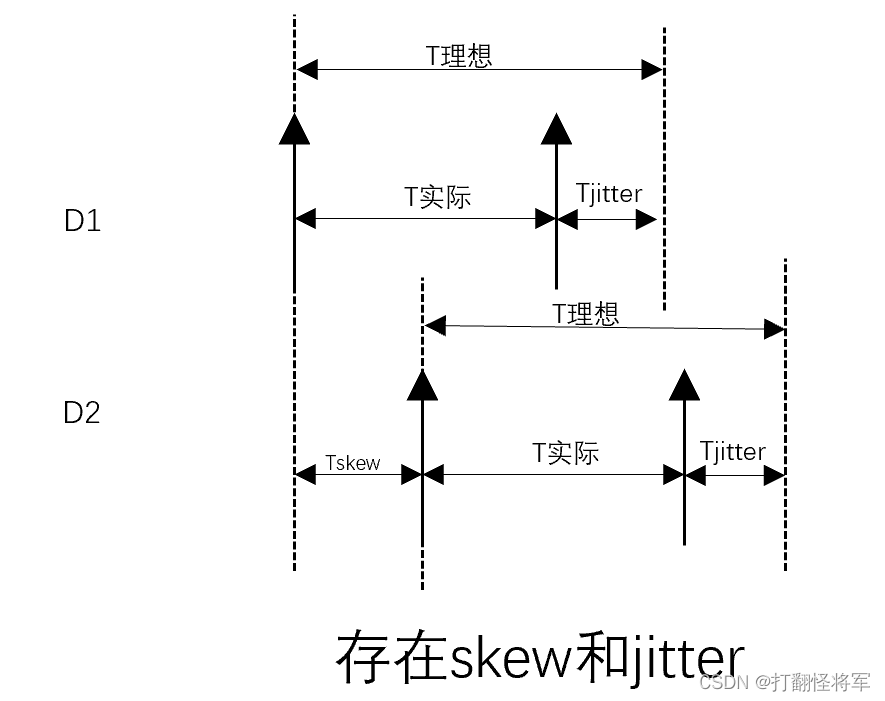

首先时钟jitter的概念

Clock Jitter(时钟抖动):是指芯片在某个给定的时间点上时钟周期发生暂时性变化,从而导致时钟在不同的周期上加长或者变短。换句话来说就是指,两个时钟周期之间存在差值,这个误差是在时钟内部产生的,与晶振或者内部的PLL有关,与时钟的布局布线无关。(由于时钟内部产生的原因,导致时钟有加长和变短的行为,前后两个时钟周期不同)

具体如下图所示:

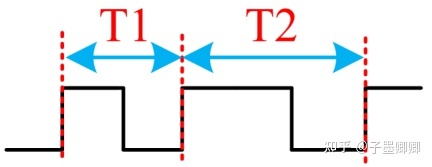

根据上图可以算出抖动值为:Clock Jitter = T2 - T1。(后一个周期减去前一个周期?)根据我们上面的推理,时钟jitter对保持时间没有影响。

抖动的定义为“信号的定时事件与其理想位置之间的偏差”,jitter = T理想 - T实际

视角的不同:

保持时间看的是两个触发器,同一次时钟上升沿到来后,前一个触发器生成新信号的时间和旧信号应该保持的时间的比较。它在乎的是电路的延时。因此保持时间和skew有关,和时钟周期无关,和时钟jitter无关(jitter带来了周期的改变)。D2出现skew(D2的时钟比D1的时钟晚到)会对保持时间要求更严格。jitter(若jitter为正值=T理想-T实际)的出现会让建立时间更严格(时间更短)

而建立的时间看的是能不能在一个时钟周期内完成延时和信号的建立。。建立时间和jitter和时钟周期有关,与skew都有关。D2出现skew(D2的时钟比D1的时钟晚到)会对建立时间放松(时间更多)。

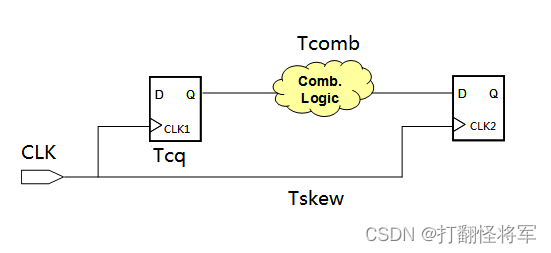

简便方法做题的时候对着这个图做就好了

最后建立时间和保持时间的公式

针对这个电路:

D2的建立时间的约束: Tcq1+Tlogic+Tsu2 <T+Tskew-Tjitter,愚蠢的我认为应该有一个Tcq>Tskew的约束,否则这一拍的Q可能直接被skew后的时钟采集到。

D2的保持时间的约束:Tcq1+Tlogic > Tskew+Thold。

太棒了,感觉至少此刻理解的很透彻了对于建立时间和保持时间的计算!

这边再提出两个时钟的概念:Tlanch和Tcapture

Tlaunch和Tcapture分别为始终到达UFF1和UFF2的时间延时,定义Tskew为Tcapture - Tlaunch。

另外补充温度和电压对他们的影响,

1)温度越高,时延越高,要求D触发器的建立时间更加严格(建立时间越小越不会违例),如果很大就会违例。要求D触发器的保持时间越宽松(D触发器保持时间大一点也没事,因为时延长了)因此温度高,可能会造成建立时间不满足,而有利于保持时间。

2)电压越高,时延越小。越有利于建立时间,越不利于保持时间。所以温度过高会带来保持时间的违例。

参考资料:

原理性角度的分析:(里面推荐了一本书,有空看下,flag)

FPGA之道(75)静态时序分析(一)基本概念介绍_李锐博恩的博客-CSDN博客

做题的角度,好多例题。

IC常用基础知识1-setup time和hold time 总结_mu_guang_的博客-CSDN博客_setuptime和holdtime

极限情况的理解

对Setup time 和Hold time计算关系的理解_limanjihe的博客-CSDN博客_setup time计算

holdtime setup time负值的理解

STA setup/hold time可以是负数么?_luoai_2666的博客-CSDN博客_建立时间为负

hold time的负值问题_feiyang756的博客-CSDN博客

后续有时间再将建立时间的计算方式补充(当然建立时间很好理解)(flag)以及立和保持时间在cmos电路中对标的参数究竟是什么,解释以下触发器为什么需要满足这两个时间。

480

480

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?