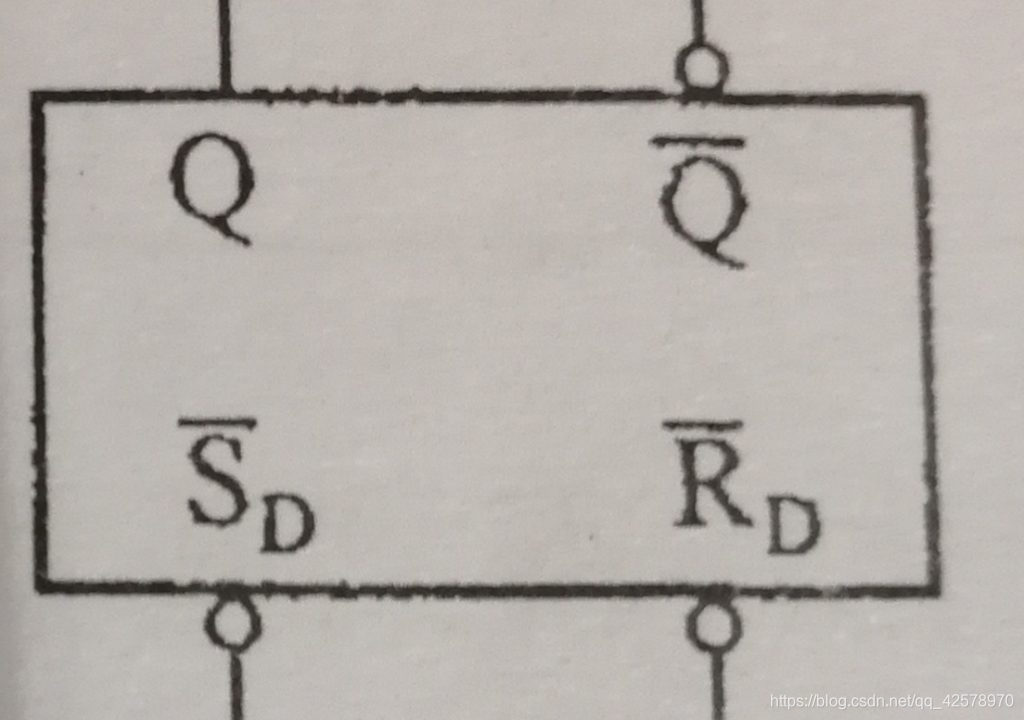

一、基本RS触发器

两个输入端不同时,Q的值与RD反相同(与SD相同)

都为1时,保持,都为0时,Q和Q反状态不确定,理论上不允许出现

缺点:没时钟信号,可以快速切换,且没有处理输入同时为0的情况

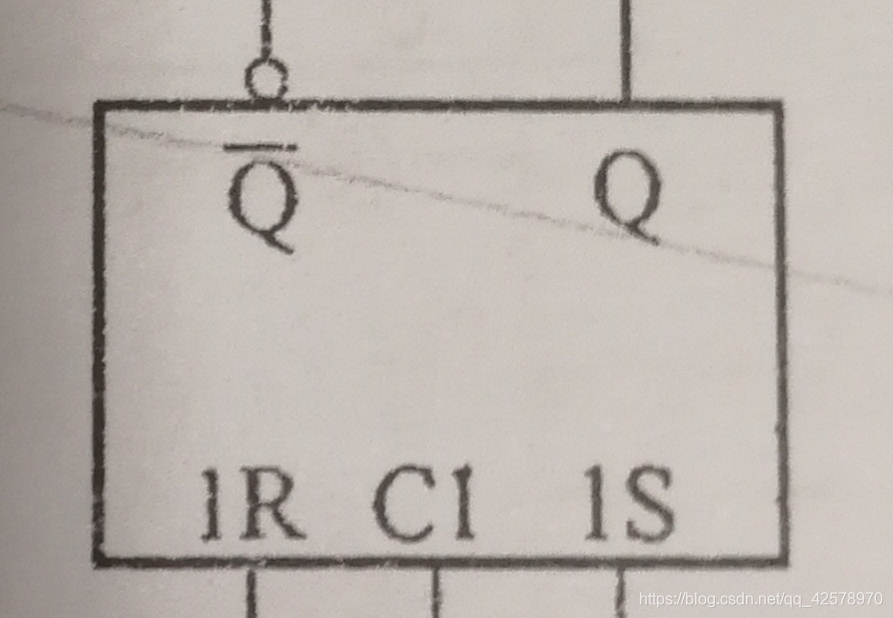

二、同步RS触发器

JXTA R如果有干扰信号,就可能引起Q和Q非的状态转换

Q依然跟随S,与R相反。

同为1时保持,同为0无效

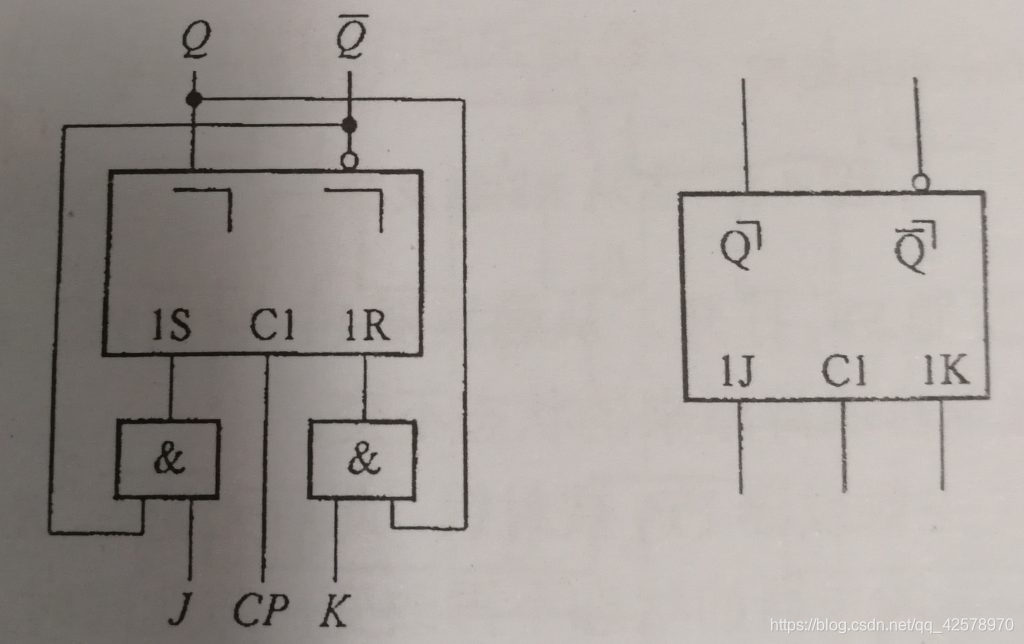

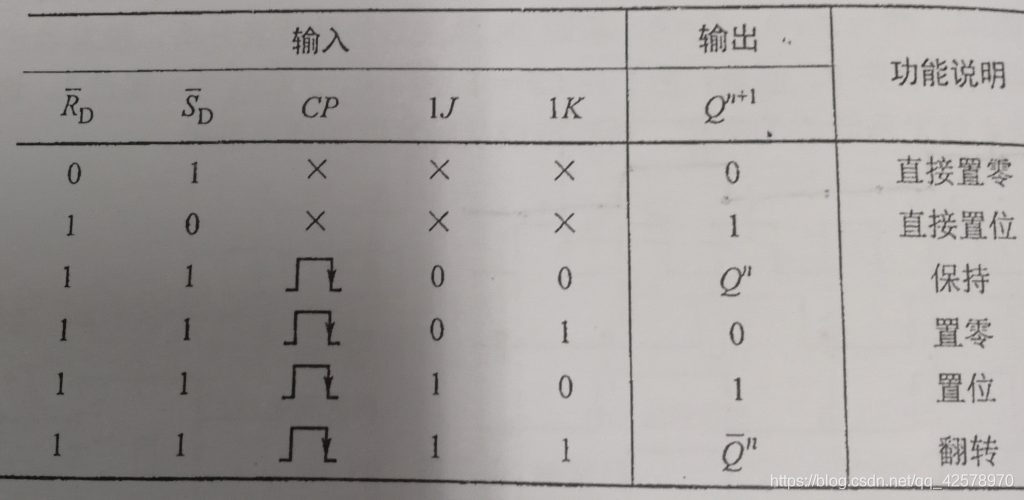

三、主从JK触发器

在同步RS的基础上加入了反馈。解决了干扰信号导致的在时钟信号转换之外的翻转和RS同时为0的问题。

这里转换发生于时钟信号的下降沿

JK不同时,Q跟随J

同为1,翻转,同为0,保持。比如Q此时为1,JK同时为1,则时钟信号下降沿来临时,Q变为0

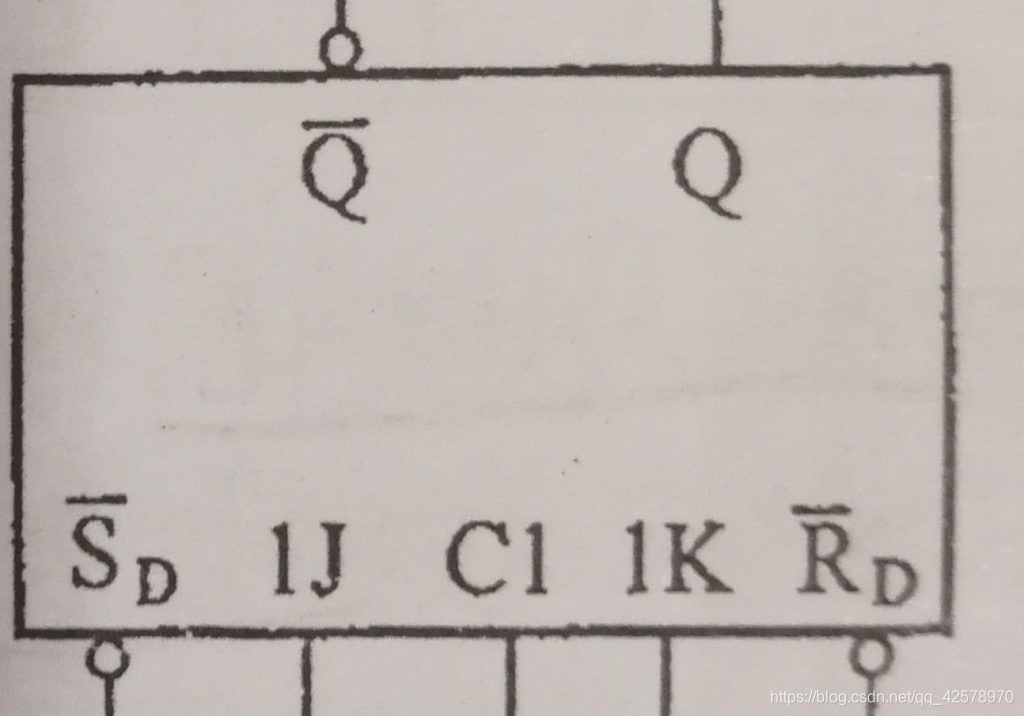

四、集成主从JK触发器

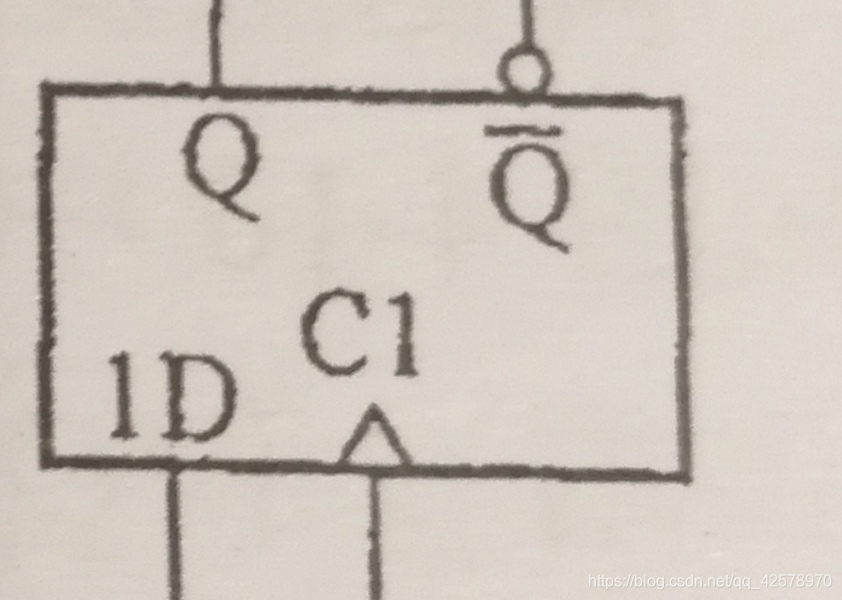

五、边沿触发器 D触发器

时钟信号上升沿来临时,Q=D

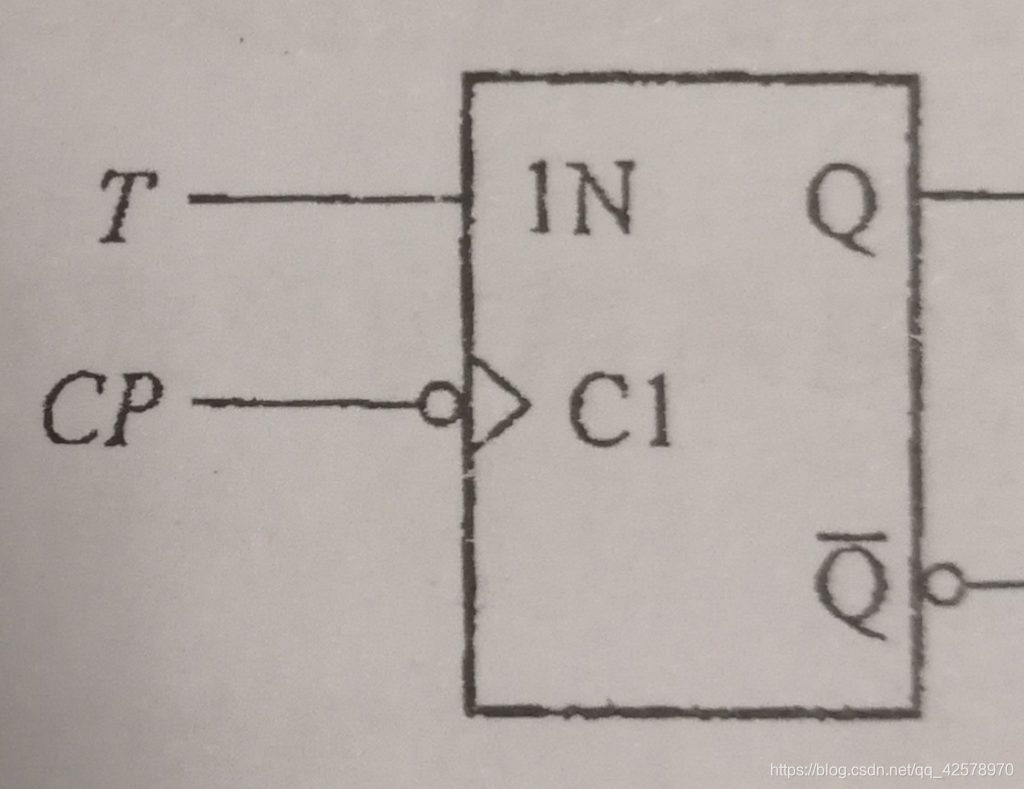

六、T触发器

CP输入端有个小圆,说明信号下降沿处才可能发生状态变换。

T=0时,保持,T=1时,Q和Q非都取反。即Q=1,Q非=0,T=1时,时钟信号来临,Q变成0,Q非变成1

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?