文章目录

前言

Cortex-M3和 Cortex-M3处理器都是基于ARMv7-M架构。

一、编程模型

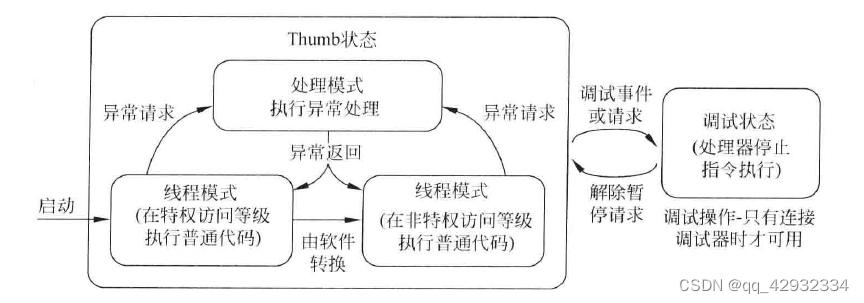

1.1 操作模式和状态

- 操作状态分为 调试状态、Thumb状态(处理器在执行程序代码)

- 操作模式分为 处理模式(执行中断服务程序ISR等异常处理)、线程模式

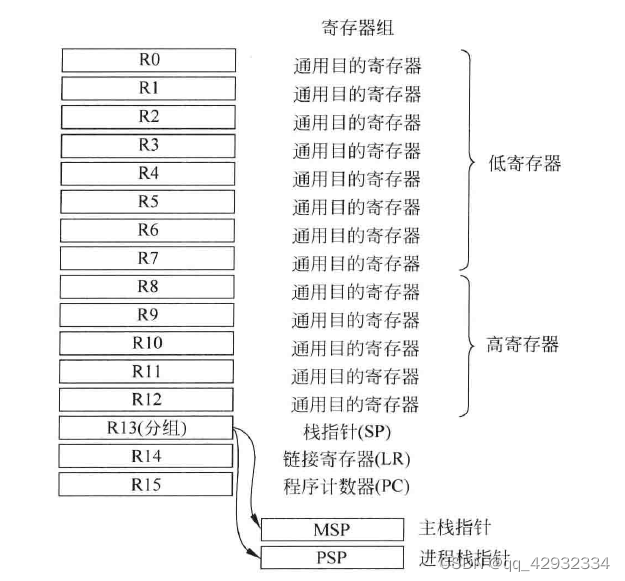

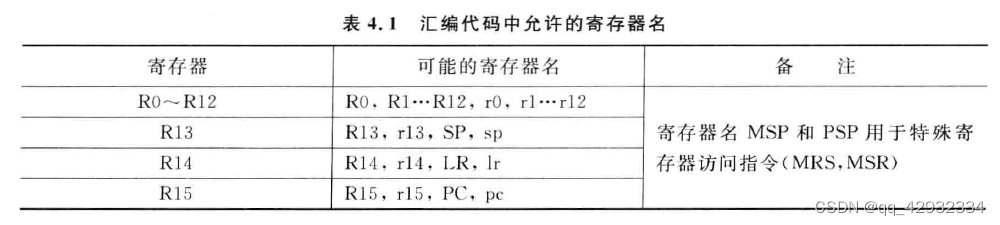

1.2 寄存器

Cortex-M3和 Cortex-M3处理器有16个寄存器组,其中13个32bit通用目的寄存器,3个有特殊用途。

- R13:可通过PUSH和POP操作实现栈存储的访问,最低2bit 总为0,写无效。物理上存在两个栈指针:主栈指针(MSP)和进程栈指针(PSP,仅用于线程模式,一般嵌入式OS才会使用PSP)

- R14:用于函数或子程序调用时返回地址的保存。

- R15:读操作返回当前地址加4,写PC会引起跳转操作。

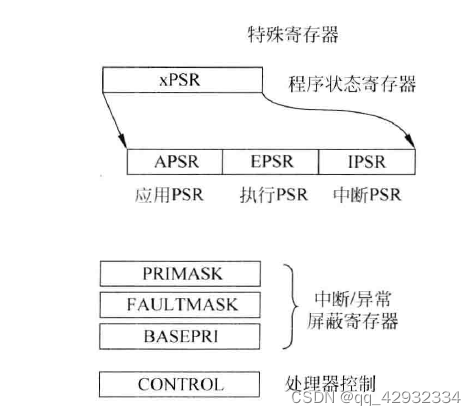

1.3 特殊寄存器

处理寄存器组中的寄存器外,处理器还存在多个特殊寄存器。特殊寄存器未经过存储器映射,可以使用MSR MRS等特殊寄存器访问指令来进行访问。

MRS<reg>,<special_reg> ; 将特殊寄存器读入寄存器

MSR<special_reg>,<reg> ; 写入特殊寄存器

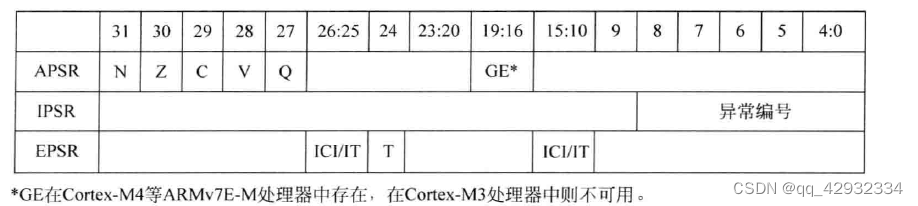

- 程序状态寄存器:包含应用PSR(APSR)、执行PSR(EPSR)、中断PSR(IPSR)

- PRIMASK FAULTMASK BASEPRI寄存器: 都用于异常或中断的屏蔽。

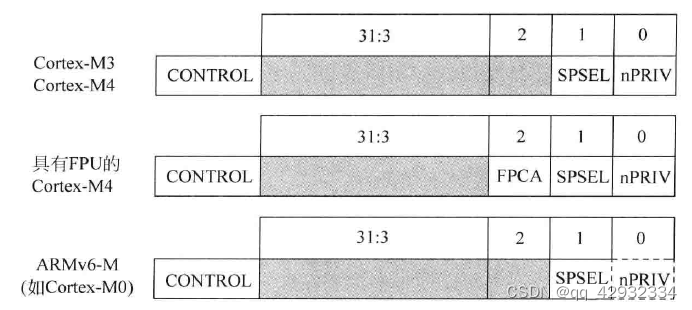

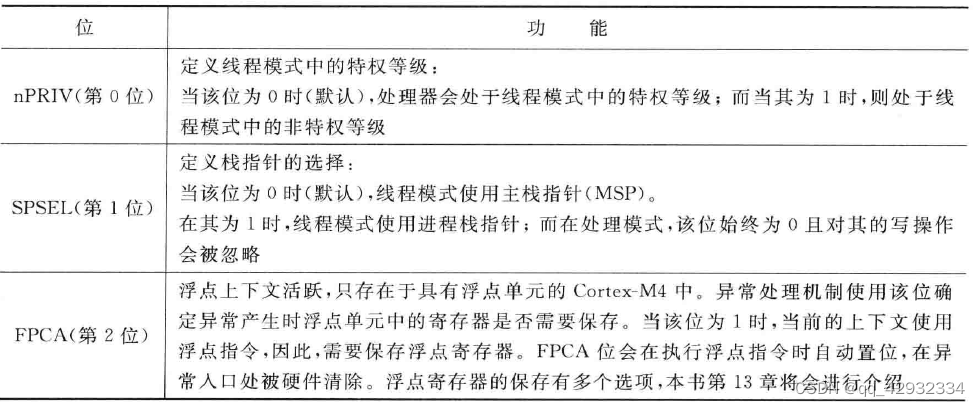

- CONTROL 寄存器:定义栈指针的选择(主栈/进程栈)和线程模式的访问等级(特权/非特权),复位后寄存器值默认为0,即默认处于线程模式、具有特殊权限,运行主栈指针。可以使用C语言访问CONTROL寄存器,使用符合CMSIS的设备驱动库提供的以下函数:

x = _get_CONTROL(); _set_CONTROL(x);

- 浮点寄存器: Cortex-M4具有可选的浮点单元,不支持双精度浮点运算,但传输双精度数据时仍可使用浮点指令。

二、应用程序状态寄存器

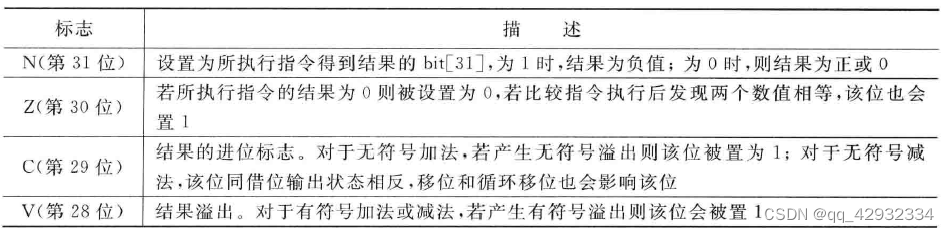

APSR中包含以下机组状态标准:整数运算的状态标准(N-Z-C-V),饱和运算的状态标志位(Q),SIMD运算的状态标注位(GE)

2.1 整数状态标志

2.2 Q状态标志

Q表示饱和算数运算或饱和调整运算过程中产生了饱和。该位被设置后,以及软件写APSR清除Q位之前,它都一直保持置位状态,饱和运算/调整运算不会清除该位。

2.3 GE位

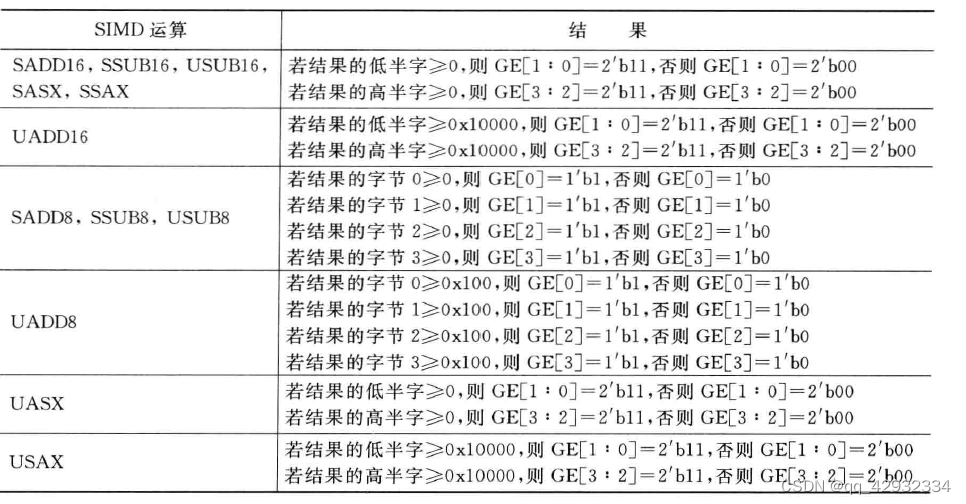

“大于等于”(GE)位域在APSR中占用4位。许多SIMD指令都会更新该标志位。

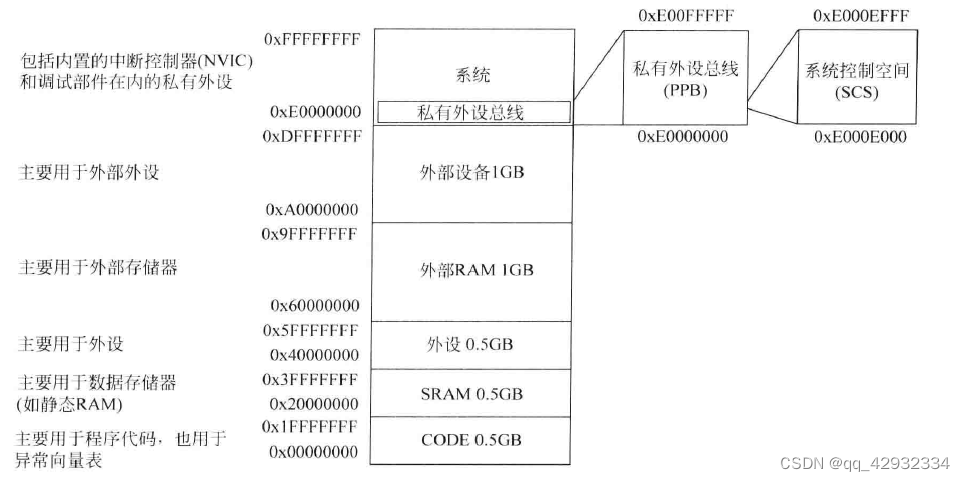

3. 存储器系统

处理器接口为通用总线接口,可通过不同存储器控制器连接至不同类型和大小的存储器。Cortex-M3和 Cortex-M3处理器具有以下存储器系统特性:

- 4GB线性地址空间(32bit)

- 架构定义的存储器映射(划分多个区域)

- 支持大端和小端

- 位段方位(可选)

- 写缓存

- 存储器保护单元(MPU)

- 非对齐传输支持

2.1 存储器映射

4GB的地址控制被划分为多个存储器区域,主要用于

- 程序代码访问(CODE区域)

- 数据访问(如SRAM区域)

- 外设

- 处理器的内部控制和调试部件(如私有外设总线)

2.2 栈存储

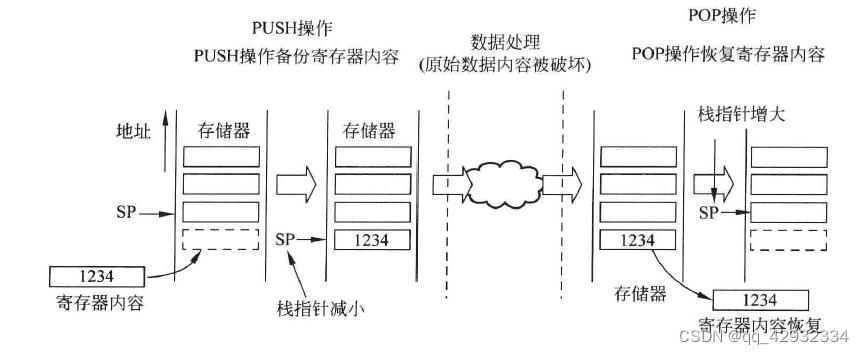

Cortex-M处理器在运行时需要栈存储和栈指针(R13),存储器的一部分可被用作后进先出的数据存储缓冲。

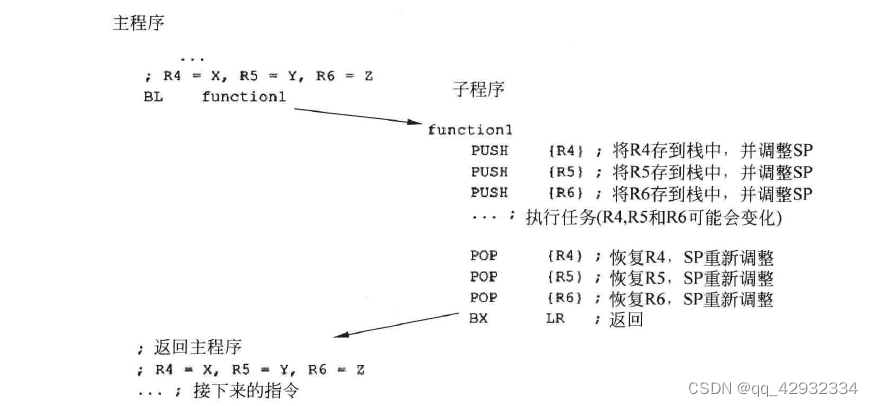

PUSH和POP的常见用法为,在执行函数或子程序调用时保存寄存器组中的内容。在函数开始时,有些寄存器的内容可以通过PUSH指令保存在栈中,而后在函数调用结束时通过POP指令恢复为它们的初始值。

2.3 存储器保护单元(MPU)

MPU在Coretex-M3和Coretex-M4处理器中是可选的,可编程的。

3 异常和中断

3.1 什么是异常

异常是会改变程序流的事件,当其产生时,处理器会暂停正在执行的任务,转而执行一段被称作异常处理的程序。在异常处理结束后,处理器会继续正常的程序执行。中断就是一种异常,也被称作为中断服务程序(ISR)。

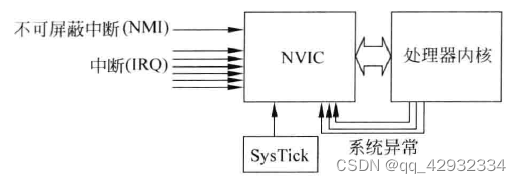

Coretex-M处理器有多个异常源:NVIC处理异常、处理器本身

3.2 嵌套向量中断控制器(NVIC)

NVIC有以下特点:

- 灵活的中断和异常管理:每个中断(NMI除外)都可以呗使能或者禁止,NVIC输入信号高有效。

- 嵌套向量/中断支持:每个异常都有优先级(可编程/固定),正在执行的异常任务可被高优先级的异常打断,抢占去执行新异常。

- 向量化的异常/中断入口:异常发生时,处理器需要确定对应异常处理入口的位置。Cortex-M处理器会从存储器的向量表中自动定位异常处理的入口。

- 中断屏蔽:利用PRIMASK寄存器,可禁止除HardFault和NMI外的所有异常,BASEPRI寄存器来选择屏蔽低于特定优先级的异常和中断。

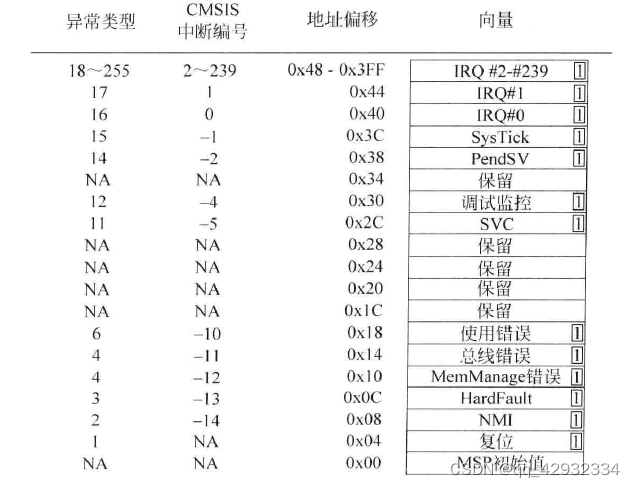

3.2 向量表

确定异常处理的起始地址,处理器利用了一种向量表机制。向量表微系统存储器内的子数据数组,每个元素都代表一个异常类型的起始地址。向量表可重新定位,重定位由NVIC中向量表编译寄存器(VTOR)的可编程寄存器控制。复位后,VTOR默认为0,向量表则位于地址0x0。

由于Cortex-M处理器只支持Thumb指令,因此,所有异常向量的最低位都应该为1。

4 复位和复位流程

控制器的复位类型有:上电复位,系统复位,处理器复位。

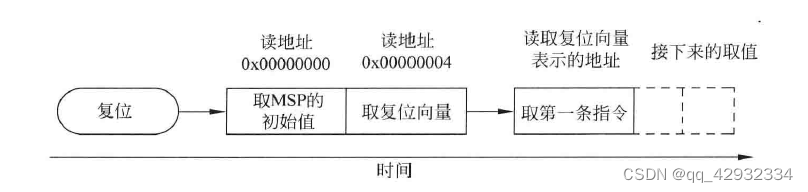

在复位后以及处理器开始执行程序前,Cortext-M处理器会从存储器中读出头两个字。如下图所示。向量表位于存储器的开头,它的头两个字为MSP的初始值,以及代表复位处理起始地址的复位向量,处理器读出这个两个字后,就会将这些数值赋给MSP和程序计数器(PC)。

MSP的设置也有必要,这是因为在复位的很短时间内有产生NMI或HardFault的可能,在异常处理前将处理器状态压栈时需要栈存储和MSP。

注意:对于多数C开发环境,进入main()前更新MSP的数值。通过这两次对栈的设置,具有外部存储器的微控制器可以将外部存储器用作栈。

2769

2769

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?