工程创建步骤和仿真设置步骤参考第一篇笔记:https://blog.csdn.net/qq_43110479/article/details/115472241

my3_8.v 代码

module my3_8(a,b,c,out);

input a,b,c;

output reg [7:0]out;

always@(a,b,c)begin

case({a,b,c})

3'b000:out=8'b0000_0001;

3'b001:out=8'b0000_0010;

3'b010:out=8'b0000_0100;

3'b011:out=8'b0000_1000;

3'b100:out=8'b0001_0000;

3'b101:out=8'b0010_0000;

3'b110:out=8'b0100_0000;

3'b111:out=8'b1000_0000;

endcase

end

endmodule

注意只要是在always@ 语句赋值的变量,一定要定义成reg型!

若是output reg [7:0]out;这一行不采用reg型,则报错。

my3_8_testbench.v 代码

`timescale 1ns/1ps

module my3_8_tb;

reg signal_a;

reg signal_b;

reg signal_c;

wire [7:0]led;

my3_8 my3_8_1(

.a(signal_a),

.b(signal_b),

.c(signal_c),

.out(led)

);

initial begin

signal_a = 0; signal_b = 0;signal_c = 0;#100;

signal_a = 0; signal_b = 0;signal_c = 1;#100;

signal_a = 0; signal_b = 1;signal_c = 0;#100;

signal_a = 0; signal_b = 1;signal_c = 1;#100;

signal_a = 1; signal_b = 0;signal_c = 0;#100;

signal_a = 1; signal_b = 0;signal_c = 1;#100;

signal_a = 1; signal_b = 1;signal_c = 0;#100;

signal_a = 1; signal_b = 1;signal_c = 1;#100;

end

endmodule

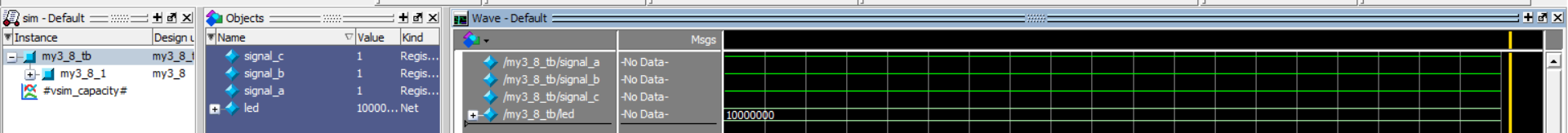

运行仿真

编译后运行仿真发现,没有波形。

查看ModelSim ALTERA的tanscript发现,‘out’ port不能连接。

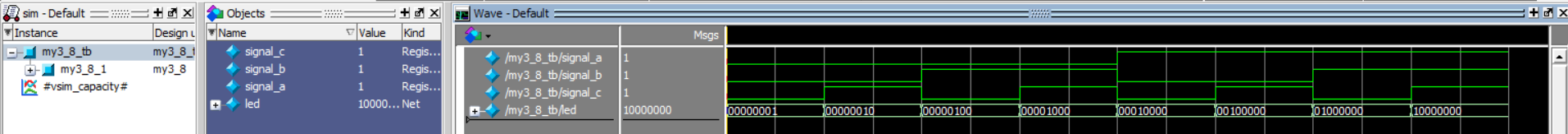

更改代码:

my3_8.v:

output reg [7:0]out; -->output reg [7:0] out;

my3_8_testbench.v:

wire [7:0]led; --> wire [7:0] led;

1359

1359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?