FPGA开发流程

- 设计定义

- 设计输入

- 分析和综合

- 功能仿真(理想仿真,实际存在逻辑延迟等)

modelsim-altera软件 - 布局布线

- 时序仿真(时序约束,保证时序要求)

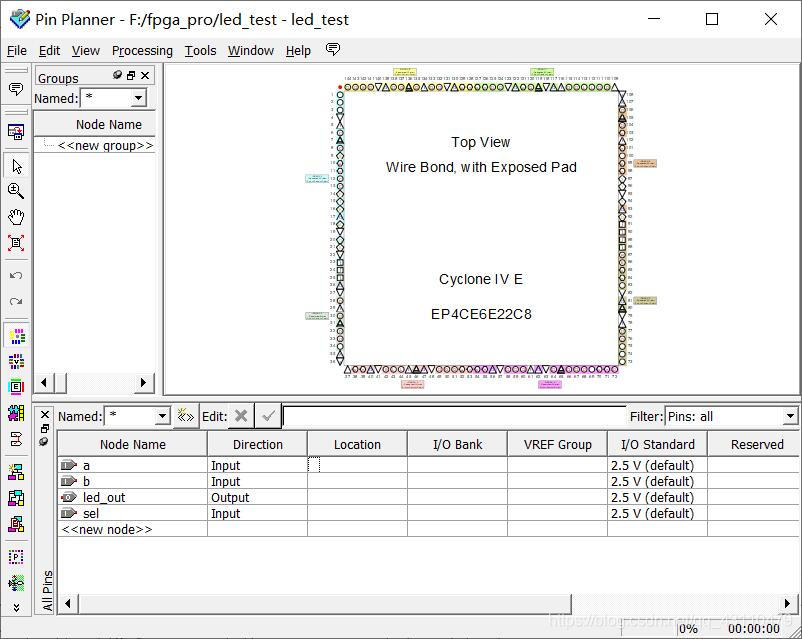

modelsim-altera软件 - IO分配以及配置文件的生成

- 配置(烧写FPGA)

- 在线调试

二选一案例

1、设计定义:

两个按键输入I/O(a,b)

输入按键按下时,LED灯与a端口状态保持一致;否则,LED灯与b端口状态保持一致

2、设计输入:

module led_test(a,b,sel,led_out);

input a,b;//input port a and b

input sel;//input port sel

output led_out;//output port led_out

assign key_out = (sel == 0)? a:b; //if sel logic low, key_out<=a ,else b

endmodule

3、仿真综合

4、功能仿真

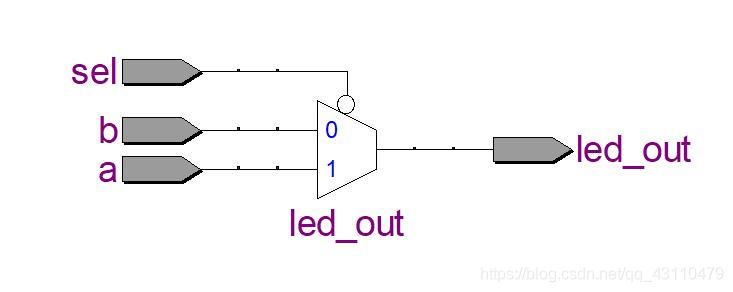

rtl视图:

编写testbench文件

`timescale 1ns/1ps

// #100.1 //delay 1ns*100, accuracy 1ps 0.1ns = 1ps

module led_test_tb;

//激励

reg signal_a;

reg signal_b;

reg signal_c;

//待检测信号定义,连接到待测试模块输出

wire led;

//例化

led_test led_test_0(

.a(signal_a),

.b(signal_b),

.sel(signal_c),

.led_out(led)

);

//产生激励

initial begin

signal_a = 0; signal_b = 0;signal_c = 0;#100;

signal_a = 0; signal_b = 0;signal_c = 1;#100;

signal_a = 0; signal_b = 1;signal_c = 0;#100;

signal_a = 0; signal_b = 1;signal_c = 1;#100;

signal_a = 1; signal_b = 0;signal_c = 0;#100;

signal_a = 1; signal_b = 0;signal_c = 1;#100;

signal_a = 1; signal_b = 1;signal_c = 0;#100;

signal_a = 1; signal_b = 1;signal_c = 1;#100;

$stop;

end

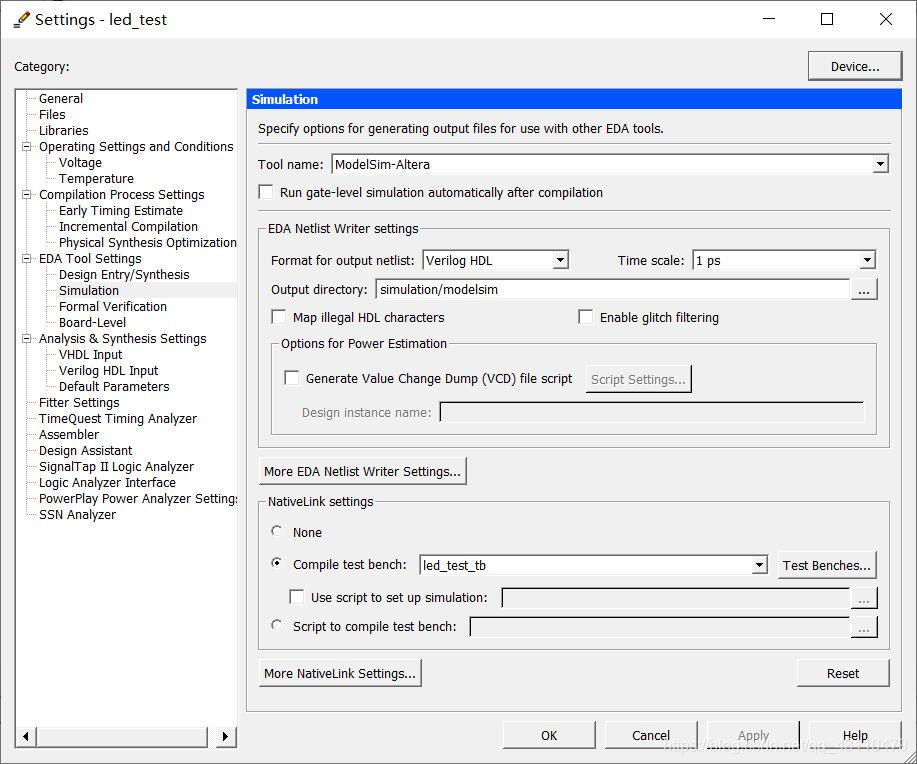

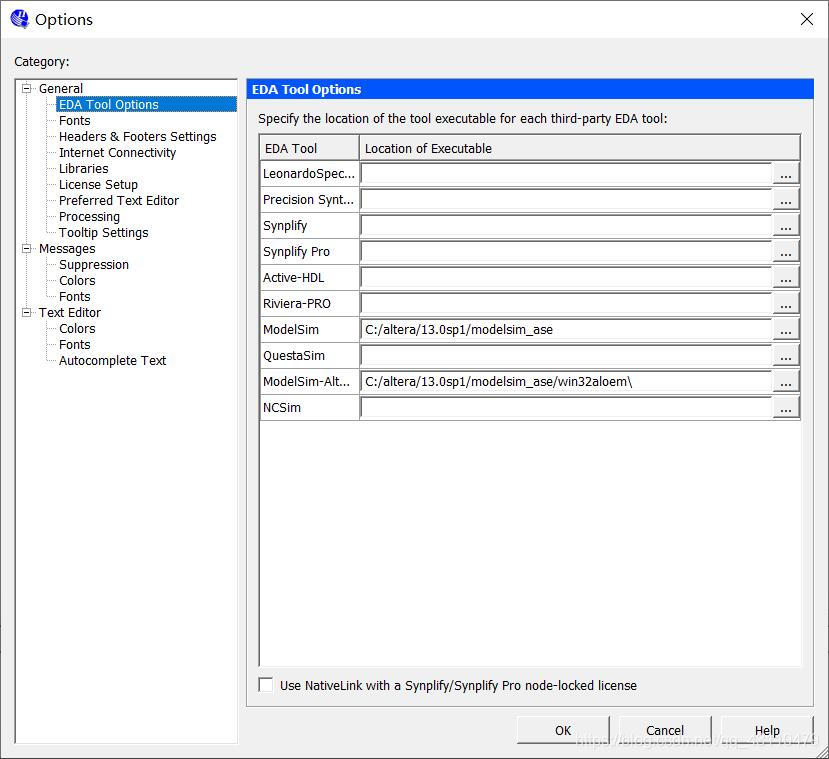

设置好仿真环境以及联络testbench文件

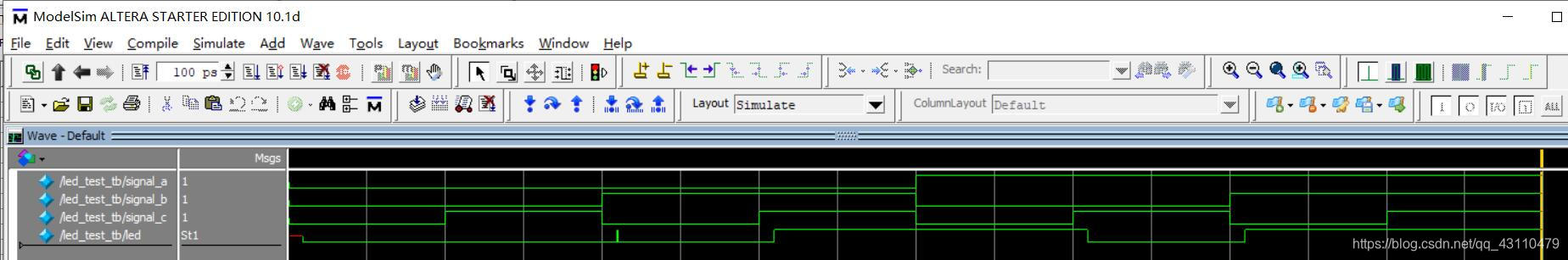

进行仿真

5、布局布线

直接编译

6、后仿真

7、引脚分配

8、配置烧写

9、在线调试

本文详细介绍了FPGA开发的整个流程,包括设计定义、输入、分析综合、功能仿真、布局布线、时序仿真、引脚分配、配置烧写以及在线调试。通过一个具体的案例展示了如何实现按键输入控制LED显示的功能,并使用modelsim-altera软件进行仿真验证。该文对于理解和实践FPGA设计具有指导意义。

本文详细介绍了FPGA开发的整个流程,包括设计定义、输入、分析综合、功能仿真、布局布线、时序仿真、引脚分配、配置烧写以及在线调试。通过一个具体的案例展示了如何实现按键输入控制LED显示的功能,并使用modelsim-altera软件进行仿真验证。该文对于理解和实践FPGA设计具有指导意义。

2709

2709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?