Verilog编写2FSK第③步信号的调制

上一篇编写了2FSK调制信号的程序,本节编写信号调制的子程序

- 2FSK二进制频移键控,FSK 是用不同频率的载波来传递数字消息的。

- 例如:f1=sin2πw f2=sin4πw 传输f1时代表’0’传输f2时是’1’

module modulation(clk,DDSin,DA_Data,DA_Data2,DDS_out);//定义模块和端口

input clk;//输入的时钟

input DDSin;//需要调制的信号

input wire [10:0]DA_Data;//输入的载波=‘0’

input wire [10:0]DA_Data2;//输入的载波=‘1’

output wire[10:0]DDS_out;//输出的调制完成的信号

reg [10:0]canshu;//模块定义内部寄存器

always @(posedge clk)//每当时钟上升沿时触发

begin

if(DDSin==0)//如果输入的基带信号为0则输出位载波1

canshu<=DA_Data;

else //如果输入的基带信号为1则输出位载波2

canshu<=DA_Data2;

end

assign DDS_out=canshu;//

endmodule

- 子模块编写完成后编写顶层文件

module DDS_top(

input clk,

output wire [10:0]DA_Data,

output wire [10:0]DA_Data2,

output wire [10:0]DDS_out,

input canshu

);

DDS DDS(//例化上节的载波生成的模块

.clk(clk),

.DA_Data(DA_Data),

.DA_Data2(DA_Data2)

);

modulation modulation(

.clk(clk),

.DDSin(canshu),

.DA_Data(DA_Data),

.DA_Data2(DA_Data2),

.DDS_out(DDS_out)

);

endmodule

- 最后编写tb仿真文件

`timescale 1ms/1ms

module DDS_tb;//因为是仿真文件不用进行端口设置,该文件里的参数都会在wave中显示

wire [10:0]DA_Data;

wire [10:0]DA_Data2;

wire [10:0]DDS_out;

reg clk;

reg canshu=0;

DDS_top DDS_top(

.clk(clk),

.DA_Data(DA_Data),

.DA_Data2(DA_Data2),

.DDS_out(DDS_out),

.canshu(canshu)

);

initial clk=1;

always #5 clk=~clk;

endmodule

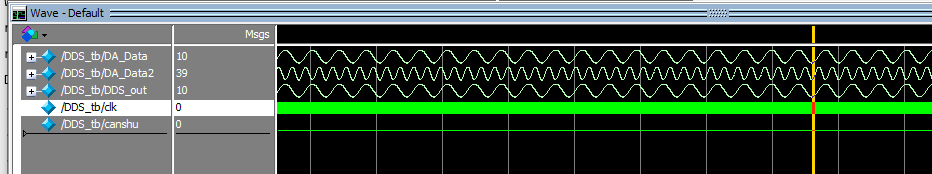

- 仿真运行文件,根据上一节将参数操作后可直观的查看波形

当基带为0时即canshu<=0;改变canshu的值为‘1’或者‘0’可观测到DDS_out即调制信号会变化

【FPGA】使用Verilog编程通过ModelSim实现2FSK调制解调仿真②(调用.mif生成2FSK载波波形——DDS)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?