zcu106点灯

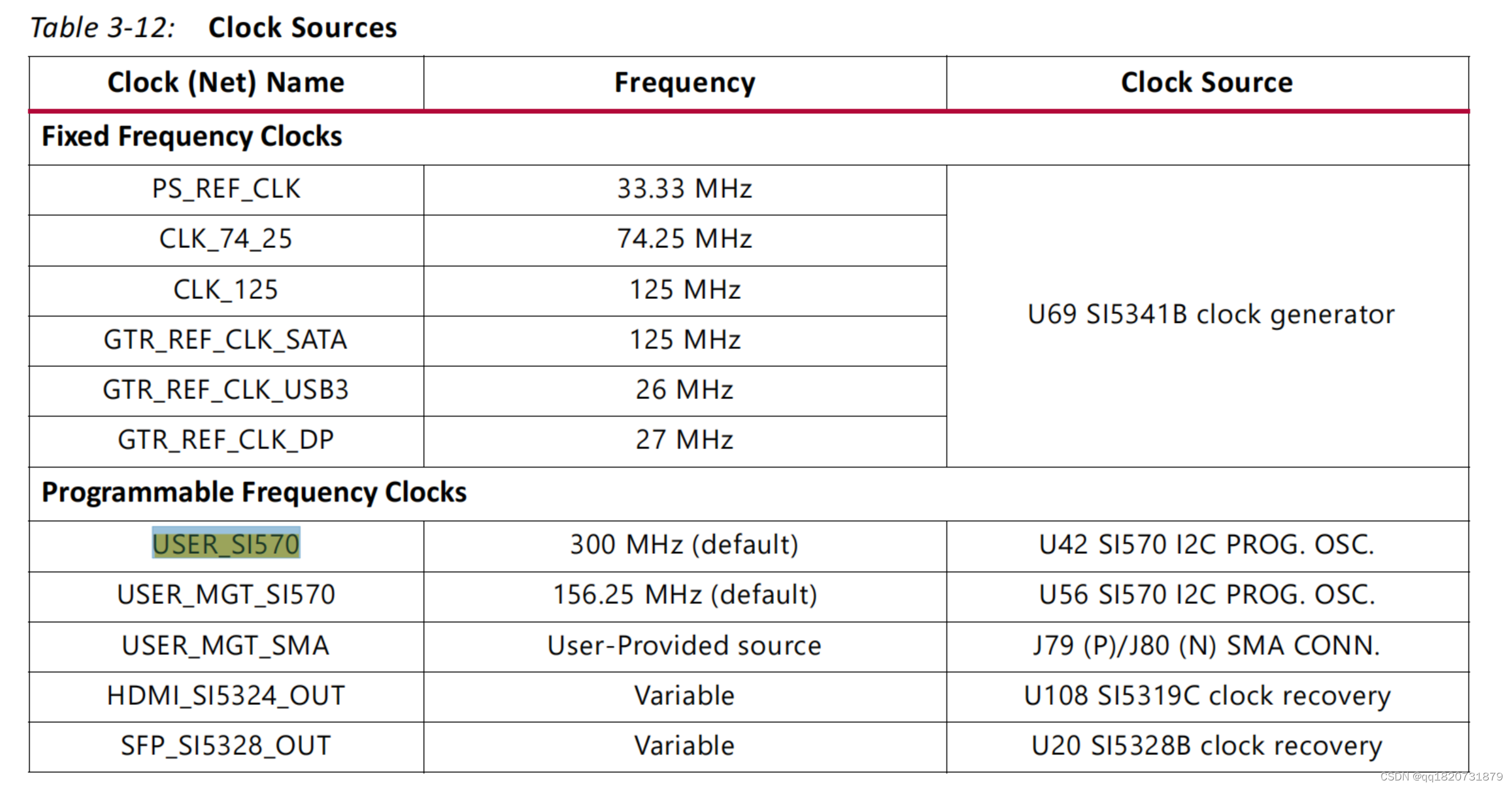

1、时钟选择

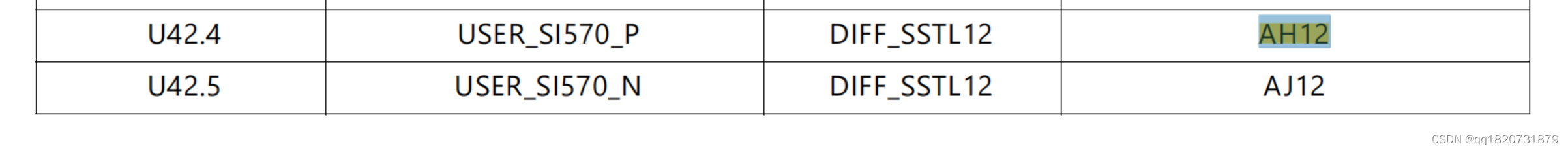

①、这里选择USER_SI570这个默认差分时钟300M时钟

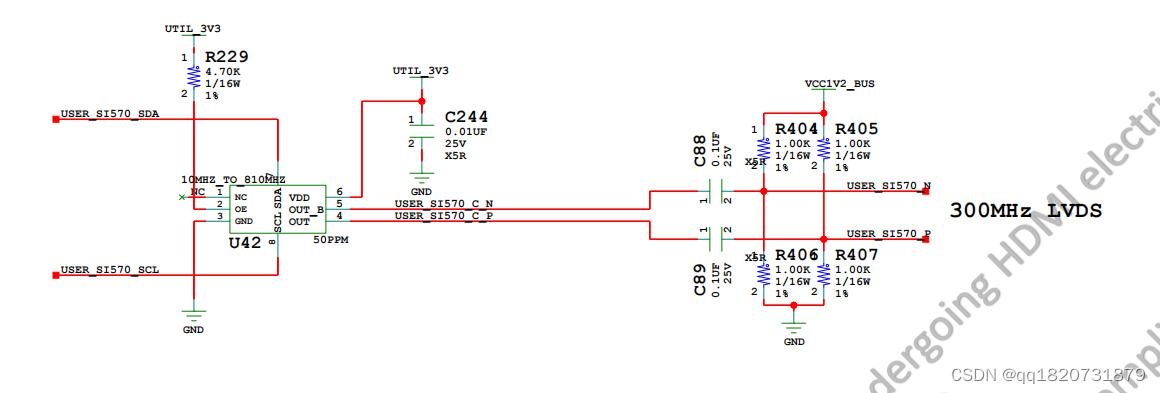

②、查看原理图

2、verilog代码

module led_twinkle(

input clk_n, //系统时钟

input clk_p, //系统时钟

input sys_rst_n, //系统复位,底电平有效

output [1:0] led //低电平复位有效

);

wire clk;

//使用IBUFDS将差分时钟转换未单端时钟

IBUFGDS i_ibufgds_adc_0

(

.I (clk_p),

.IB (clk_n),

.O (clk)

);

//reg define

reg [31:0] cnt;

//对计数器的值进行判断,以输出LED的状态

assign led = (cnt < 32'd15000_0000) ? 2'b01 : 2'b10;

//计数器在0~5000_000之间进行计数

always @(posedge clk or negedge sys_rst_n) begin

if(sys_rst_n)

cnt <= 32'd0;

else if(cnt < 32'd30000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 32'd0;

end

endmodule

主要是差分时钟怎么切换为单端时钟

//使用IBUFDS将差分时钟转换未单端时钟

IBUFGDS i_ibufgds_adc_0

(

.I (clk_p),

.IB (clk_n),

.O (clk)

);

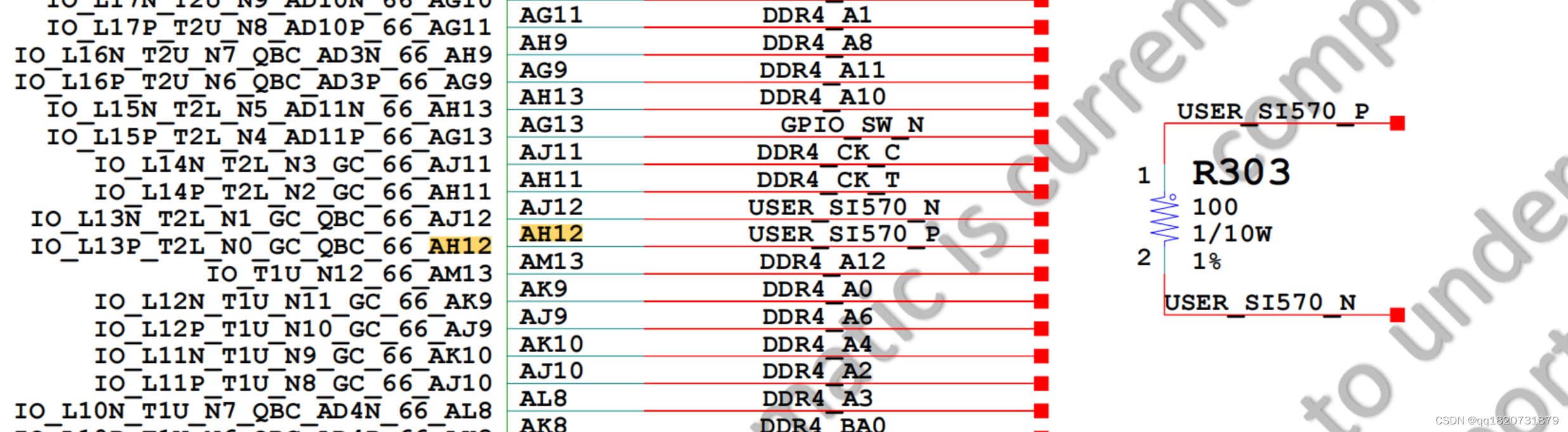

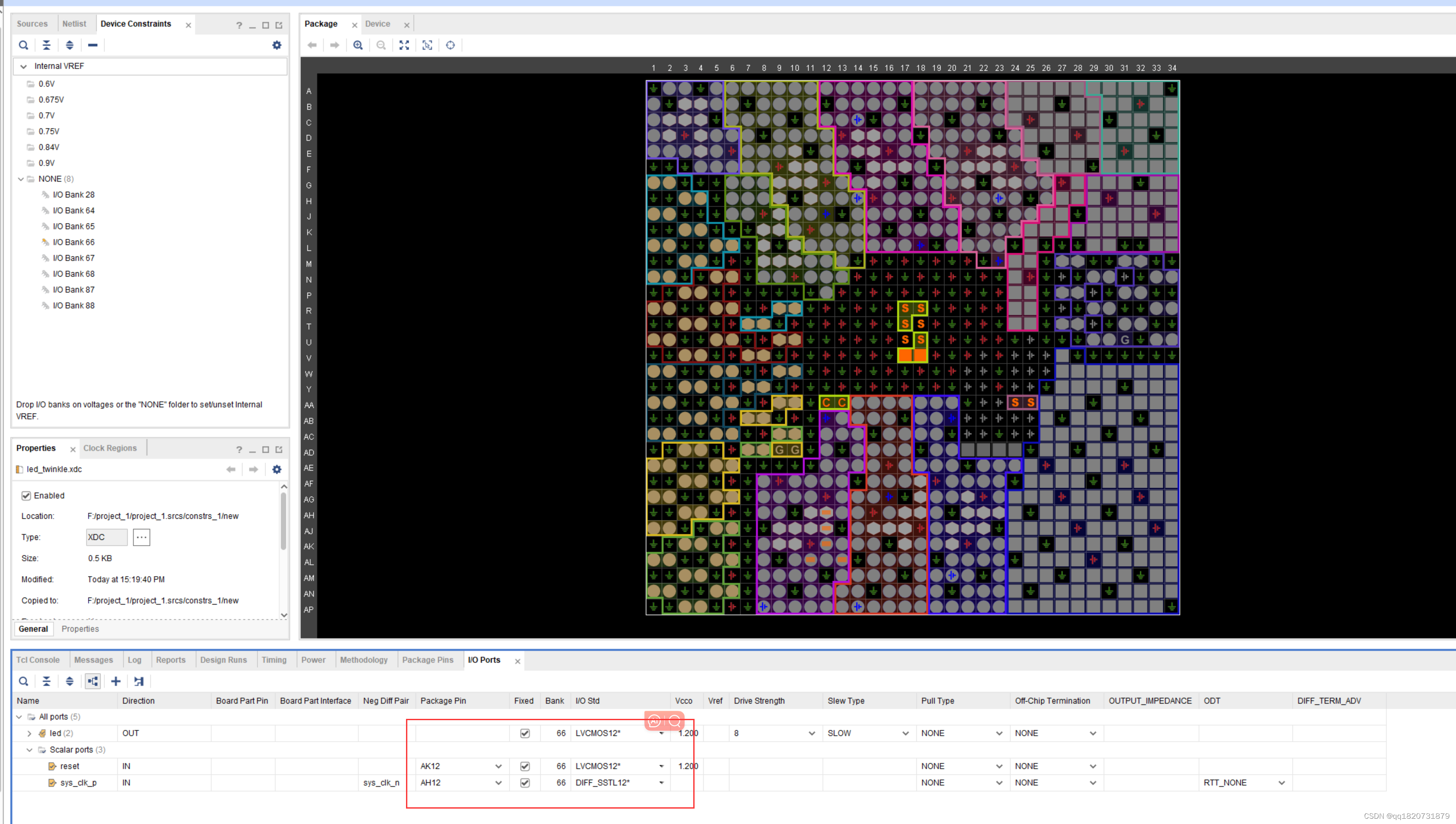

3、管脚配置

这里管脚电压要根据用户指南去查看具体管脚电压配置

4、jtag烧录,查看现象

两个LED循环闪烁,按下复位按键之后暂停

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?