一、实验学时

4学时

二、实验目的

掌握节拍脉冲发生器的设计方法,理解节拍脉冲发生器的工作原理。

三、实验环境

硬件资源:PC机或笔记本电脑,康芯实验箱;软件资源:Quartus17.1设计平台。

四、实验原理

计算机之所以能够按照人们事先规定的顺序进行一系列的操作或运算,就是因为它的控制部分能够按一定的先后顺序正确地发出一系列相应的控制信号。这就要求计算机必须有时序电路,控制信号就是根据时序信号产生的。本实验说明时序电路中节拍脉冲发生器的工作原理。

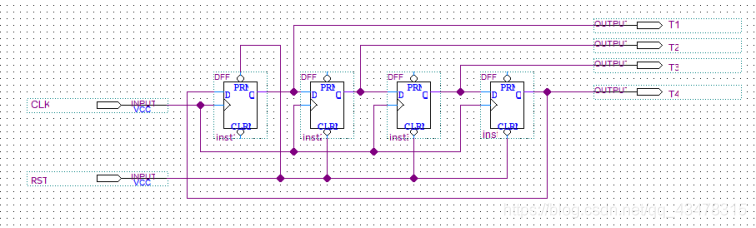

某机器的连续节拍发生电路可由4个D触发器组成,如图3.1所示,该电路可产生4个等间隔的时序节拍信号T1–T4,其中CLK为时钟信号,当RST为低电平时,T1输出为“1”,而T2、T3、T4输出为“0”;当RST由低电平变为高电平后,T1–T4将在CLK的输入脉冲作用下,周期性地轮流输出正脉冲(脉冲宽度为一个时钟周期)。

(1)实验任务1:连续节拍发生电路设计

T1–T4以及CLK、RST的工作波形如图3.2所示。示例顶层文件是STEP1.bdf。硬件电路见图3.1所示。

图3.1 节拍脉冲发生器电路

(2)实验任务2:单步节拍发生电路设计

用单步节拍发生电路可以对微程序进行单步运行调试。如图3.3所示,该电路每当STEP出现一个正脉冲后,仅输出一组T1、T2、T3、T4节拍信号,直到STEP出现下一个正脉冲。

示例顶层文件是STEP2.bdf

本次实验旨在通过Verilog语言设计不同类型的节拍脉冲发生器,包括连续节拍、单步节拍及单步/连续节拍发生电路。实验中,使用4个D触发器构建节拍脉冲发生器,根据时钟信号CLK和复位信号RST,产生T1-T4四个时序节拍信号。在单步模式下,每个STEP脉冲只产生一组节拍信号。所有设计经过Quartus17.1仿真验证,并在康芯实验箱上进行了实物验证。

本次实验旨在通过Verilog语言设计不同类型的节拍脉冲发生器,包括连续节拍、单步节拍及单步/连续节拍发生电路。实验中,使用4个D触发器构建节拍脉冲发生器,根据时钟信号CLK和复位信号RST,产生T1-T4四个时序节拍信号。在单步模式下,每个STEP脉冲只产生一组节拍信号。所有设计经过Quartus17.1仿真验证,并在康芯实验箱上进行了实物验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5034

5034

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?