目录

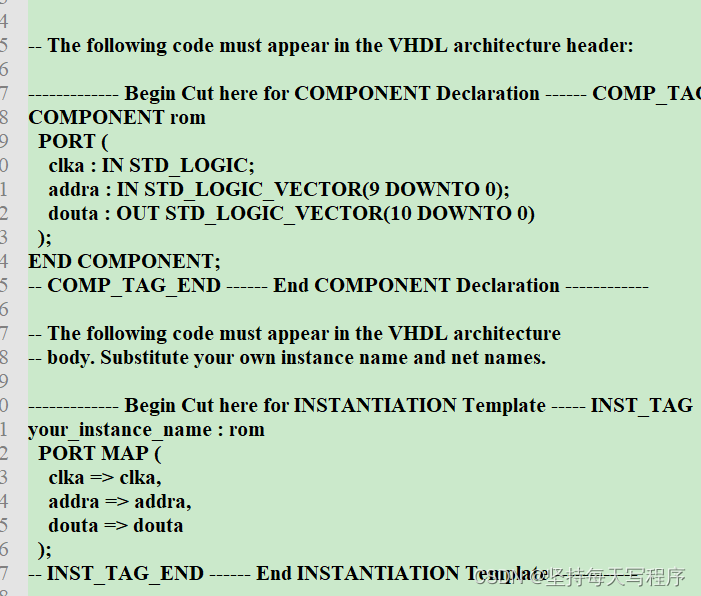

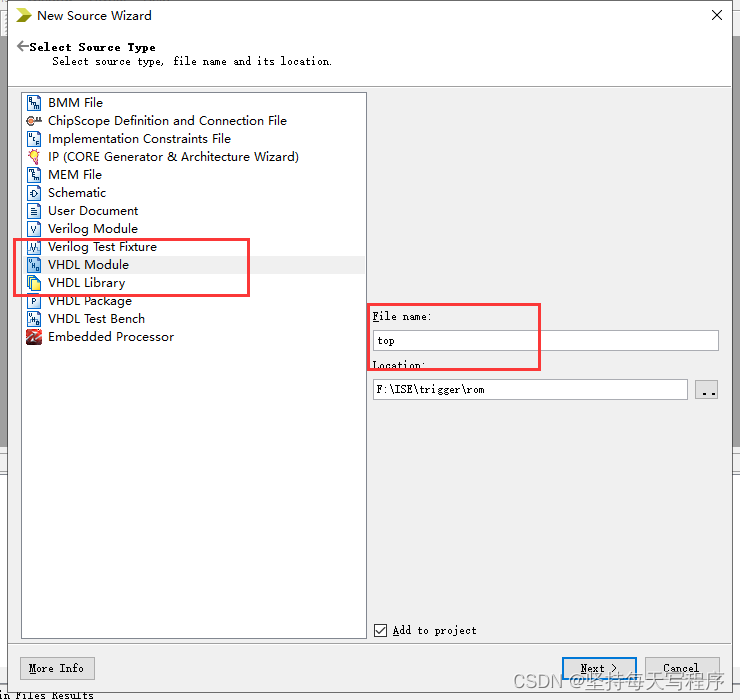

2.编写顶层文件或者激励文件:(一定一定点击下面这个例化模板 去对ip核进行例化)

工程下载链接:https://download.csdn.net/download/qq_43811597/86488775

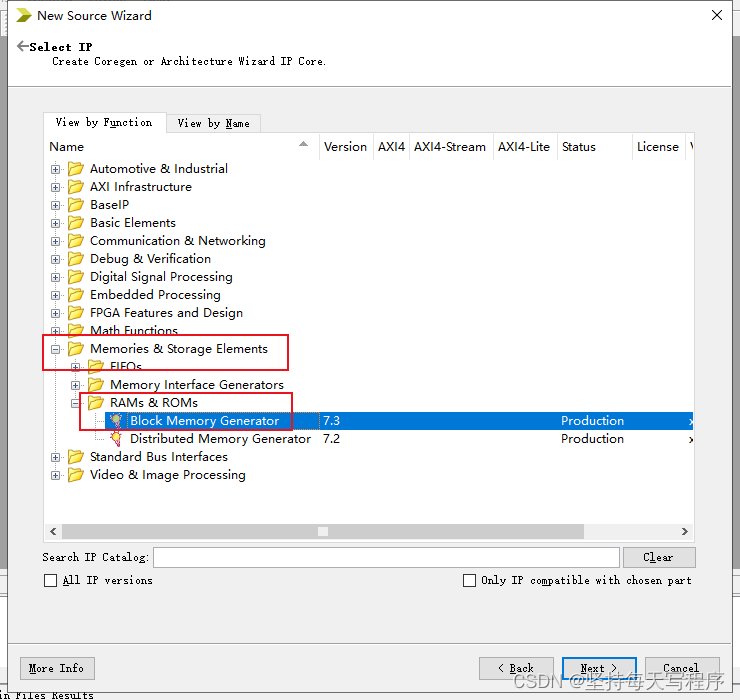

1.新建工程之后 建一个ip核文件:

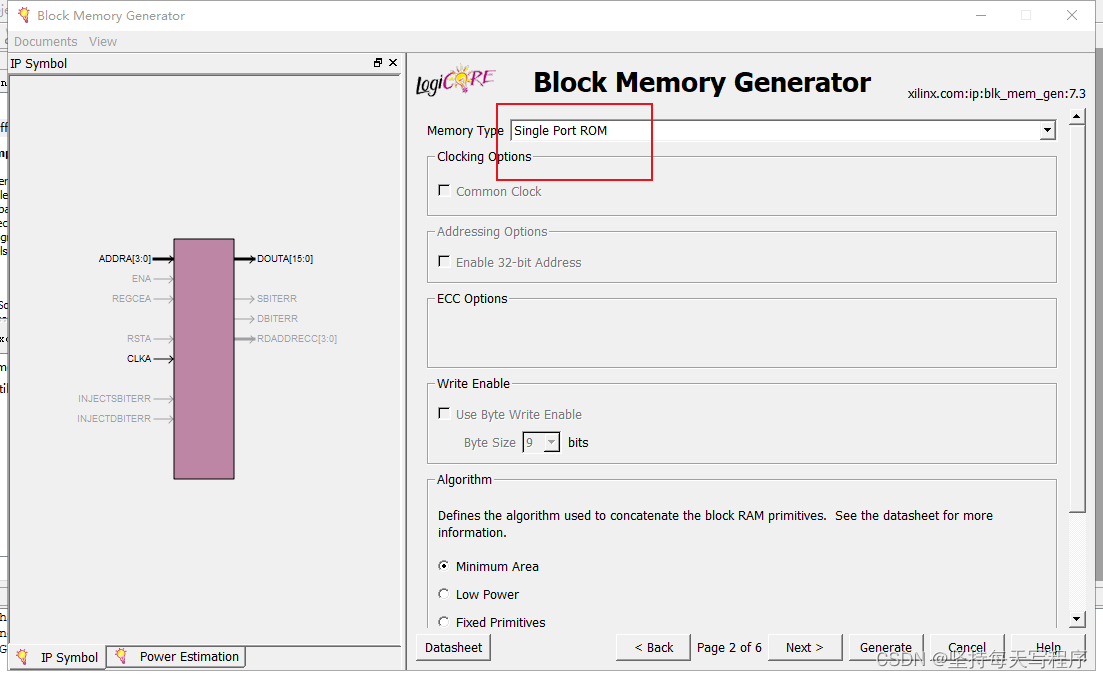

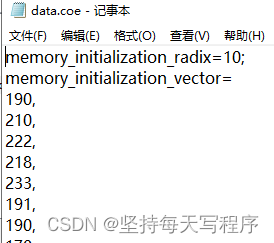

根据所存数据的最大值来设置数据位宽(但位宽不知道需不需要换算,还是说将最大的那个数设为位宽)

根据所存数据个数来设置数据深度(他这里的深度好像不用根据个数去换算,直接就是深度=数据个数)

我本来以为我存700个数据 那么深度就是10,结果一直报错 不能生成ip核

就是这个加载coe这块会变红,还有就是一直报错:the memory initialization vector can contain between 1 to write depth A number of entires.

one or more of the parameters are invalid. please correct and try again.

然后我看到深度那个范围很大,就把深度直接改成数据个数了,没有错误出现,但是宽度需不需要改 暂时不确定

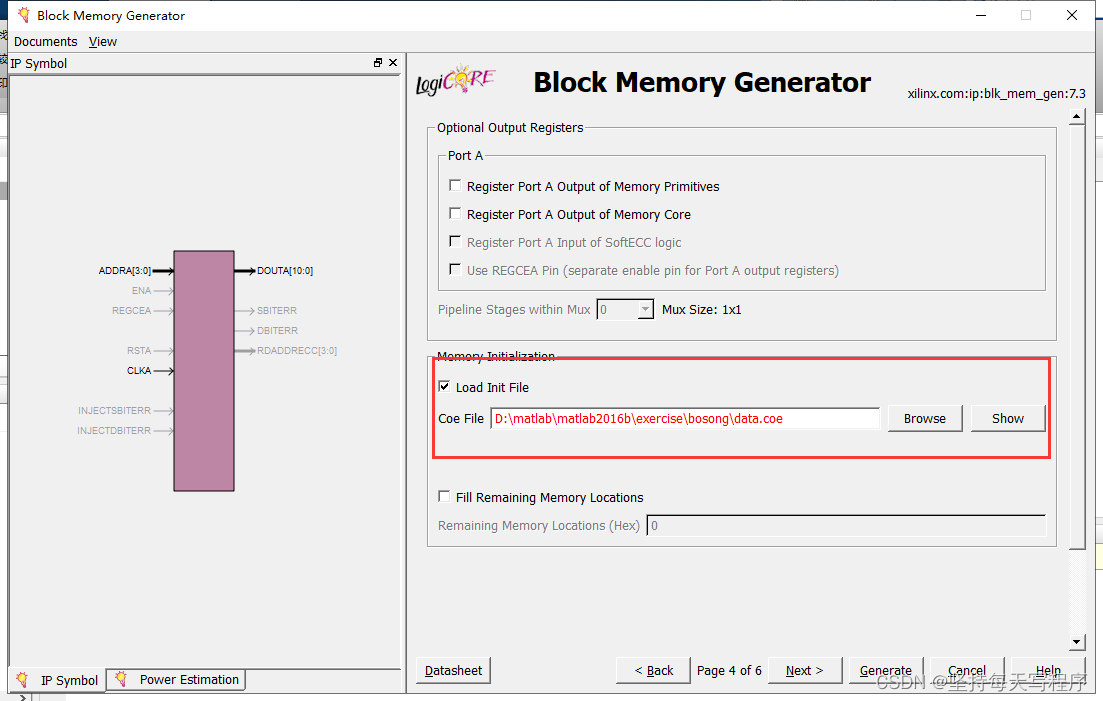

在这里是将matlab产生的数据导入到rom当中(放coe文件的路径不能有中文,并且xilinx系列的rom放coe文件,altera系列放mif文件),可以点击show看是否coe文件有效

matlab生成数据步骤链接:http://t.csdn.cn/OvDPP

2.编写顶层文件或者激励文件:(一定一定点击下面这个例化模板 去对ip核进行例化)

在ram.vho 点开是一个.vho的文件,里面就有你建的ip核的元件声明和例化(ip核的名字跟顶层文件或者其他的测试或者其他模块名字不要重!!!我找了一周的错)

这里可以先建立一个top文件,对rom进行例化,以及地址数据的产生

顶层代码如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity top is

PORT (

clk : IN STD_LOGIC;

rst_n : IN STD_LOGIC;

dout : OUT STD_LOGIC_VECTOR(10 DOWNTO 0)

);

end top;

architecture Behavioral of top is

COMPONENT rom

PORT (

clka : IN STD_LOGIC;

addra : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

douta : OUT STD_LOGIC_VECTOR(10 DOWNTO 0)

);

END COMPONENT;

signal addr : STD_LOGIC_VECTOR(9 DOWNTO 0):= (others => '0');

begin

u0 : rom

PORT MAP (

clka => clk,

addra => addr,

douta => dout

);

process(clk)

begin

if (rst_n = '1') then

addr <= (others => '0');

elsif (rising_edge(clk)) then

if addr = "1010111100" then

addr <= (others => '0');

else

addr <= addr + '1';

end if;

end if;

end process;

end Behavioral;

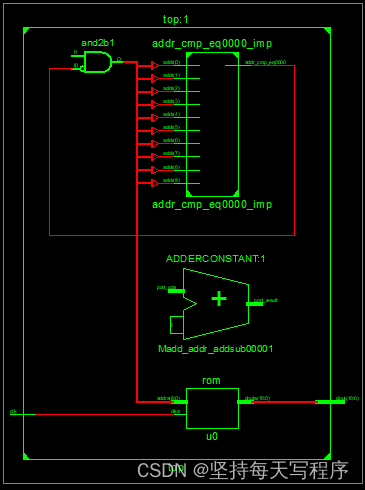

3.查看rtl图:

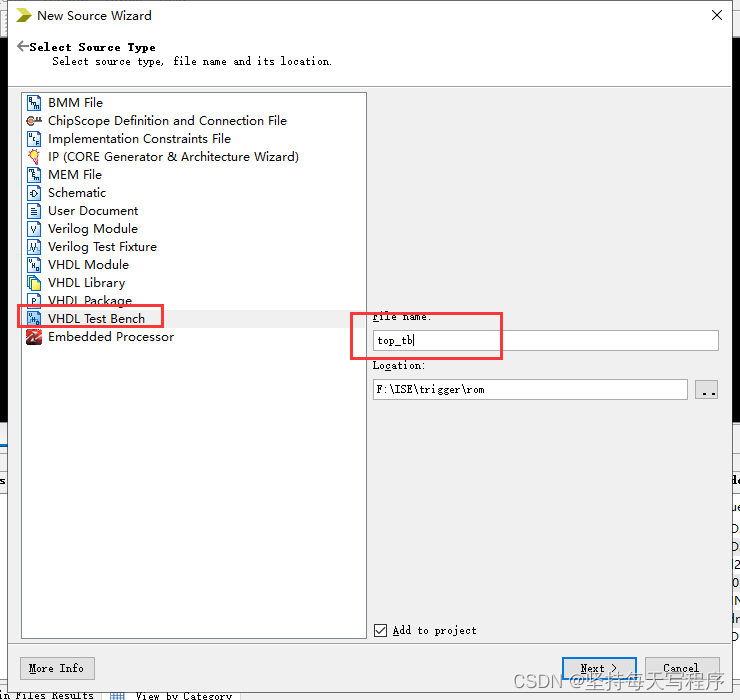

4编写测试文件:

tb文件如下:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY top_tb IS

END top_tb;

ARCHITECTURE behavior OF top_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT top

PORT(

clk : IN std_logic;

rst_n : IN STD_LOGIC;

dout : OUT std_logic_vector(10 downto 0)

);

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

signal rst_n : std_logic := '1';

--Outputs

signal dout : std_logic_vector(10 downto 0);

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: top PORT MAP (

clk => clk,

rst_n => rst_n,

dout => dout

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

rst_n <= '0';

wait for clk_period*10;

-- insert stimulus here

wait;

end process;

END;

5.仿真图:

可以看到最开始的数据和吻合的(注意生成地址数据时,要符合时钟)

可以看出最后的数据也是吻合的

注:另外我们也可以不建立top文件,直接建立tb文件,在tb文件中产生时钟和地址数据即可:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

ENTITY rom_tb IS

END rom_tb;

ARCHITECTURE behavior OF rom_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT rom

PORT(

clka : IN std_logic;

addra : IN std_logic_vector(9 downto 0);

douta : OUT std_logic_vector(10 downto 0)

);

END COMPONENT;

--Inputs

signal clka : std_logic := '0';

signal addra : std_logic_vector(9 downto 0) := (others => '0');

--Outputs

signal douta : std_logic_vector(10 downto 0);

-- Clock period definitions

constant clka_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: rom PORT MAP (

clka => clka,

addra => addra,

douta => douta

);

-- Clock process definitions

clka_process :process

begin

clka <= '0';

wait for clka_period/2;

clka <= '1';

wait for clka_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

addra <= (others => '0');

if addra = "1010111100" then

addra <= (others => '0');

else

addra <= addra + '1';

end if;

wait for 100 ns;

wait for clka_period*10;

-- insert stimulus here

wait;

end process;

END;

1631

1631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?