文章目录

进位计数制

r位进制,各位代表的是权重,小数点前是0、1、2… , 小数点后是-1、-2…

1.任意进制→十进制

2.二进制↔八进制、十六进制

分组,对应着表示出来就行了,位数不够就用0凑上

如果八进制要转换成十六进制,可以先把八进制转换成二进制再转换成十六进制

十六进制加前缀0x,或后缀H

十进制后缀D

二进制 B(binary)

3.十进制→任意进制

原理就是前面的权重,所以说在小数点后面的,是负的多少次方,这个时候用乘法,小数点前面是正的多少次方,用除法就可以把r消掉,得到对应的K。

由此也可以解释,当算小数点前面的时候,高位是在下面的(因为除法是从低位开始得到的);而算小数点后面的时候,高位又在上面了(乘法直接从小数点后第一位开始得到)

不过要注意的是,有些十进制的小数是无法精确转换的,具体分析,毕竟2-1=0.5,2-2=0.25,这样子的话精度肯定是有限的(八进制和十六进制也是类似的),当你乘半天发现小数部分始终不能化为0,那么肯定是没法精确转换(很多时候陷入一种循环)。

拼凑法

66=64+2,这样凑出来,然后在64的位和2的位写上1就行了。(八进制和十六进制就不这样了,不太好算,如果嫌慢可以弄成二进制再转换过去)

4.真值和机器数

正负在前面用0、1表示就行了

小结

字符与字符串

1.英文字符在计算机内的表示

ASCII码

在计算机里,数字、字母、符号还有一些通信符号总共需要有128个字符,也就是27,但是为了刚好凑齐1B来存,在最高位加个0刚好凑齐8位(8 bit)

0 ~ 31、127为控制\通信字符,32 ~ 126为可印刷字符

数字:0 ~ 9 (0011 0000 ~ 0011 1001),前四位 0011

大写字母 26位(010 00001 ~ 010 11010),前三位 010

小写字母 26位(011 00001 ~ 011 11010),前三位011

由此可以看到,大小写字母隔开一定距离是因为让前三位有规律,后五位从1 ~ 26。

只需要知道大写字母、小写字母、数字这些在存放的时候,各自内部是相邻存放的

存放的内容是一串二进制数

2.汉字的表示和编码

区位码:在计算机里一块区域存放汉字(像正方形一样),区位码理解成坐标就行了,(16,01),分别是1个字节(94x94,所以要用28 =128来表示),放在字符串里要读两个地址单元,所以说为了避免读这两个地址单元的时候把它当作控制\通信字符,就分别加个20H(十六进制)来区分,叫做国标码。但是这样做还是有可能和ASCII码相冲突,所以再加80H,叫做汉字机内码

3.字符串

很多语言里,结尾要加个’ \0 '作为结束标志

大端模式:把低位的放在高位

小端模式:把低位的放在低位

小结

奇偶校验码

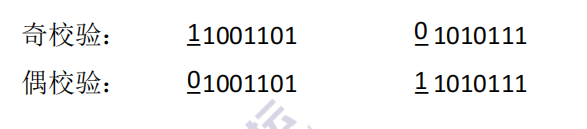

奇校验码:增加一位校验位,使整个校验码的1是奇数个

偶校验码:使1是偶数个

异或(模2加):相同为0,不同为1

0 ⊕ 0 = 0

0 ⊕ 1 = 1

1 ⊕ 1 = 0

奇偶校验是没法检验出偶数个位数出错的情况的(因为出偶数个错误奇偶性是一样的),也不能知道具体哪错了(不能纠错)

小结

海明校验码

设计多个校验位,这样能携带更多信息,也就能通过这些校验位来判断究竟是哪里出了问题

校验位放在1、2、4、8……位上

但是这样也有问题,比如如果S1、S2、S3都错了,得到111,指明是D4出错,但是假如是D1、D2一起出错,那么也会得到相同的结果。也就是说海明校验码只能纠正1位出错的情况,有两位出错的时候没办法知道具体是哪两位。

为了能够检验出是不是1位出问题,增加了一个全校验位,对整体进行偶校验,这样只要偶校验失败就知道是1位出错,纠正即可,如果偶校验成功就重传。

小结

循环冗余校验码(CRC)

1.生成校验码

生成多项式的最高次幂是n,那么校验位就有n位

相对应的,生成码有n位,那么校验位有n-1位(注意生成码和生成多项式之间的区别)

在信息码后面加n位0,然后除生成码,得到的n位余数就是校验位,加到信息码后面就得到了CRC校验码

与除法有区别,模2除只要最高位是1,那么就可以除下来,然后进行模2减(同0异1)

2.检错和纠错

用校验码除生成码得到余数,不是全为0就有错,并且由纠错能力(只要检验码表示的状态比总位数多),但是不是二进制换算成十进制那么得到的(依次进行模2除的方式来计算的)

循环就体现在上图,不够表示的时候就会开始循环,所以这个时候不能准确知道是哪里出错(只能检验)

所以大多数时候是用来进行检验的,并且常用来检验信息码很多很多(大量数据)的情况

小结

定点数的表示

1.无符号数

全部都是数值,没有符号位

表示范围:0 ~ 2n-1,比如00000000 ~ 11111111(0 ~ 255)

2.有符号数

①原码

原码就是用二进制表示,带个符号位

比如机器字长是8位:

[x]原 =1,0010011 也可写为:[x]原 =1, 10011(未指明机器字长的时候把00忽略掉了)

[x]原 = 1.1100000

逗号和小数点只是表示前面的是符号位

②反码

若符号位为0,则反码与原码相同

若符号位为1,则数值位全部取反

“反码”只是“原码”转变为“补码”的一个中间状态,实际中并没什么卵用

③补码

正数的时候和原码是相等的!!!

补码的0只有一种表示方式

用10000000 来表示2-7,小数表示-1

所以补码的整数表示范围:−2n ≤ x ≤ 2n−1 (比原码多表示一个 −2n )

小数范围:−1 ≤ x ≤ 1−2−n (比原码多表示一个 −1 )

④移码

把补码的符号位取反

主要是为了方便两个数比大小,移码保持了相同的大小顺序

移码只能表示整数

若机器字长n+1位,移码整数的表示范围:−2n ≤ x ≤ 2n−1 (与补码相同)

小结

各种码的作用

原码就是表示成二进制

反码是原码到补码的过渡,没啥作用

1.补码的作用

补码——让减法操作转变为加法操作,节省硬件成本(无需减法器),执行加法操作时,符号位一起参与运算

计算机自带了取余操作,如果超过八位会把第一位丢掉

88-x→[ 88+(28-x) ] mod 28 (取余是计算机自带的)

而补码其实就是得到了 28-x 这么一个数

2.移码的作用

移码方便了整数之间比较大小(对于计算机来说)

移位运算

改变小数点和各个数字之间的相对位置,可以借此实现乘法和除法运算

1.算数移位

算数移位的符号位保持不变,移动数值位

①原码的算术移位

左移×2,右移÷2,由于位数有限有可能移动中丢弃掉一些,所以精度是不够的

②反码的算数移位

正数的时候和原码一样补0,负数的时候补1

③补码的算数移位

正数:与原码一样

负数的时候:左边补1,右边补0

算数移位的作用:用来实现乘除运算

2.逻辑移位

可以把逻辑移位看作是对“无符号数”的算数移位(都动,不像算术移位那样符号位保持不变)

3.循环移位

不带进位位:移出来的不仅要去另一头,还要去进位位

带进位位:移出来的去进位位,进位位去空出来的地方

循环移位可以实现两个字节里面的数据调换

小结

加减运算

1.原码的加减运算

2.补码的加减运算

符号位也参与运算

3.溢出判断

只有“正数+正数 ”才会上溢 —— 正+正=负

只有“负数+负数 ”才会下溢 —— 负+负=正

(很简单,正数和负数本身不会溢出,相加更是抵消了)

溢出的本质就是两个同号的相加最后得出来一个另外的,肯定就是溢出了

①一位符号位

②根据数据位进位情况判断溢出

| 、 | 符号位的进位CS | 最高数值位的进位C1 | 对应情况 |

|---|---|---|---|

| 上溢 | 0 | 1 | 符号位两个0,最高位进了1导致变成1 |

| 下溢 | 1 | 0 | 符号位两个1,最高位不进位导致变成0 |

CS与C1不同时有溢出

逻辑表达式为V=CS ⊕ C1

若V=0,表示无溢出;V=1,表示有溢出。

③双符号位

模4补码(双符号位)也只存储一个符号位,但是运算时会复制一个,然后把两个一起送到ALU中运算

4.符号扩展

补码的负数和移位的时候一样,左边补1右边补0

小结

乘法运算

1.原码的乘法

①手算

符号单独处理:符号位 = Xs⊕Ys

数值位取绝对值进行乘法计算

②机器实现

ACC初始置为0

MQ里最低位是1,ACC就加上X,是0就加0,然后ACC里的内容逻辑右移(最右边的直接丢了,因为后面用不到)

循环进行,最后把符号位修改了(符号位是单独处理的),乘数的符号位不用管,放在那就行。

乘数全部移出时结束

2.补码的乘法

补码的乘法要采用双符号位(因为MQ增加了辅助位,各个寄存器要保持一致,所以增加了一位符号位)

注意补码的算数右移

小结

除法运算

1.原码的除法

①恢复余数法

符号单独处理:符号位 = Xs⊕Ys

数值位取绝对值进行除法计算

计算机默认商为1,然后通过ALU计算出ACC的值(减法),如果发现是个负数(被除数小于除数),就会进行一个恢复余数的处理(ACC + |y|补)

然后ACC、MQ整体左移,ACC高位直接丢弃,MQ低位补0,接着循环,默认商为1……

最后MQ里全是商(图中黄色标记)的时候停止,如果最后一步余数为负也要恢复余数并商0

最后ACC里的就是余数,MQ里就是商

每次都恢复余数太麻烦,所以想到了优化办法

商0,把a变成2a+b即可(左移一位相当于 ×2 )

=左移一位再加上除数

②加减交替法

最后一步如果减出来是负数,要商0,并且把余数恢复(余数+|y|补)得到正确的余数(最后一步不移位),所以说虽然是不恢复余数法,但是要记住最后一步还是有可能恢复余数

2.补码的除法

用双符号位

末位商恒为1

小结

强制类型转换

定点整数是用补码存储的,所以短整数变长整数,负数补1正数补0

数据的存储和排列

1.大小端

大端模式:低位在大端

小端模式:低位在小端

2.边界对齐

每次访存只能读写一个字,所以对齐的话方便查找(用空间换时间)

浮点数的表示

1.浮点数的表示

2.规格化

补码尾数符号位与最高位一定相反

小结

IEEE 745(浮点数标准)

移码=真值+偏置值(偏置值就是移码把真值-128 ~ 127转换成0 ~ 255)

在一般移码中,偏置值=128,但是在IEEE 745中,偏置值等于127(2n-1)(因为-128和-127有特殊的用途,他们分别是11111111、00000000,所以让-128转换成了11111111)

这个图里表格里的内容要背下来,做题时不会告诉

其中偏置值2n-1-1,n用阶码的值代入

真值正常范围:-126 ~ 127(其他也是去掉前面两个推)

尾数部分隐藏表示最高位1,也就是默认尾数为1.M(M是尾数记录的值)

记住 移码=真值+偏置值(127)

把移码的值算出来,得到129,所以真值=129-127=2,也就是阶码的值为2

后面一串尾数(隐藏最高位1),1.01000……=1.25,再考虑到符号位为1(负),所以浮点数真值=22× (-1.25)= -5.0

阶码全为0或1的作用(-128、-127)

全为0,就是把隐含的最高位改成0(这样可以表示更小的数)

全为1,表示无穷大(尾数如果不全为0说明发生了非法运算)

小结

浮点数的加减运算

1.浮点数加减运算

小阶向大阶对齐:如果大的向小的对齐,算完之后肯定要规格化,很麻烦,但是小向大对齐可能就不需要规格化

对阶的时候:X的阶码011→100(+1),尾数部分右移,左边补1

规格化:尾数符号位是10说明溢出,右移,符号位变成11(最高位的符号位代表正确的),阶码 +1

舍入:右规时发生

舍0进1法:舍弃的最高数为1时,进1,为0就丢掉

恒置1法:不管丢多少都把尾数末位置于1

2.强制类型转换

虽然浮点数类型也占那么多位,但是实际数值不是全部,比如float是 1 + 8 + 23(隐含1位所以实际有效数字是24位)。这样int→float会损失精度(要丢弃一部分)

float→int 也损失精度:float表示的小数范围更大,所以会损失精度

小结

算术逻辑单元

1.算术逻辑

机器字长就是ALU输入输出接多少线,一次能处理多少,其他寄存器要和ALU保持一致

同或就是相同为1不同为0,符号是⊙

与或和乘法加法很像,优先级:与>或

本质上逻辑表达式就是电路的数学表示,优化逻辑表达式等于优化电路,能省钱

异或的表示:

A

‾

・

B

+

A

・

B

‾

\overline{A}・B + A・\overline{B}

A・B+A・B(10、01的时候为1)

2.加法器

加法器的基本构造

①串行加法器

②并行加法器

可以同时输入各位的数据(算是并行了,提高速度了),但是要实现运算需要等待上一位的进位

小结

加法器、ALU的改进

理解即可,不是特别重要

1.加法器的改进

进位生成信号g:XiYi

进位传递信号(函数)p:Xi⊕Yi

在之前,每个加法器需要等待之前的进位才能开始运算,所以速度还是有限

在展开逻辑表达式之后,其实是可以一直推到C0的,而C0是一开始就输入了的数据,所以从这方面入手可以提高各个加法器之间的并行程度

每个展开式里都有相同的地方,用另一种表示方式来简化它

①单级先行进位方式

由于超过四个会使电路越来越复杂(成本过高),所以一般来说以四个为一个单位,相当于他们组成了个新的部件。(也就是形成了4位CLA加法器)

可以把这么一个部件看成输入输出同步(内部),然后再和外面的有互相等待进位的关系

这个就是组内并行,组间串行

②多级先行进位方式

再套一次娃,把4个4位CLA加法器整到一起,取他们逻辑表达式里相同的

这个就是多级先行进位方式,组内并行,组间并行

2.ALU芯片的优化

ALU也是这个原理,四个一组套上娃,内部并行,不够就继续套娃(反正套上娃了内部就看成并行的)

706

706

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?