在verilog设计过程中,调用实例化模块时是非常头疼的一件事,因为位置绑定不安全,必须使用名称绑定,手动一个个码就很烦

于是用python写了一段代码。缺点是没有用正则表达式来除去[],也没有用特定的方式来终止键入。

out=''

for i in range(1,50):

temp=input()

temp = temp.replace("input", '')

temp = temp.replace("output", '')

len_temp = len(temp)

for k in range(len_temp):#remove [*]

if (temp[k] == ']'):

temp = temp[k + 1:]

break

temp=temp.replace(",",'')

temp = temp.replace(";", '')

temp = temp.replace(" ", '')

ins = '.' + str(temp) + '(' + str(temp) + '),\n'

out = out + ins

print('\n')

print(out)

使用方法:

复制要实例化的信号,运行python代码,然后在pycharm的命令窗内输入复制的verilog代码,然后就得到了实例化的信号。

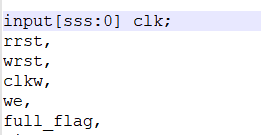

待输入的信号:

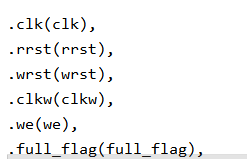

实例化的信号:

621

621

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?