目录

6.3 调用Synopsys DesignWare来优化设计

第四章 SOC系统架构设计

4.1 SOC系统架构设计的总体目标与阶段

SoC系统架构的总体目标就是设计者针对应用的特点,选取合适的功能模块及模块之间数据的通信方式,在满足总线吞吐率、芯片面积、功耗等一系列系统约束的条件下,从众多系统架构方案中找到最优的SoC系统架构方案。

SoC的系统架构设计的过程还可分为以下3个阶段:功能设计阶段、应用驱动的系统架构设计阶段和基于平台的系统架构设计阶段。

4.2 SoC中常用的处理器

在SoC中使用的处理器主要分为3类:通用处理器(CPU)、数字信号处理器(DSP)和可配置处理器。通用处理器主要负责控制、操作系统平台和一般的信号处理等任务,使用较多的通用处理器有ARM、MIPS、PowerPC、RISC-V等。

4.3 SoC中常用的总线

总线提供了系统中各个设备之间一种互连的访问共享硬件机制。在数字系统中,总线承担数据传输的任务如处理器和存储器之间的数据传输。总线的传输能力由总线的宽度和工作频率决定,总线的设计通常要考虑4个因素:总线宽度、时钟频率、仲裁机制和传输类型。总线带宽 = 总线位宽 X 工作频率。

4.3.1 AMBA总线

AHB总线连接的外围设备有处理器、DMA控制器、片内存储器、外部存储器接口、LCD控制器等,AHB总线支持仲裁、突发传输、分离传输、流水操作、多主设备等复杂事物。

APB总线连接的外围设备有UART接口、键盘、 USB接口、键盘接口、时钟模块等。APB没有复杂事物实现,非流水线操作,可达到减少功耗和易于使用的目的。

4.3.2 CoreConnect总线

CoreConnect是IBM开发的一套片上系统总线标准,包括PLB(Procesor Local Bus)总线,OPB(On-Chip Peripheral Bus)总线、DCR(Device Control Register)总线。其中PLB总线连接高性能设备如处理器、存储器接口、DMA等。OPB总线连接低性能设备,如各种外围接口等。

4.3.3 Wishbone总线

4.3.4 开放核协议(OCP)

4.4 SoC中典型的存储器

在SoC中,存储器是决定性能的另一个重要因素。典型的SoC存储器体系包括处理器内部的寄存器和高速缓存(Cache)、片内ROM、片外主存。

4.4.1 存储器分类

- 按照存储介质分类:半导体材料、电磁材料和光介质;

- 按照存储方式分类:随机存取存储器(RAM)、顺序存取存储器(SAM)、相连存储器;

- 按信息是否可更改分类:读/写存储器、只读存储器(ROM);

- 按照断电后信息的可保存性分类:非易失性存储器(NVM)、易失性存储器(VM);

4.4.2 常用的存储器

- 静态随机存储器(SRAM,Static Radom Acess Memory)是一种具有静止存取功能的存储器,即不需要刷新电路,SRAM中每个存储单元需要由6个晶体管构成。

- 动态随机存储器(DRAM,Dynamic Radom Acess Memory)是SoC中采用最广泛的存储器,每个存储单元由一个电容和一个晶体管构成。

- 闪存Flash是一种基于电荷存储、价格性能兼顾的非易失性存储器,能以块为单位进行擦除与编写,是电可擦除只读存储器(EEOROM)的变种。

4.4.3 新型存储器

SoC中广泛采用基于“SRAM+DRAM+Flash”的混合存储模式。

4.5 多核SoC的系统架构设计

多核SoC也称为多处理器架构的SoC可以完成这样一个复杂任务分解到多个内核中去执行的任务。

4.5.1 可用的并发性

并发性分为三种:

-

- 指令级并行性(ILP,Instructions Level Parallelism):利用指令之间的无关性,使得多条指令可以同时执行,改变传统串行执行指令造成的较大延时,提高指令和程序的执行效率;

- 数据级并行性(DLP,Data Level Parallelism):指一组待处理的数据内部存在较为松散的依赖关系,在理论上可以对这些松散数据并行执行;

- 任务级并行性(TLP,Task Level Parallelism):可以从原本的串行任务中提取出来。

4.5.2 多核SoC设计中的系统架构选择

- 处理器与存储器架构;

- 核间通信与Cache的架构;

- 操作系统的设计;

- 提高并行性;

4.5.3 多核SoC的性能评价

4.5.4 几种典型的多核SoC系统架构

- 片上网络;

- 通用处理器和DSP结合的异构多核架构;

4.6 SoC中的软件架构

- 数据流的路径;

- 软件环境;

- 软硬件接口;

- 存储空间映射;

- 设备驱动;

- 初始化、复位、Bootloader程序;

- 中断服务程序及中断向量;

- I/O脚的复用;

- 模型。

4.7 电子系统级(ESL)设计

第五章 IP复用的设计方法

5.1 IP的基本概念和IP分类

- IP的定义:一种事先定义,经验证可以重复使用的,能完成某些功能的组块。

- IP的分类:

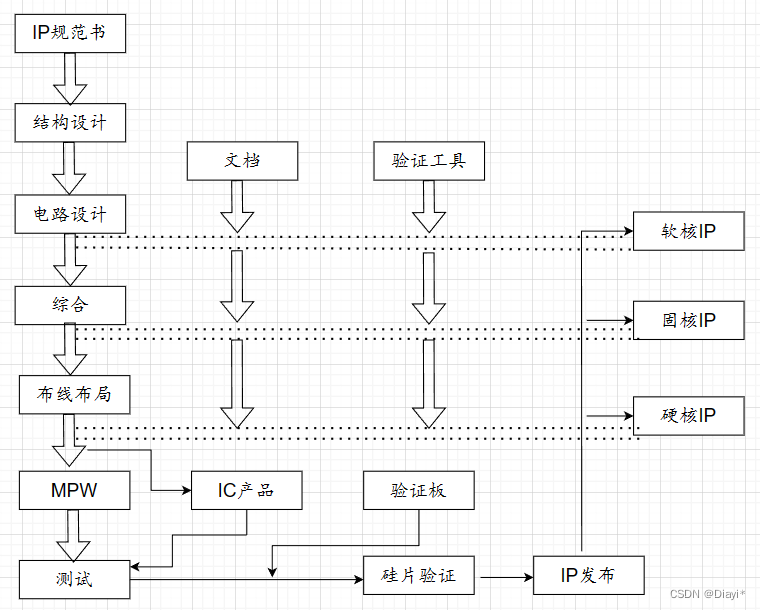

- 从设计流程区分:软核IP、固核IP和硬核IP;

- 依差异化程度来区分:基础IP(Foundation IP)、标准IP(Standard IP)和明星IP(Uniqie IP);

5.2 IP设计流程

5.2.1 设计目标

-

- 可配置,参数化,提供最大程度的灵活性;

- 标准接口;

- 多种工艺下的可用性,提供各种库的综合脚本,可以移植到新的技术;

- 完全、充分的验证,保证设计的健壮性;

- 完整的文档资料;

5.2.2 设计流程

定义关键特性-->规划和指定设计规范(包含功能设计、验证、封装规范和开发计划)--> 模块设计和集成(包含设计流程、硬核的模型建立)-->IP产品化(P86表)。

5.3 IP的验证

- IP验证计划

- 验证策略的描述;

- 仿真环境的详细描述,包括模块关系连接图;

- 验证平台部件清单;

- 验证工具的清单还包括仿真器和验证平台自动产生工具;

- 特定验证向量清单;

- IP关键特性的分析报告;

- 每一个子模块核和顶层IP测试覆盖率的说明;

- 用来说明验证要达到的标准的规范;

- IP验证策略

- 兼容性验证;

- 边界验证;;

- 随机验证;

- 应用程序验证;

- 回归验证;

- 验证平台的设计

5.4 IP的选择

- IP种类的选择

- 产品完整性

5.5 IP交易模式

5.6 IP复用技术面临的挑战

- 可复用性和多IP集成

- 复杂冗长的验证和仿真时间

- 来自商务模式的挑战

第六章 RTL代码之前的准备

6.1 编写RTL代码之前的准备

- 根据芯片架构准备设计说明书

- 总线设计的考虑

- 模块的划分

- 对时钟的处理

- IP的选择及设计复用的考虑

- 对可测性的考虑

- 对芯片速度的考虑

- 对布线的考虑

6.2 可综合RTL代码编写指南

6.2.1 可综合RTL代码的编写准则(编码风格)

- 命名

- 编码风格

- 综合考虑

6.2.2 利用可综合进行代码质量检查

- 模块的分割最好能够使得在模块内部的输入和输出端直接和触发器相连接,这样在综合的过程中,时序约束的设置将非常方便;

- 避免触发器在综合过程中生成锁存器,在if else语句中,如果设计没有很好的覆盖到各种情况,就很有可能综合产生锁存器的结构;

- 避免不必要的函数调用,重复的函数调用会增加综合次数,不仅造成电路面积的浪费,还会使综合时间变长;

- 通常在verilog语言中,有always和initial两个程序块,Synopsys的综合工具忽略initial程序块,并产生警告;

- 在综合过程中,工具将忽略电路中的延时语句,例如“assign #10 C = A&B”在综合时就相当于“assign C = A&B”,因为综合时相关的时序在选用标准单元库中都有描述。

1036

1036

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?