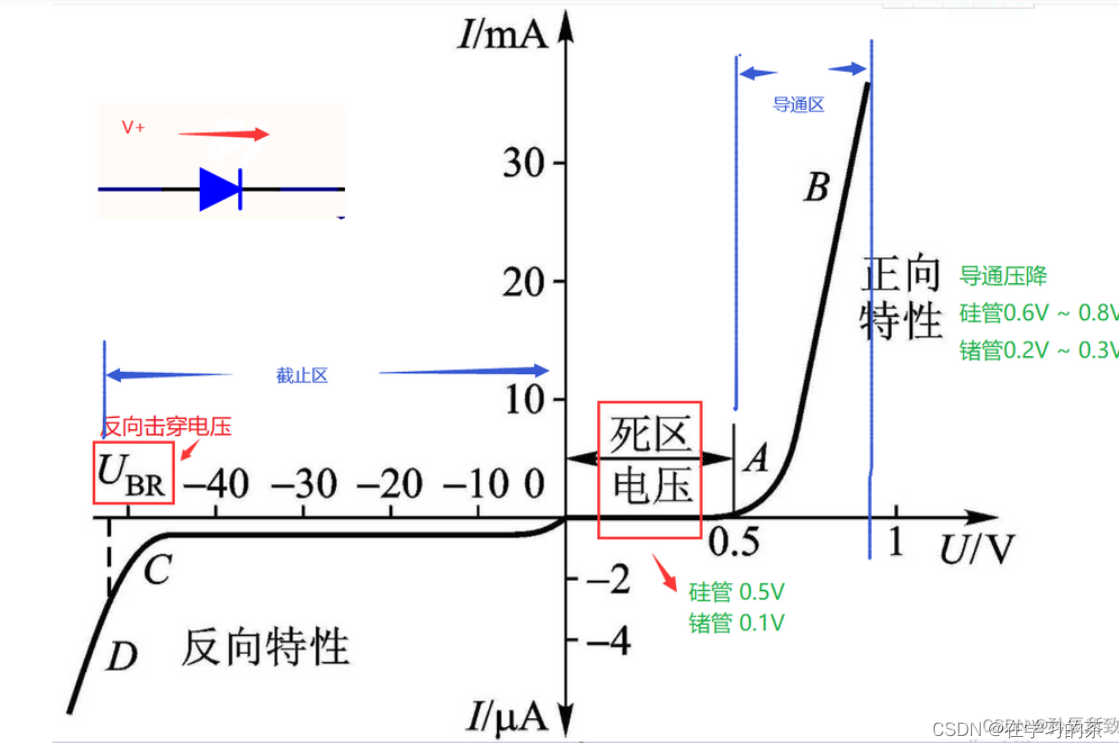

用二极管设计的话,最大问题是有效区间绝对不一样,导致不稳定!!

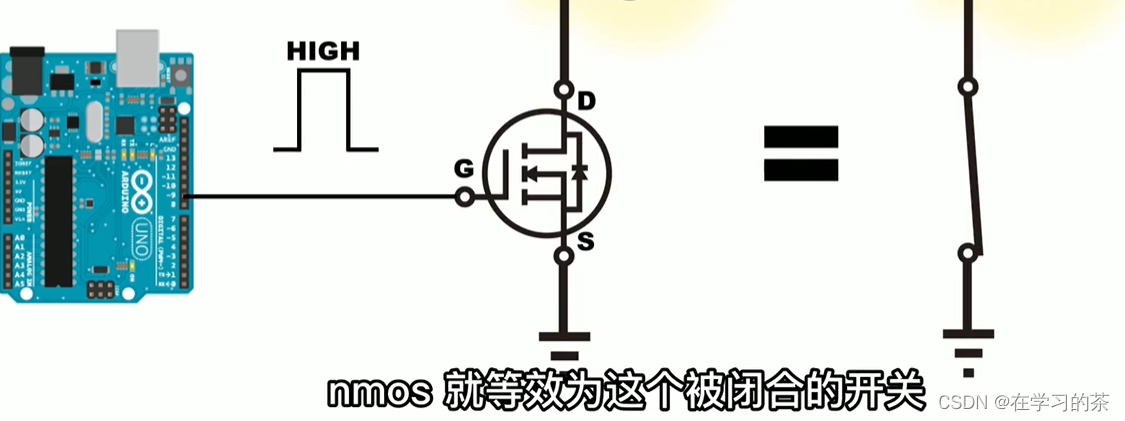

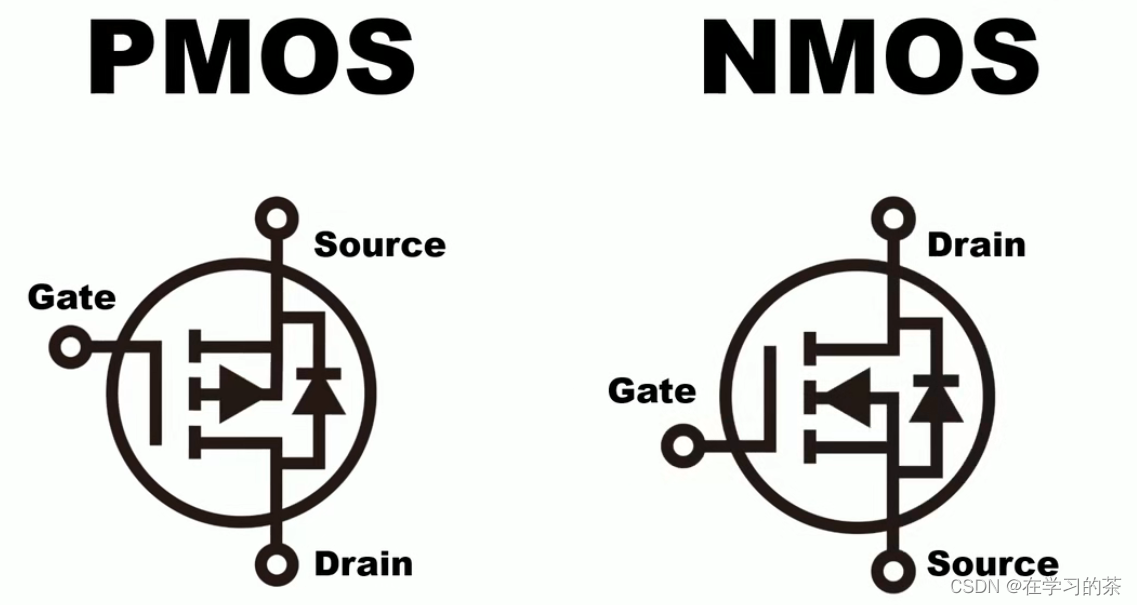

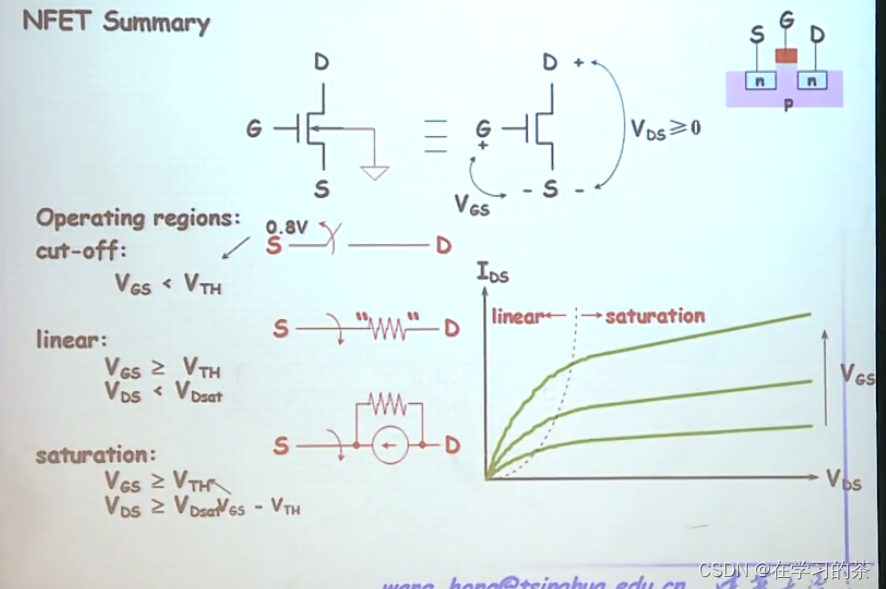

NMOS

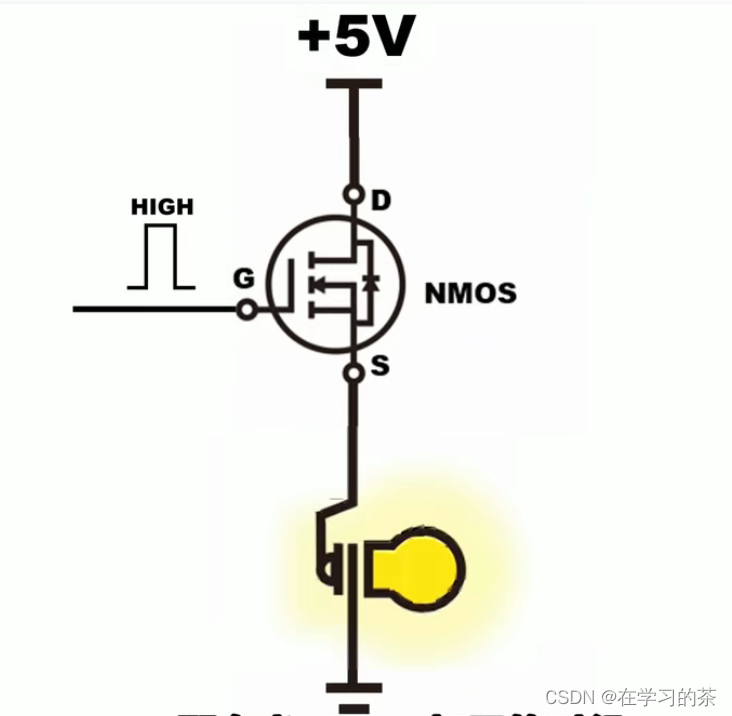

这个开关就是NMOS

G输入1,也就是灯亮;G为0等价于灯灭

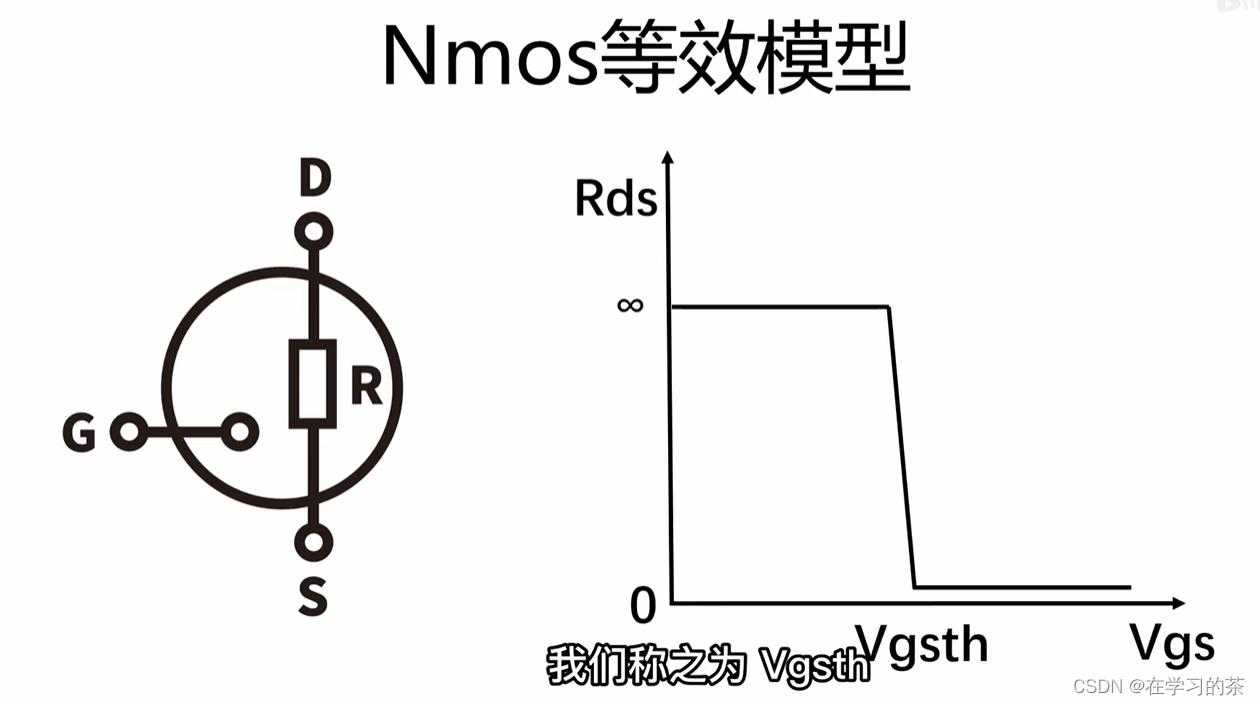

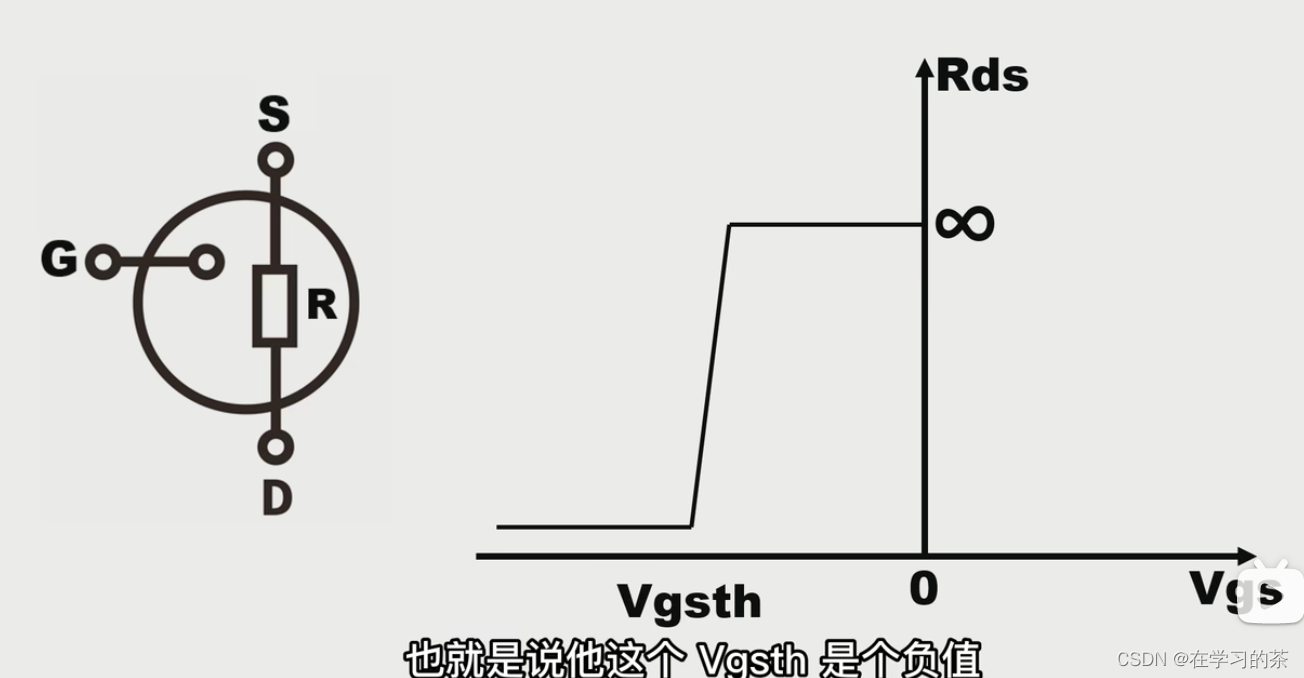

NMOS可以视作电压控制的电阻,电压是GS的电压差

封装:就是MOS的尺寸

Vgsth:打开MOS的属性电压,最高我们的高电平比Vgsth略高,防止干扰

Rdson:MOS被完全打开时的DS电阻,越小越好

Cgs:GS之间的寄生电容

制造工艺无法避免。影响MOS打开速度

Rdson和Cgs一般呈反比

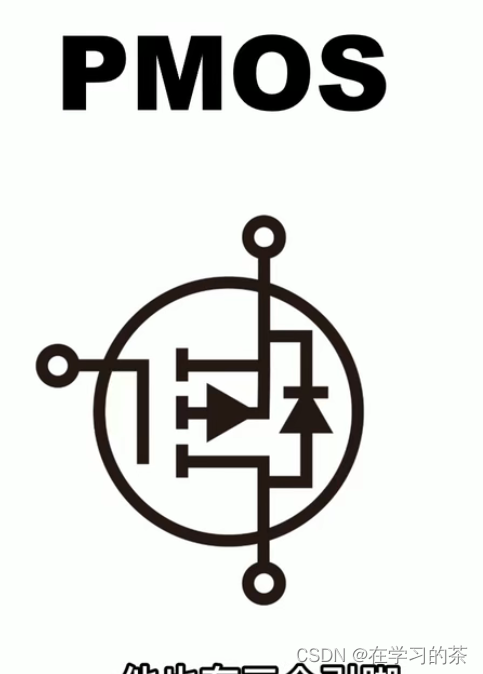

PMOS

PMOS是G低,灯亮,G高电平,灯灭

正好与NMOS相反

为什么要产生PMOS?

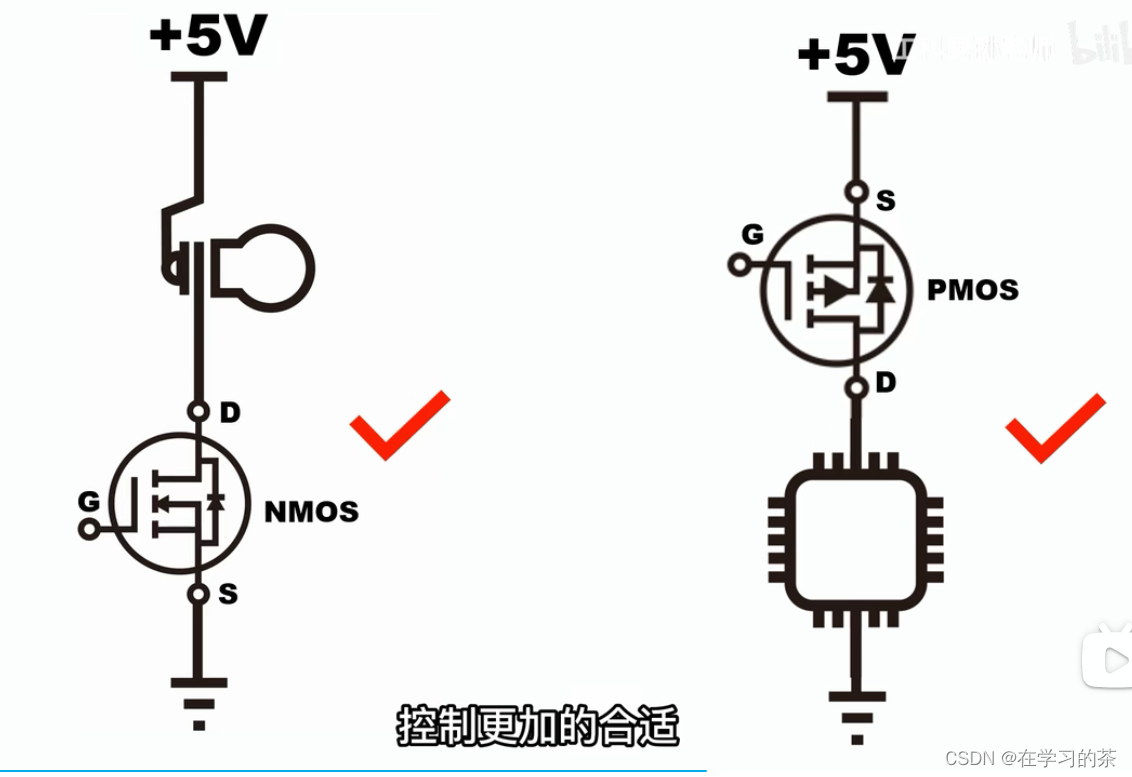

当 我们把NMOS放在灯泡上面,G给出5V电压后,电路接通,那么GS电压要维持5V,必须给G10V,而我们没有10V的电压,所以如果开关在上面 的状态,就必须用PMOS了

这对芯片来说就很有必要:接地+掐点VCC电源

N下P上

他这个图的意思就是,把MOS打通后又分了两种情况,根据V-DS大小来分

而那个电流的变化可以视作线性变化的电阻

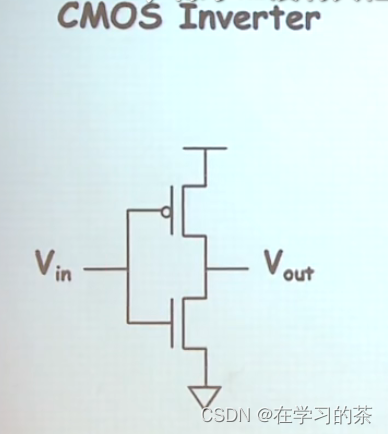

CMOS=组合NMOS、PMOS

这样如果低的1,直接接电源给你高1,如果高的0,直接接地给你低的0

上面的是PMOS, Vin=1时,量的电源和Vin的电压是0,上面不导通,而下面的Vin和地产生电压,导致下面导通。这样Vout是0,而且是很低的0.构成反相器

相反Vin=0,Vout=1,而且是很高的1

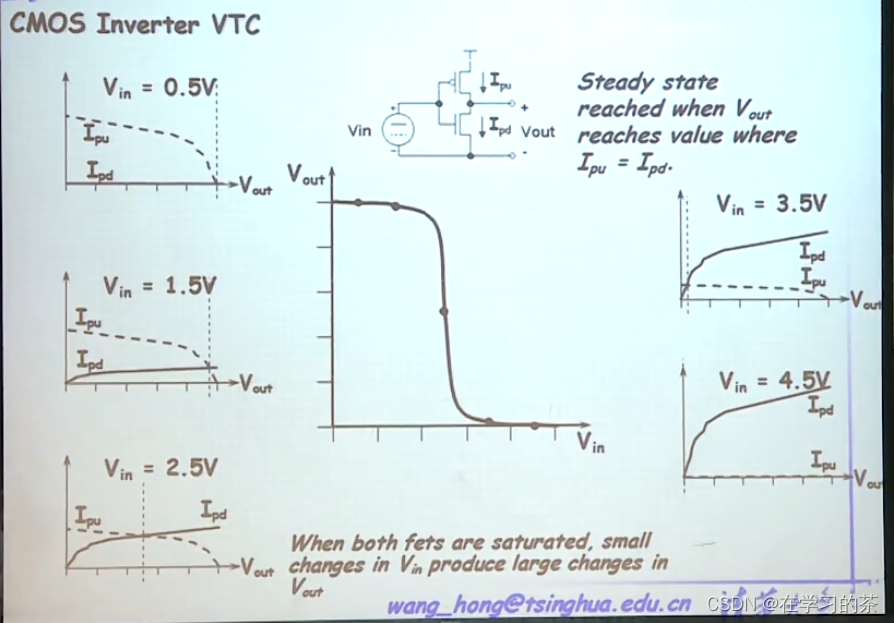

那如果是中间的电压,怎么办

如果是无效电平,会导致两个MOS一起导通, BC段电路负载过大,不稳定,尽量避免此状态

输入端噪声容限

指的是输入低/高电平的电压区域范围

V-DD电源电压升高,噪声容限也升高

CMOS的静态特性——输入输出特性

输入端特性:因为MOS可以背击穿,所以要加一个输入保护电路,原理是利用二极管的反向击穿保护MOS

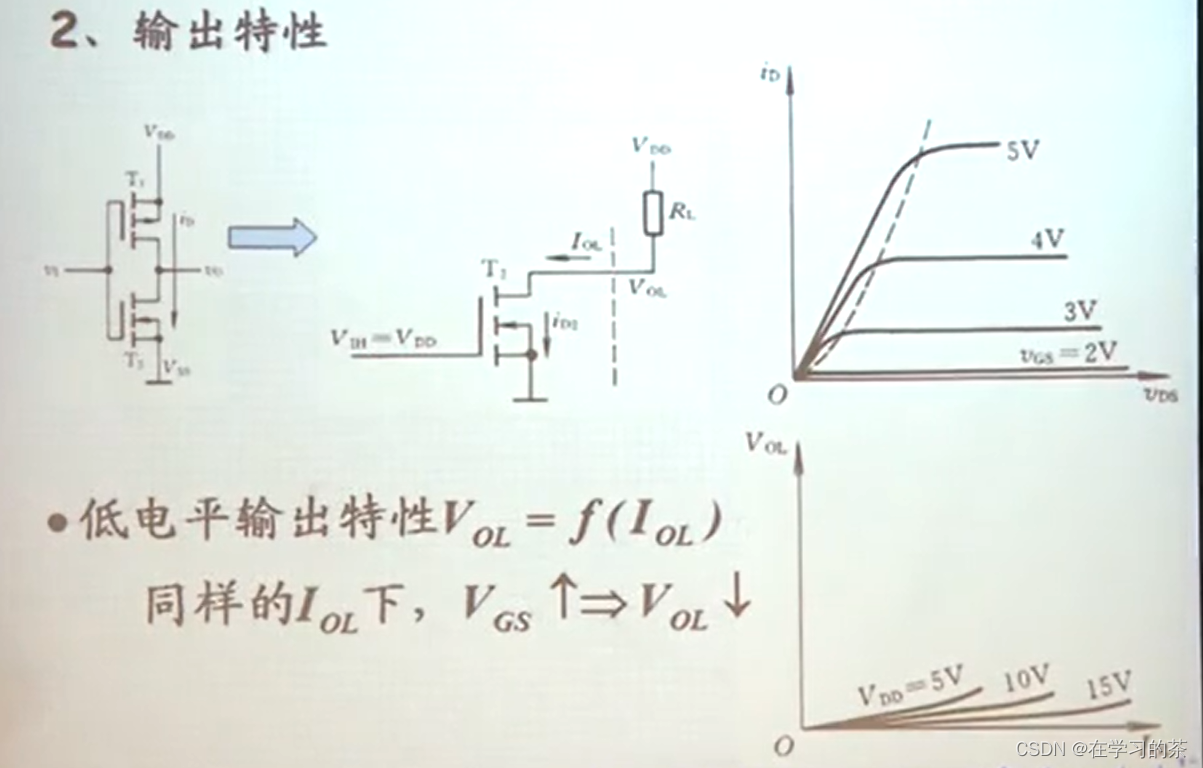

输出端特性:

Vol是输出电平,Vgs高,说明Rds越来越小,直到Rdson,那就说明Vgs狂加大,Rdson趋近于0导致输出电压接近0,也就是Vol下降

反之一样

最后一个话是:Voh下降的越少,也就是相对增高

CMOS的动态特性(电路状态转换的特性)

当输入电压发生变化,输出电压一定会滞后变化,这一时间叫做传输延迟时间。这一现象的原因是电容电压差不可以突变

MOS在静态时(恒1/恒0)功耗为0,工作起来时绝对不是0,因为尖峰电流跳变会产生功耗

其他MOS电路

我们假设上面是电源,下边是地。

AB必须都是1,左边才通,右边仅AB都是1,电路不通,存在0就通,构成互补关系

PMOS是强1器件,NMOS是强0器件,防止阈值损失

也就是说P负责上拉,N负责下拉;所谓上拉也就是把结果变成1,下拉就是把结果变成0

OD门

(49条消息) OC, OD门和线与逻辑_dongdongnihao_的博客-CSDN博客_线与逻辑功能是什么

OD门的符号

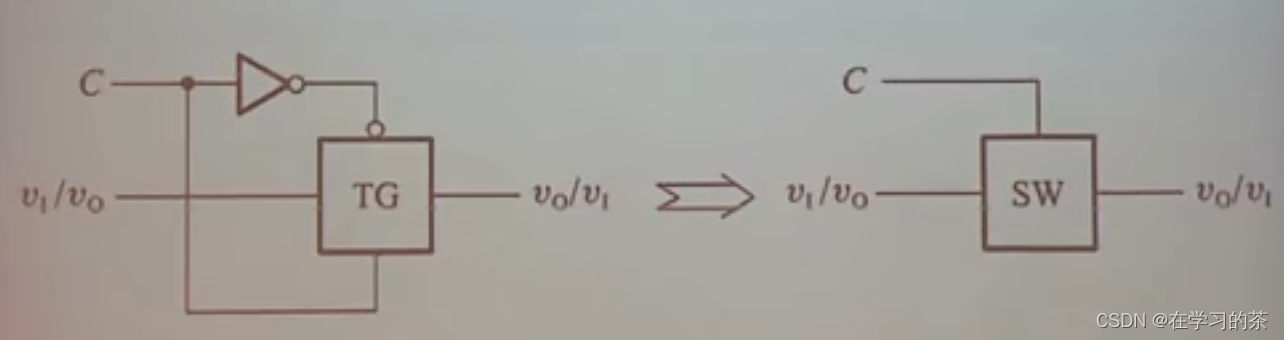

CMOS的传输门

两个简化标记

上下的高低电平会取反。开关断开称之为高阻态

三态门

EN的优先级最高。

总线仅一个设备为1

4634

4634

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?