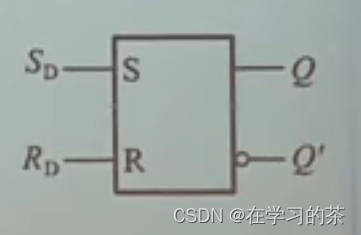

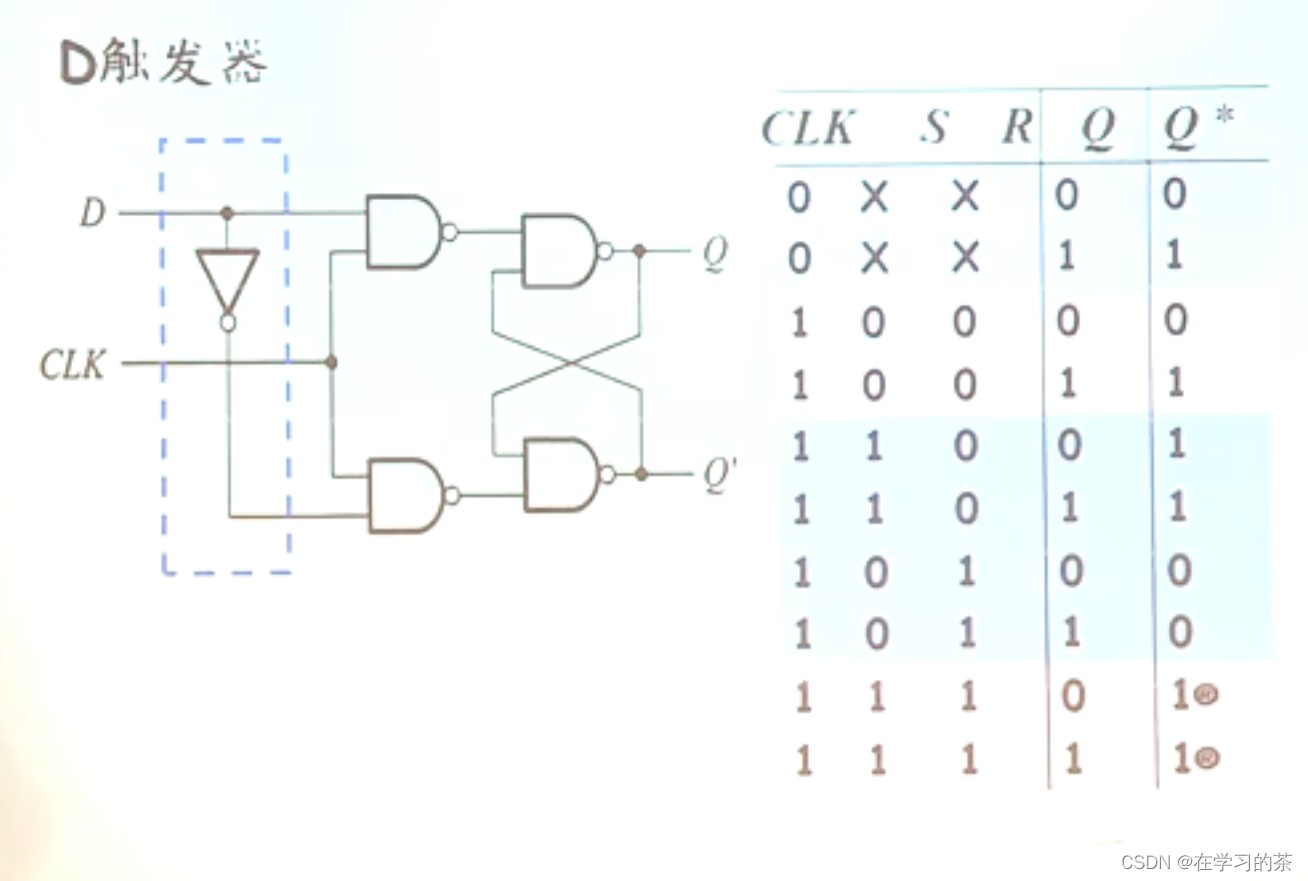

要这样说:RS电平触发器才准确

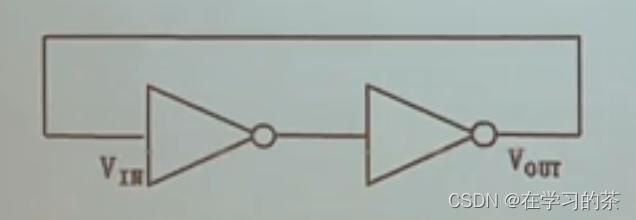

这个电路用来保存0/1(Vin=Vout),但是我们还可以进行优化

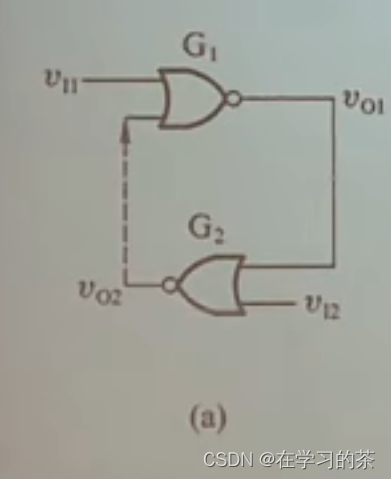

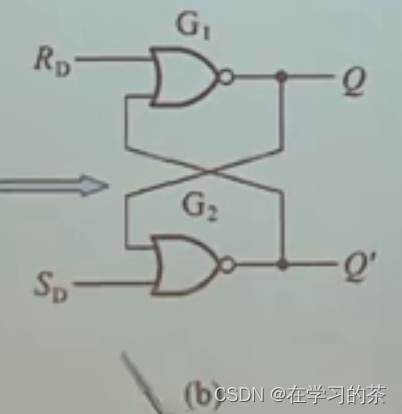

当v11,v12给0,整个电路就相当于上图

这个和上图等效,我们把Q作为存的数

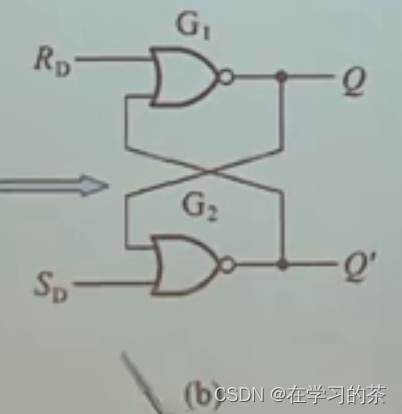

当我想存0,Q=0,Rd给1 Sd给0

当我想存1,Q=1,Rd给0 Sd给1

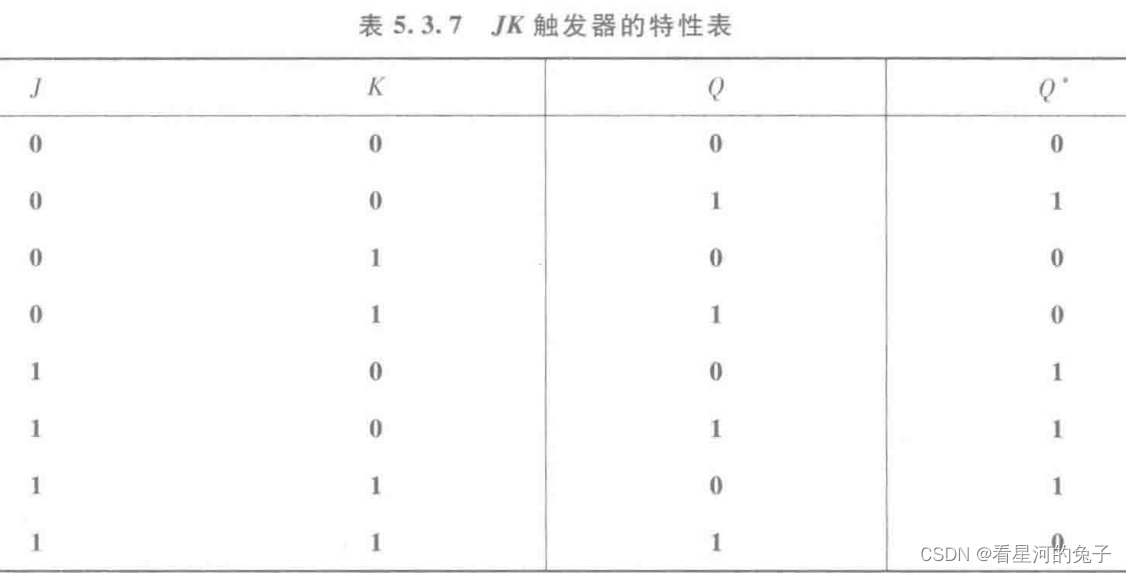

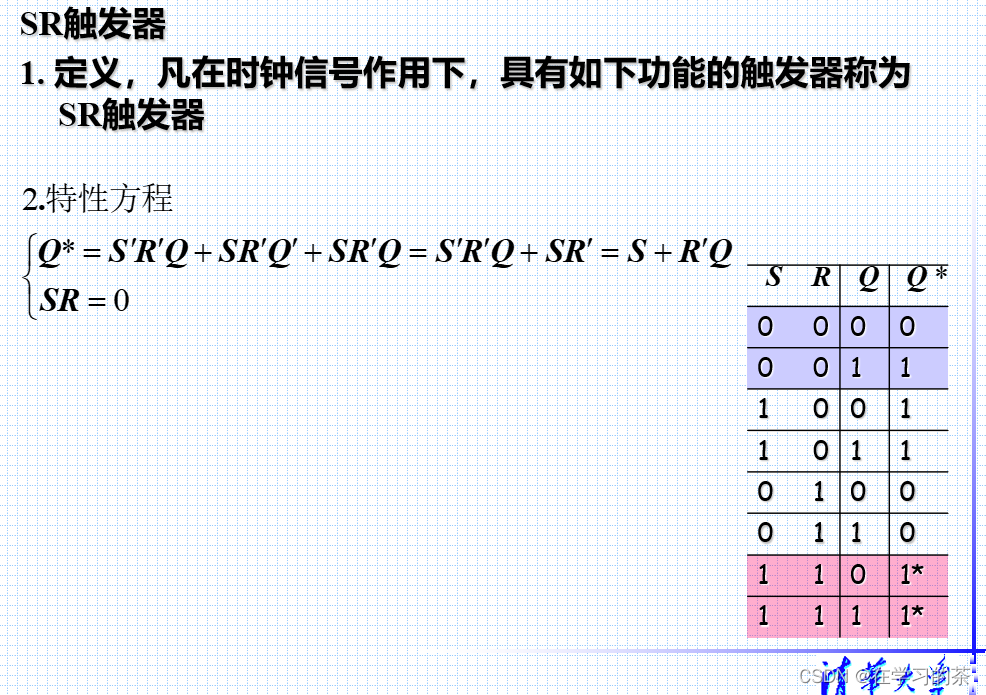

设Q*是现在的cue(次态),Q是过去的cue(现态)

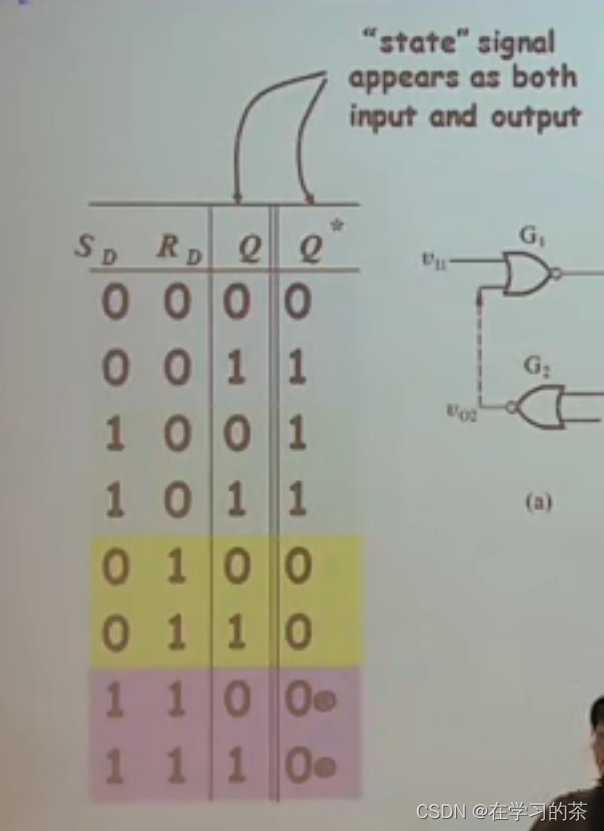

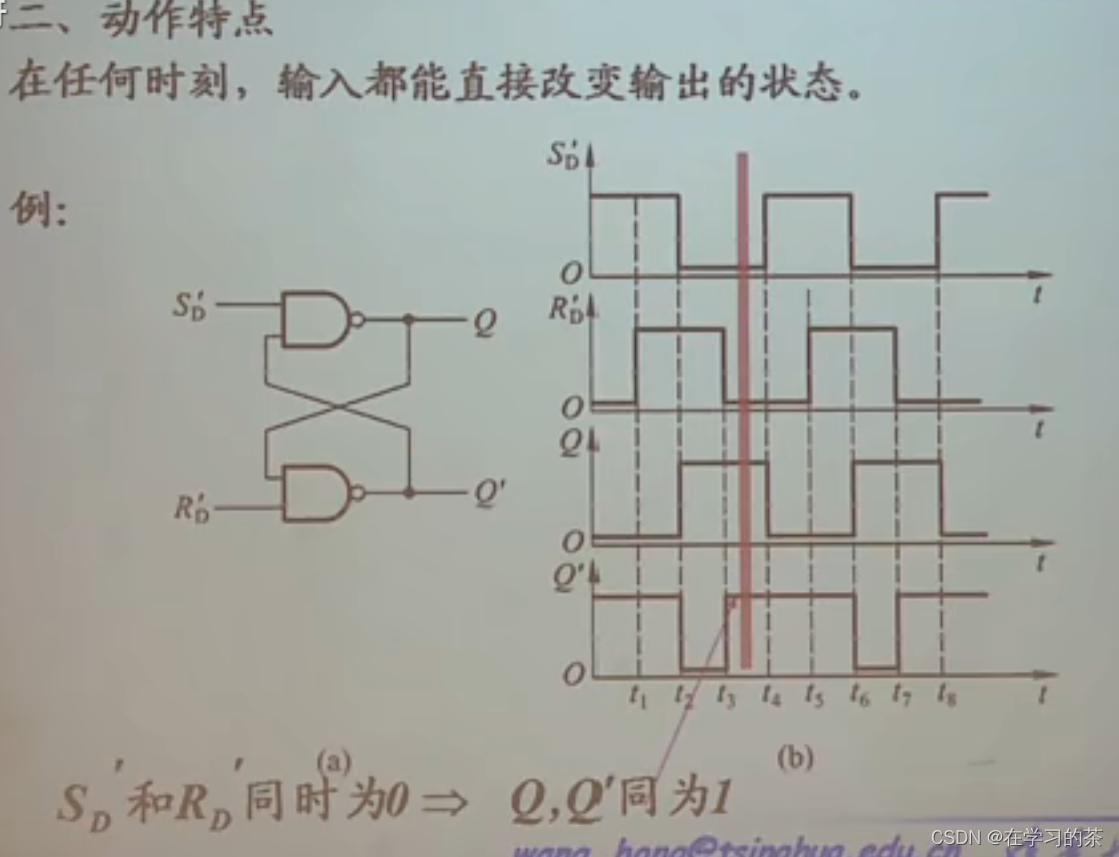

那如果Sd和Rd都是0,

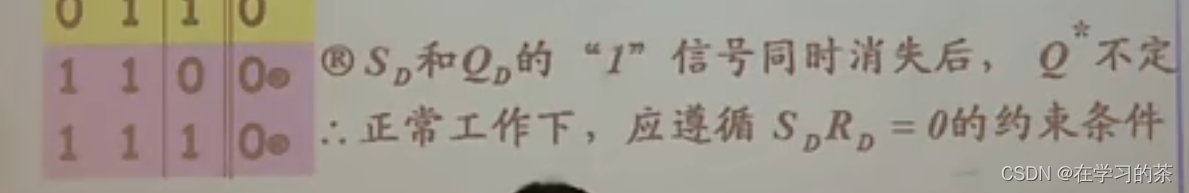

注意这个同为11,那么当11消失的时候会有大灾难

也就是Q和Q反会01乱蹦

这个SR锁存器有上图的特点 ,当他不定的时候,Q和Q反始种相反电平

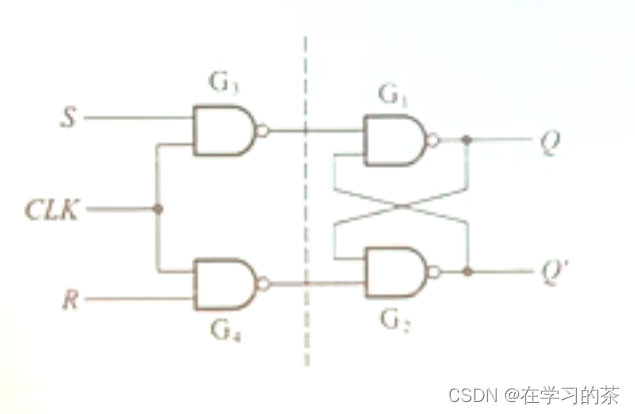

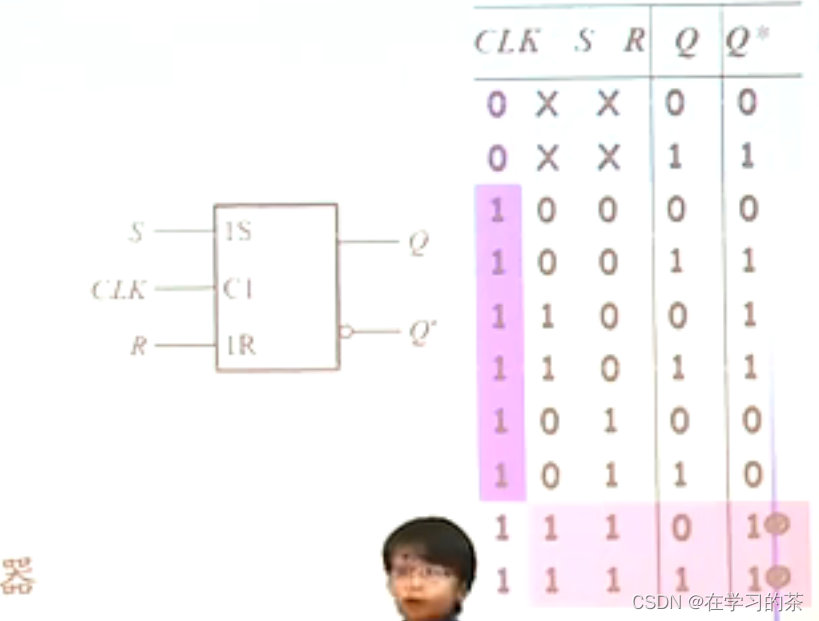

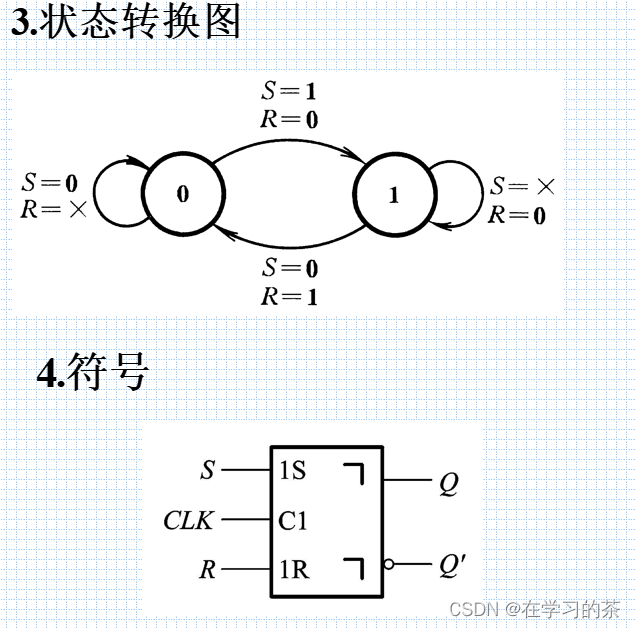

上图是加了个CLK时钟信号,只有CLK=1的时候才允许数据进入

当CLK=0的时候,因为这里是与非门,所以是11的时候不变,也就是保持与上一时刻相同的Q

也就是说CLK=1的时候,SR才起作用,S是置1端,R是置0端

为什么要叫触发器,当CLK=1的时候我们这个才触发,叫触发端。

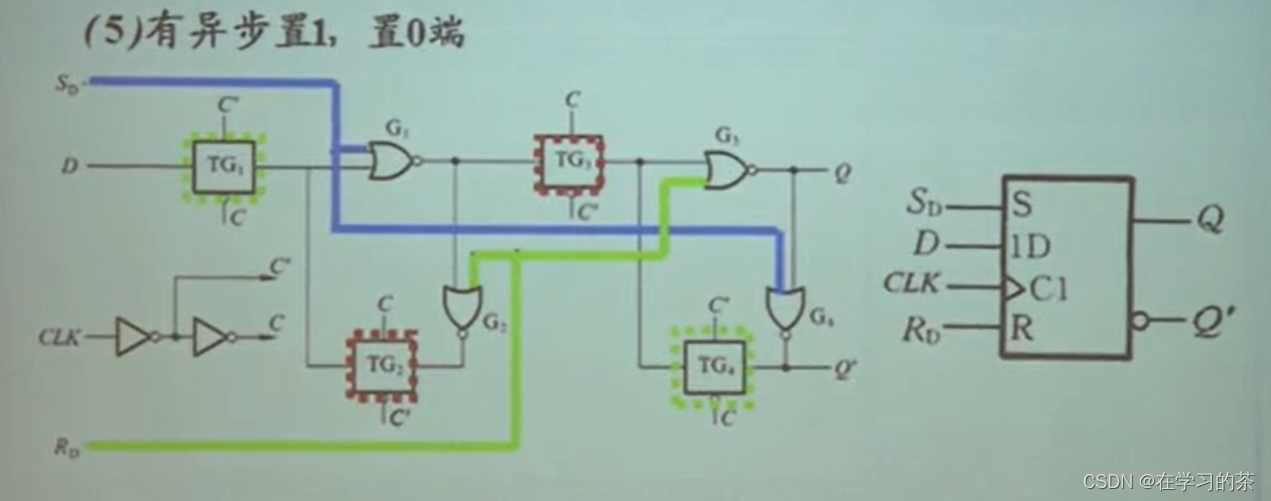

我们定义:

同步信号:和CLK相配合

异步信号:不和CLK配合

所以说

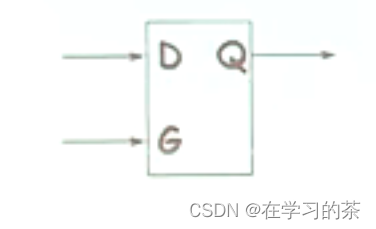

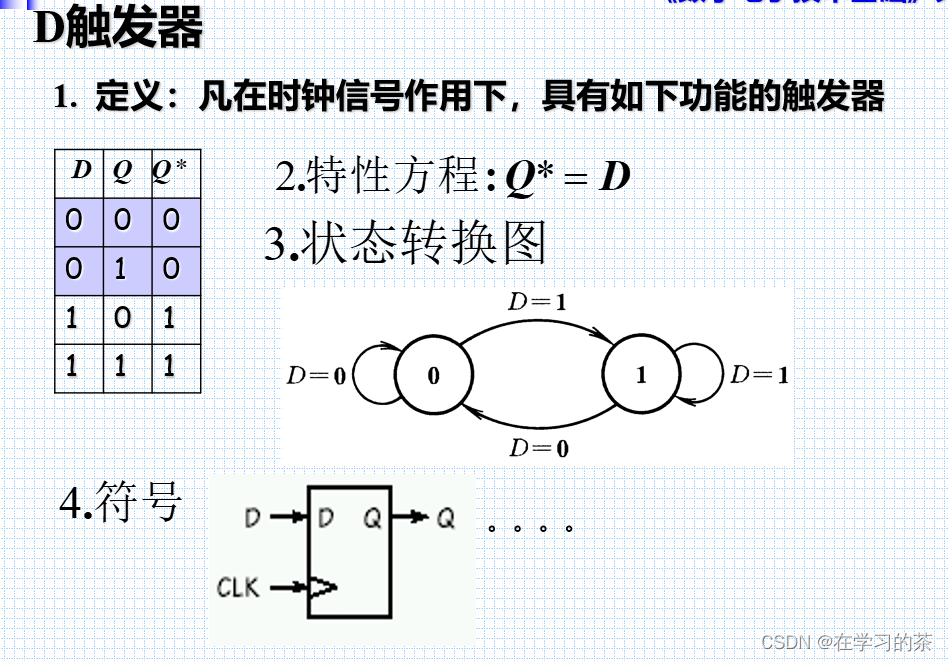

D触发器是为了构成01或者10的输入,因为00保持信号已经被CLK接管了

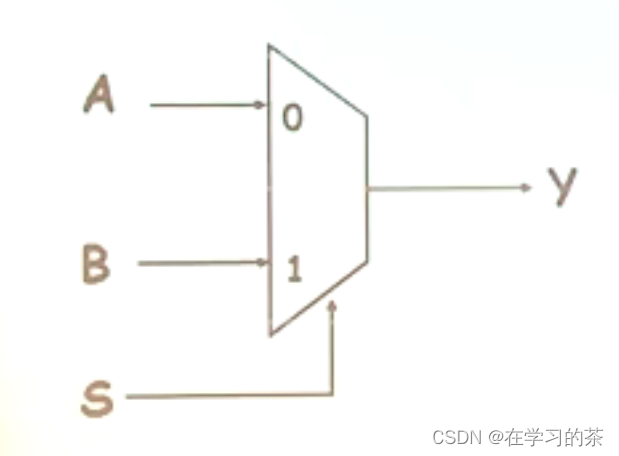

这是一个数据选择器,我们 改一下标号

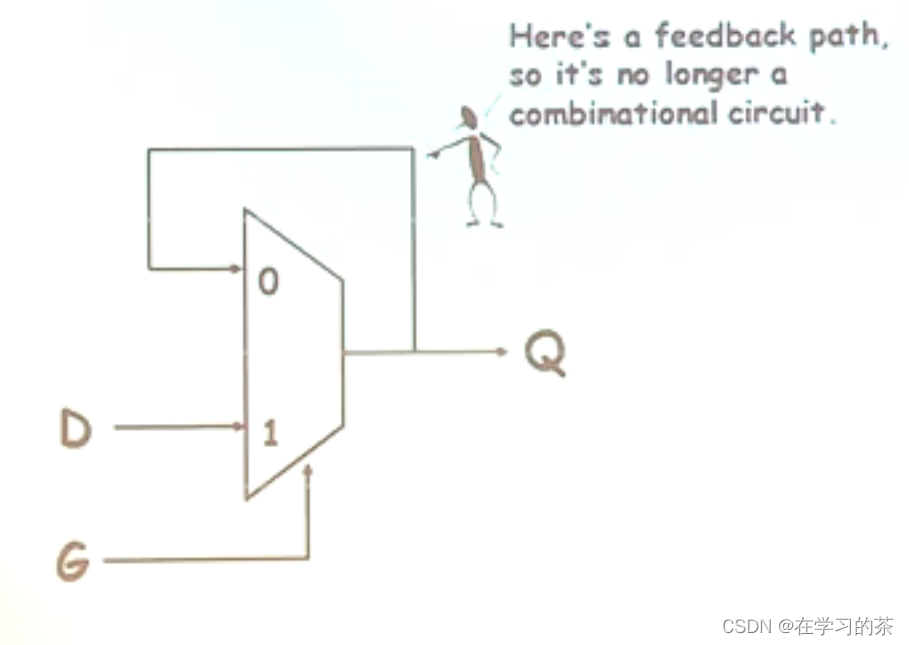

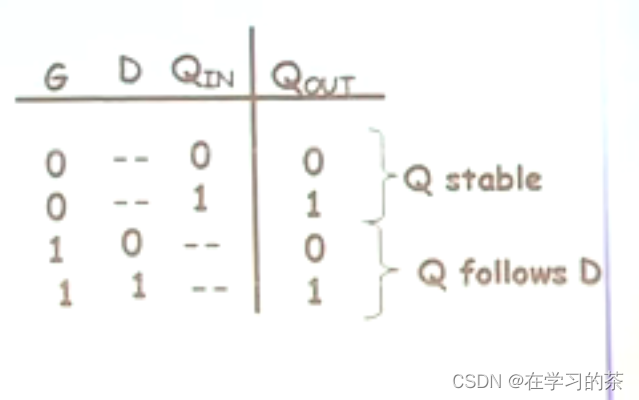

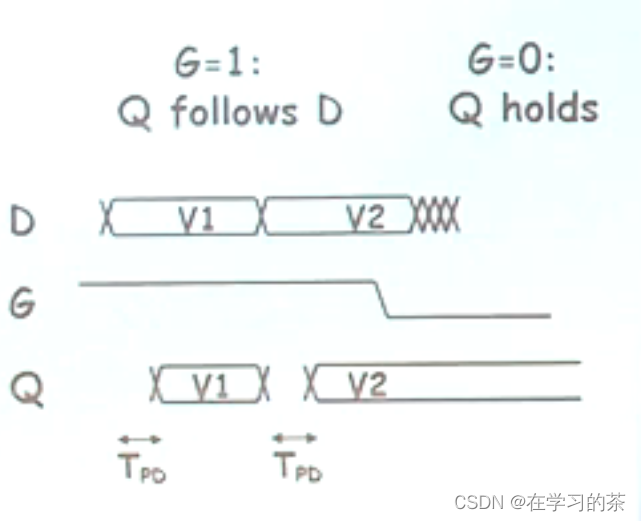

G给0,Q就保持。G给1,Q就是D的值

也可以叫D触发器

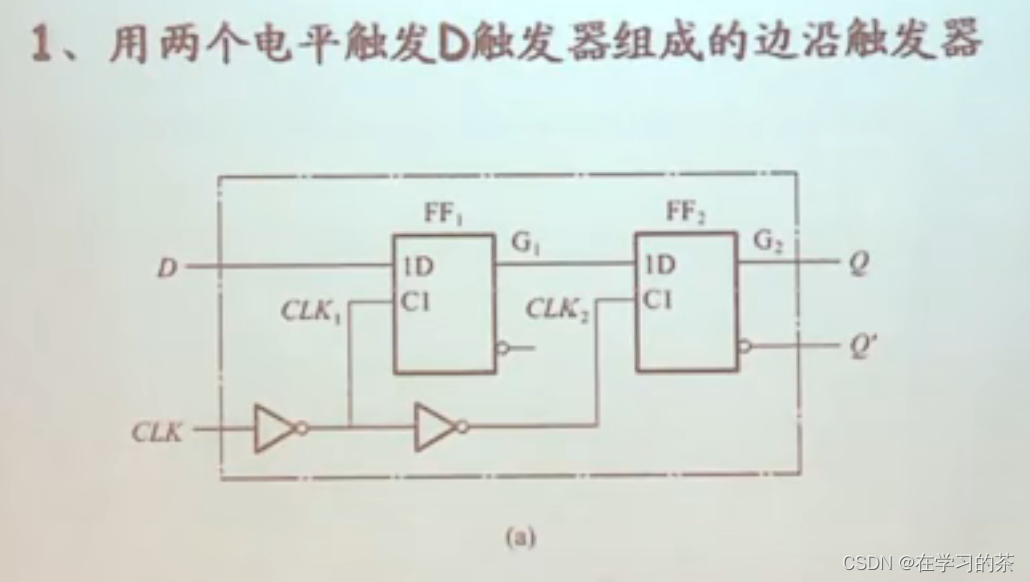

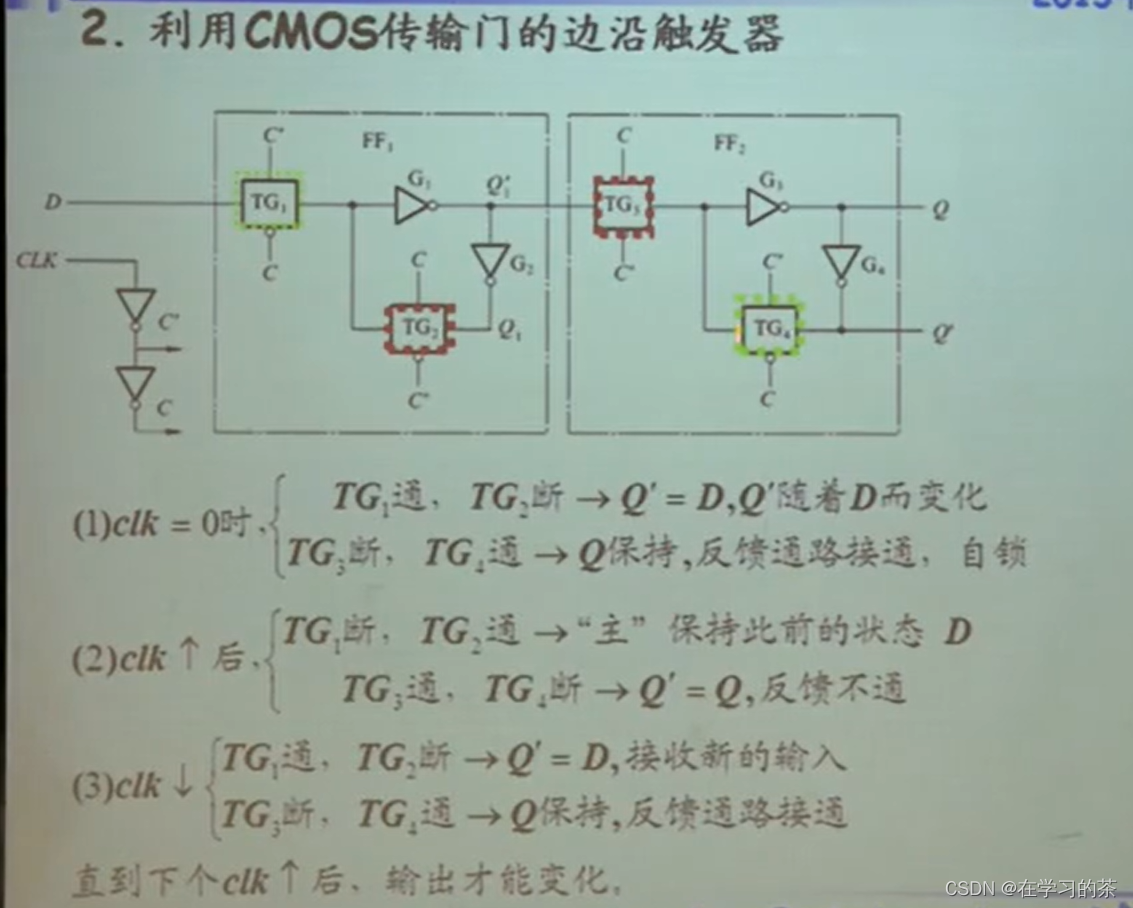

这个触发器牛逼了,按一下按钮:第一个Q输出D,松开按钮最右边的触发器输出第一个输入的D!!!双闸机过安检

所以这个只有在0->1跳变的一瞬间才会选择D的数据输出Q

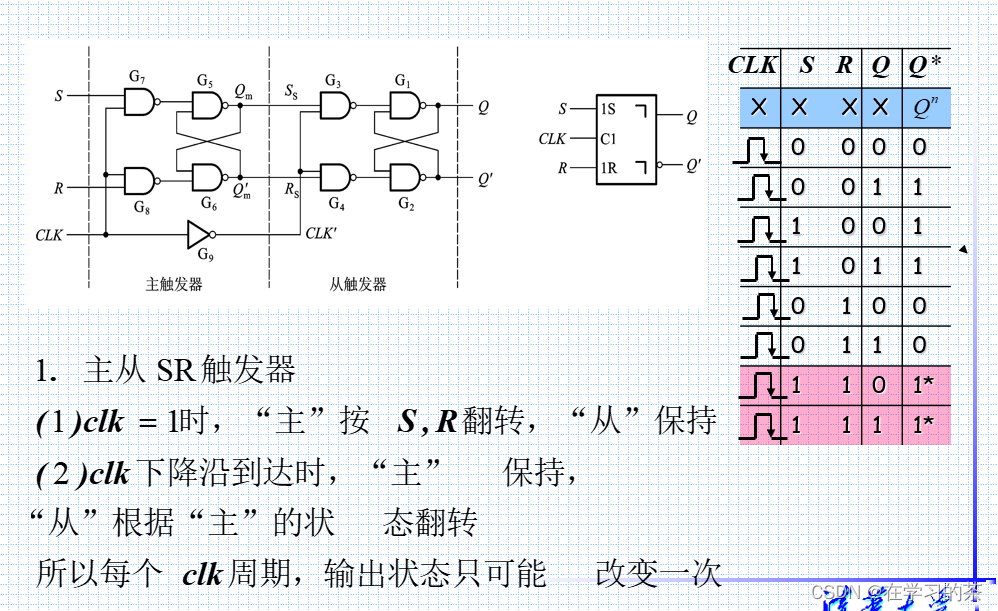

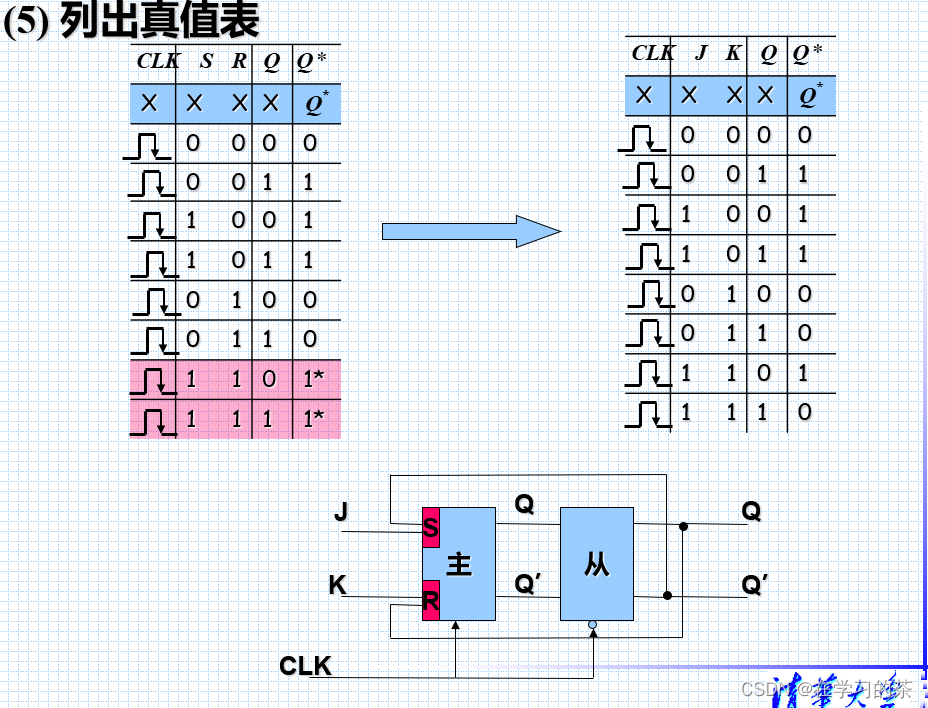

这个就是主从触发器!

简图只画了左边的触发器,因为已经够了

注意,当SR=0的时候,Q应该保持Qm的值!!分析得出

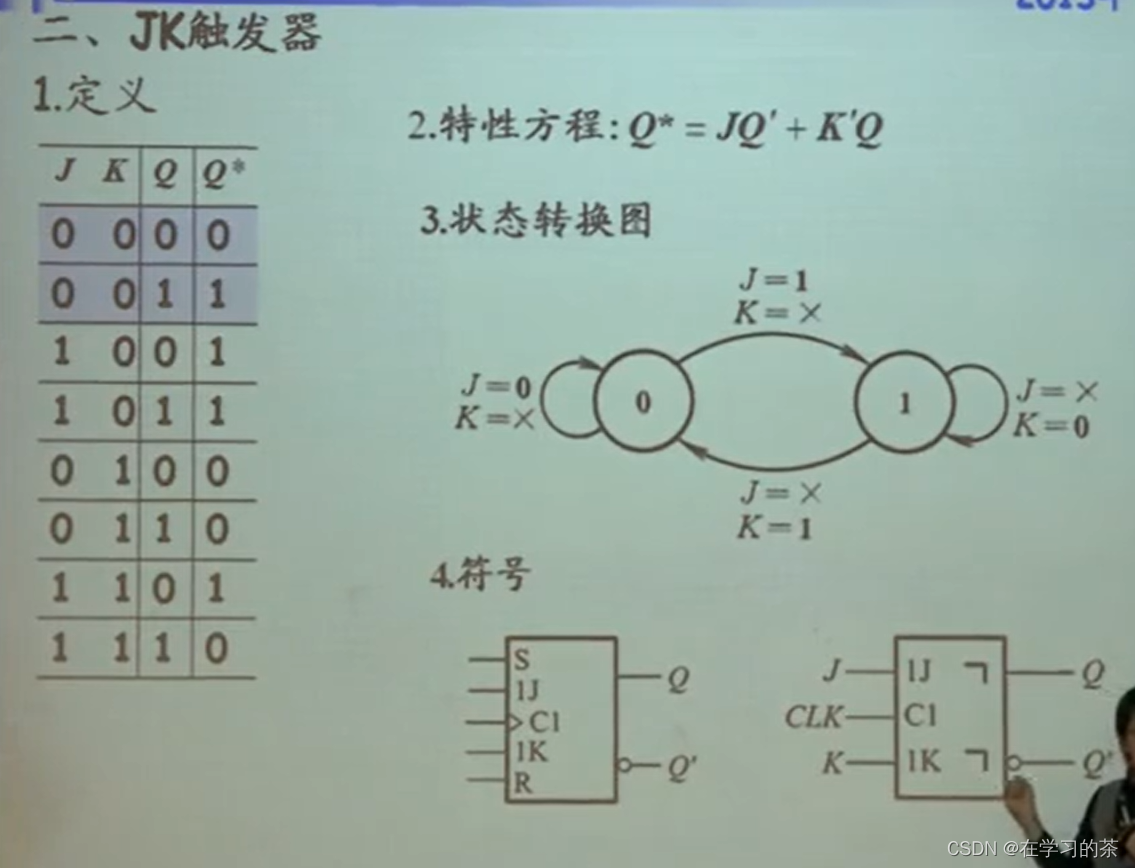

上图是除了D触发器,其他的解除约束的触发器,解除同为1的乱蹦约束

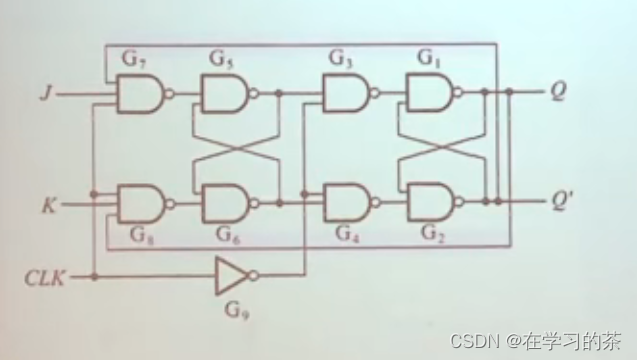

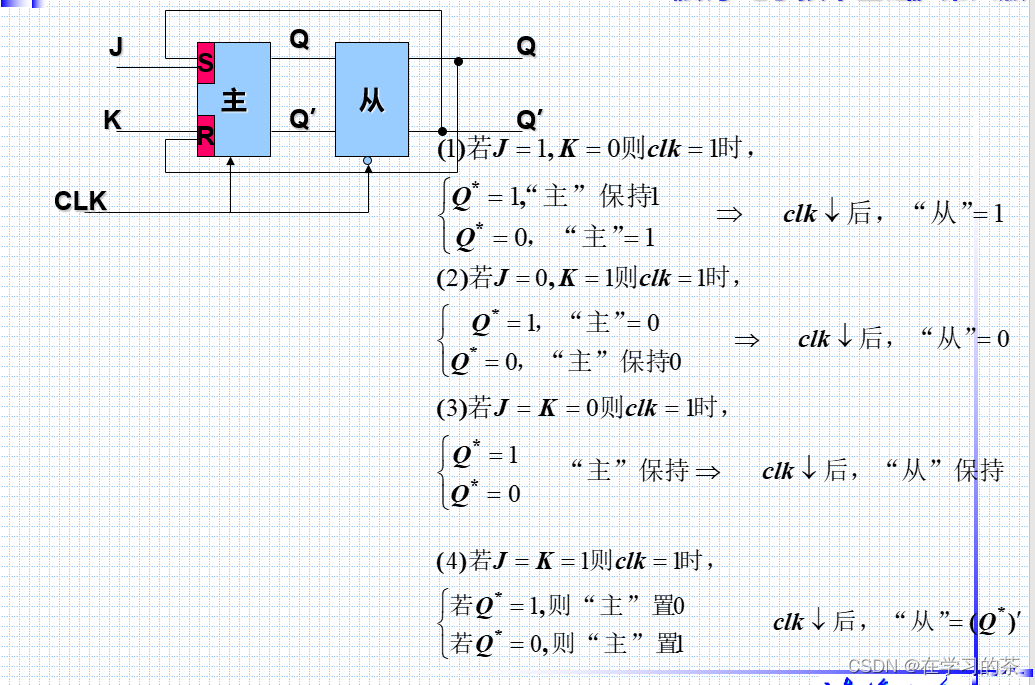

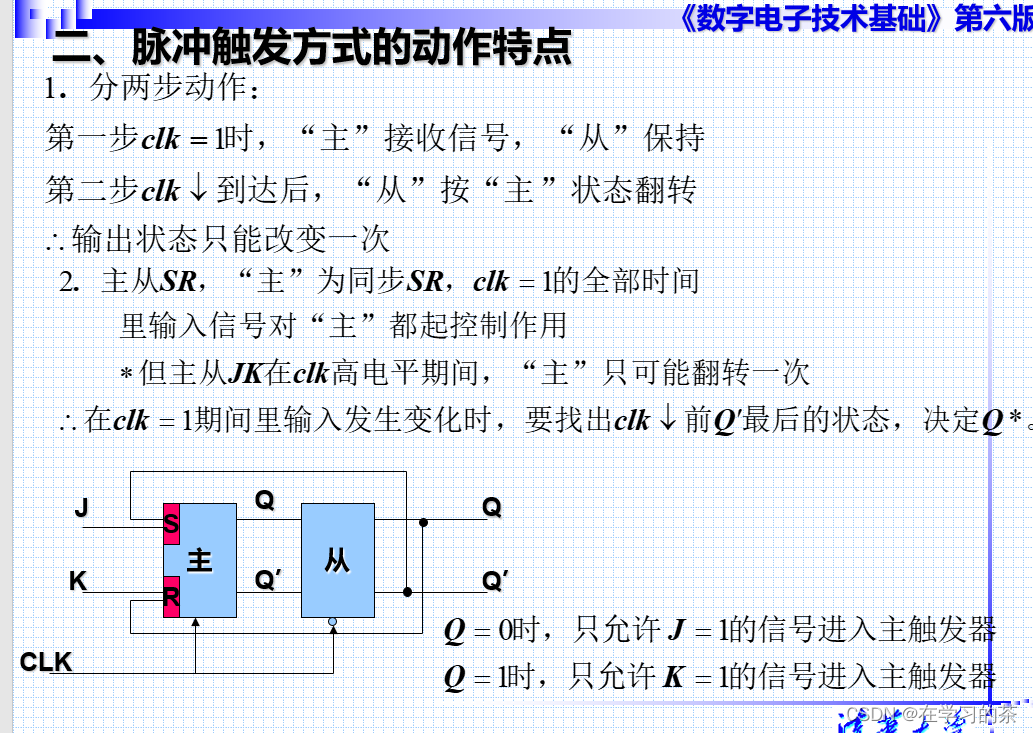

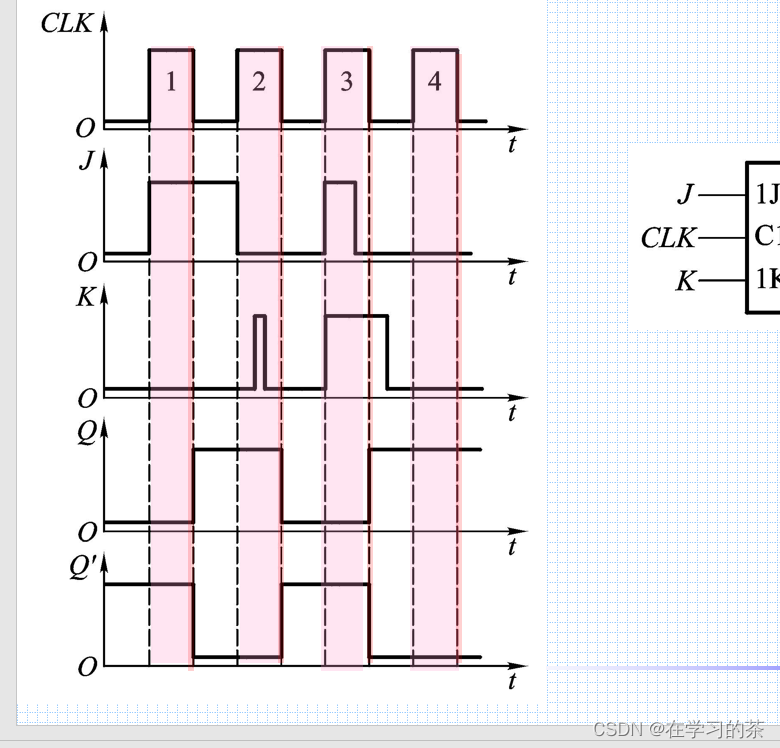

注意这个第(4)条,Q*=1,那么在跳变之前,Q*会反馈到K,相当于JK触发器的Qn-1,那么主触发器置为0。跳变之后从触发器在Q*=1的时候,接受01,那么从输出01。

注意,主触发器打开期间,主触发器的输出最多只能翻转一次

再次强调,这个翻转指的是主触发器的输出端的翻转。具体原因还是(4)的分析

注意,翻转一次是JK主从的特点,

这里面3好CLK的意思就是 之前JK=11,Q相当于取反,但是最后又变成JK=01了,因为主触发器不可以变两次的约束,只能取第一个变化的结果作为从触发器的输出

这么说,主从JK触发器会因为电路的脉冲干扰产生非法输出(如2、3CLK),这就产生了边缘触发器

主从D触发器

边缘上升沿

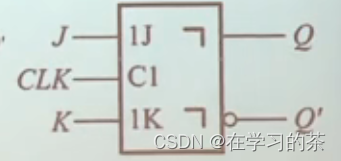

表示边缘触发,边沿触发符号三角形不带圈为上升沿,带圈为下降沿。三角符号和两个垂直符号不能同时出现,前者为边沿触发,后者为脉冲触发

如果三角符号前面没有圈,那么三角符号为上升沿,与脉冲触发上升沿要带圈不一样

边缘下降沿

上升沿

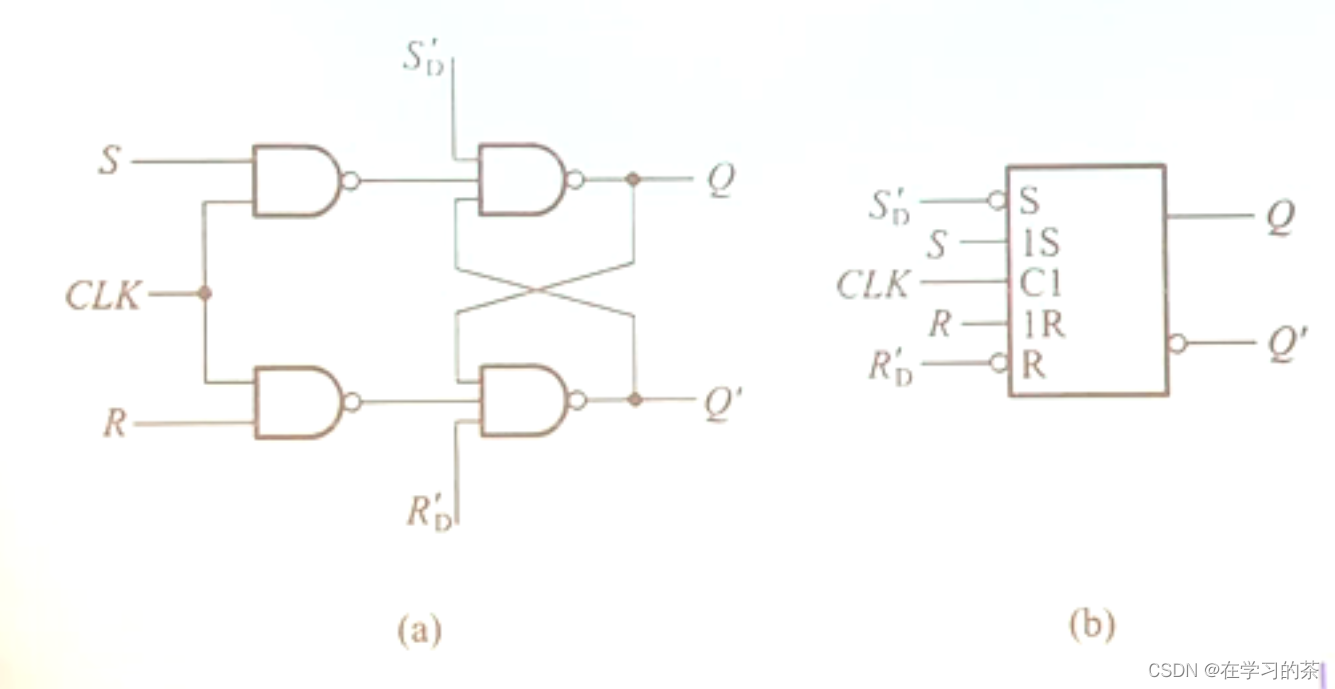

改进的SR主从触发器

改进的SR主从触发器

这里信号把主从部分都改变了,目的是防止后半段SR撤离时,继续从老版的主触发器取值,当我都改了之后,就算断电也不会拿老版的主触发器,因为主触发器已经更新

特征定义

其中状态转移图FSM和符号是必不可少的

符号代表触发器的类型,如现在的脉冲触发SR,在FSM中暗含了现态和次态

比如这张图,前一个符号我们查表只需要看上升沿的跳变,而第二章图要具体分析!!

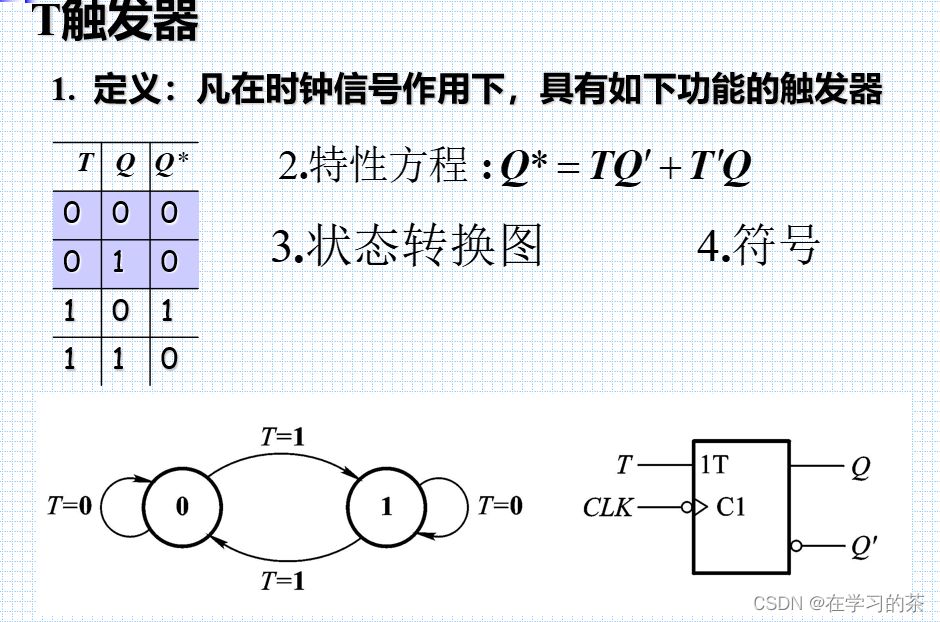

T触发器可以由J-K触发器的J,K输入端与T输入端相连得到

T触发器逻辑功能为:当T=0时,触发器状态不变Qn+1=Qn;而当T=1时,在脉冲有效边沿到来时翻转。

当T接1时,Clk的频率是Q的两倍,T触发器常用作二分频计数器,二进制计数的最低位,记得是Clk的个数

在一个clk周期Q维持一个电平,再下一个周期Q变成下一个相反电平

4753

4753

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?