目录

- 1.硬件设计定义说明(Hardwave Design Specification)

- 2.模块设计以及IP复用(Module Design & IP Reuse)

- 3.顶层模块集成(Top Level Integration)

- 4.前仿真(Pre-layout Simulation)

- 5.逻辑综合(Logic Synthesis)

- 6.版图布局规划(Floorplan)

- 7.功耗分析(Power Analysis)

- 8.单元布局和优化(Placement & Optimization)

- 9.静态时序分析(STA,Static Timing Analysis)

- 10.形式验证(Formal Verification)

- 11.可测试性电路插入(DFT,Dseign for Test)

- 12.时钟树综合(Clock Tree Synthesis)

- 13.布线设计(Routing)

- 14.寄生参数提取(Parasitic Extraction)

- 15.后仿真(Post_layout Simulation)

- 16.ECO修改(ECO,Engineering Change Order)

- 17.物理验证(Physical Verification)

简介:

SOC设计是从整个系统的角度触发,把处理机制、模型算法、芯片架构、各层次电路直至器件的设计紧密结合起来。SOC芯片设计是以IP核为基础,以分层次的硬件描述语言为系统功能和架构的主要描述手段,并借助于EDA工具进行芯片设计的过程。

SOC芯片设计步骤,主要包括模块定义、代码编写、功能及性能验证、综合优化、物理设计等环节。

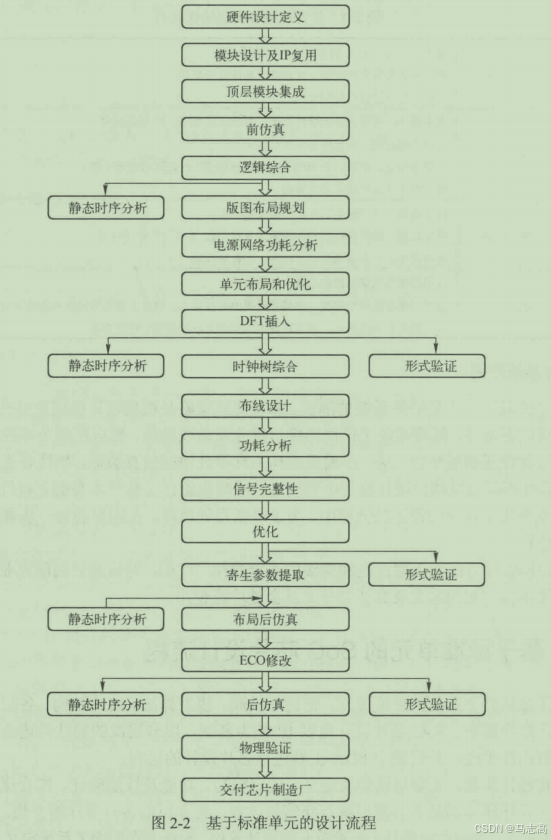

下图所示为一个较为详细的基于标准单元的设计流程,设计者在明确了系统定义和芯片定义后,了解了包括芯片的架构和电气特性的规格说明,以及设计周期、进度、人力资源管理等,就可以进行详细的硬件设计了。架构的规格说明定义了电路要实现的功能及具体实现的芯片上的架构,如核、总线、内存、接口等;电气的规格说明包括环境所能容忍的电压范围、直流特性、交流特性等。设计周期、进度和人力资源安排等则是关系到产品成败是否的关键,这是因为目前电子产品的市场生命周期越来越短,需要迅速退出自己的产品来抢占市场。

从硬件设计的角度来说,在保证功能正确的前提下,芯片面积、速度、功耗、可测性以及可靠性是衡量一块芯片成功与否的重要技术指标。在设计的各个步骤都应该考虑到这些,进而减少设计过程中的迭代次数,缩短设计周期。

1.硬件设计定义说明(Hardwave Design Specification)

硬件设计定义说明描述芯片总体架构、规格参数、模块划分、使用的总线,以及各模块的详细定义等。

2.模块设计以及IP复用(Module Design & IP Reuse)

模块设计及IP复用是根据硬件设计所划分出的功能模块,确定需要重新设计的部分以可复用的IP核。IP核可自主研发或者购买其他公司的IP。目前,设计的输入是采用硬件描述语言(HDL),如verilog或VHDL,所以,数字模块的实际通常称为RTL代码编写。

3.顶层模块集成(Top Level Integration)

顶层模块集成将各个不同的功能模块,包括新设计的与复用的整合在一起,形成一个完整的设计。通常采用硬件描述语言对电路进行描述,其中需要考虑系统时钟/复位、I/O环等问题。

4.前仿真(Pre-layout Simulation)

前仿真也叫RTL级仿真,功能仿真。通过HDL仿真器验证电路逻辑功能是否有效,即HDL描述是否符合设计所定义的功能期望。在前仿真时,通常与具体的电路版图实现无关,没有时序信息。

5.逻辑综合(Logic Synthesis)

逻辑综合是指使用EDA工具把硬件描述语言设计的电路自动转换成特定工艺下的网表(Netlist),即从RTL级的HDL描述通过编译产生符合约束条件的焖鸡网表。网表是一种描述单元和它们之间互连的数据文件。约束条件包括时序、面积和功耗约束。其中,时序是最复杂和最关键的约束,决定了整个芯片的性能。在综合过程中,EDA工具会根据约束条件对电路进行优化。

6.版图布局规划(Floorplan)

版图布局规划完成的任务是确定设计中各个模块在版图的位置,主要包括:

- I/O规划,确定I/O的位置,定义电源和接地口的位置;

- 模块放置,定义I/O的位置,定义电源和接地口的位置;

- 供电设计,设计整个版图的供电网络,基于电压降(IR Drop)和电迁移进行拓扑优化。

版图布局规划挑战是在保证布线能够走通且性能允许的前提下,如何最大限度地减少芯片面积,是物理设计过程中需要设计者付出最大努力的地方之一。

7.功耗分析(Power Analysis)

在设计中的许多步骤都需要对芯片功耗进行分析,从而决定是否需要对设计进行改进。在版图布局规划后,需要对电源网络进行功耗分析(PNA,Power Network Analysis),确定电源引脚的位置和电源线宽度。在完成布局布线后,需要对整个版图的布局进行动态功耗分析和静态功耗分析。除了对版图进行功耗分析以外,还应通过仿真工具快速计算动态功耗,找出主要的功耗模块和单元。这也是功耗分析的重要一步。

8.单元布局和优化(Placement & Optimization)

但愿布局和优化主要定义每个标准单元(Cell)的摆放位置和根据摆放的位置进行优化。现在,EDA工具广泛支持物理综合,即布局和优化与逻辑综合统一起来,引入真实的连线信息,减少了时序收敛所需要的迭代次数。

9.静态时序分析(STA,Static Timing Analysis)

静态时序分析技术是一种穷尽分析方法。它通过对提取的电路中所有路径上的延迟信息的分析,计算出信号在时序路径上的延迟,找出违背时序约约束的错误,如建立时间(Setuo Time)和保持时间(Hold Time)是否满足要求。静态时序分析的方法不依赖于激励,而且可以穷尽所有路径,运行速度快,占用内存少。它完全克服了动态时序验证的缺陷,是SOC设计中重要的一个环节。在后端设计的许多步骤完成后需要进行静态时序分析,如在逻辑综合完成之后、在布局优化之后、在布线完成后等。

10.形式验证(Formal Verification)

这里所指的形式是逻辑功能上的等效性检查。这种方法与动态仿真最大的不通电在于不需要输入测试向量,而根据电路的结构判断两个设计在逻辑功能上是否相等。在整个设计流程中会多次引入形式验证用于比较RTL代码之间、门级网表与RTL代码之间,以及门级网表之间在修改之前与修改之后功能的一致性。形式验证与静态时序分析仪器,构成设计的静态验证。

11.可测试性电路插入(DFT,Dseign for Test)

可测性设计师SOC设计中重要的一步,通常,对于逻辑电路采用扫描连的可测试性结构,对于芯片的输入/输出端口采用边界扫描和可测试结构。基于思想通过插入扫描链,增加电路内部节点的可控性和可观察性,以达到提高测试效率的目的。一般在逻辑综合或物理综合后进行扫描电路的插入和优化。

12.时钟树综合(Clock Tree Synthesis)

SOC设计方法强调同步电路的设计,即所有的寄存器或一组寄存器是否由同一个时钟的同一个边沿驱动的。构造芯片内部全局或局部平衡的时钟链的过程称为时钟树综合。分布在芯片内部寄存器与时钟的驱动电路构成了一种树状结构,这种结构称为时钟树。时钟树综合是在布线设计之前进行的。

13.布线设计(Routing)

这一阶段完成所有节点的连接。布线工具通常将布线分为两个阶段:全局布线与详细布线。在布局之后,电路设计通过全局布线决定布局的质量及提供大致的延时信息。如果单元布局的不好,全局布线将会花上远比单元布局多得多的时间。不好的布局同样会影响设计的整体时序。因此,为了减少综合到布局的迭代次数及提高布局的质量,通常在全局布线之后要提取一次时序信息,尽管此时的时序信息没有详细布线之后得到的准确。得到的时序信息将被反标(BackAnnotation)到设计网表上,用于做静态时序分析,只有当时序得到满足时才进行到下一阶段。详细布线是布局工具做的最后一步,在详细布线完成之后,可以得到精确的时序信息。

14.寄生参数提取(Parasitic Extraction)

寄生参数提取是提取版图上内部互连所产生的寄生电阻和电容值。这些信息通常会转换成标准延迟的格式被反标回设计,用于做静态时序分析和后仿真。

15.后仿真(Post_layout Simulation)

后仿真也叫门级仿真、时序仿真、带反标的仿真,需要利用在布局布线后获得的精确延迟参数和网表进行仿真,验证网表的功能和时序是否正确。后仿真一般使用标准延迟(SDF,Standard Delay Format)文件来输入延迟信息。

16.ECO修改(ECO,Engineering Change Order)

ECO修改是工程修改命令的意思,这一步实际上是正常设计流程的一个例外。当在设计的最后阶段发现个别路径有时序问题或逻辑错误时,有必要对设计进行小范围的修改和重新布线,ECO修改只对版图的一小部分进行修改而不影响到芯片其余部分的布局布线,这样就保留了其他部分的时序信息没有改变。在大规模的IC设计中,ECO修改是一种有效、省时的方法,通常会被采用。

17.物理验证(Physical Verification)

物理验证是对版图的设计规则检查(DRC,DesignRule Check)及逻辑图网表和版图网表比较(LVS,Layout Vs.Schematic)。DRC用以保证制造良率,LVS 用以确认电路版图网表结构是否与其原始电路原理图(网表)一致。LVS可以在器件级及功能块级进行网表比较,也可以对器件参数,如 MOS 电路沟道宽/长、电容/电阻值等进行比较。

在完成以上步骤之后,设计就可以签收、交付到芯片制造厂(Tape Out)了。在实际的 IC 设计中,设计工程师将依赖 EDA 工具完成上述各步骤。不同的 EDA 厂商通常会结合自己的 EDA 工具特点提供设计流程,但这些设计流程大体上是一致的。随着工艺尺寸的不断减小,新一代的 EDA 工具将出现,新的设计流程也将出现用于解决新的问题。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?