在这个项目中,将构建简单的有限状态机 (FSM)。 有限状态机是系统的数学抽象,它可以在给定时间恰好处于有限状态之一,并且可以使用适当的输入信号将状态从一个状态更改为另一个状态(状态转换)。 状态是对系统状态的描述,该系统正在等待某个触发器来执行从一个状态到另一个状态的转换。

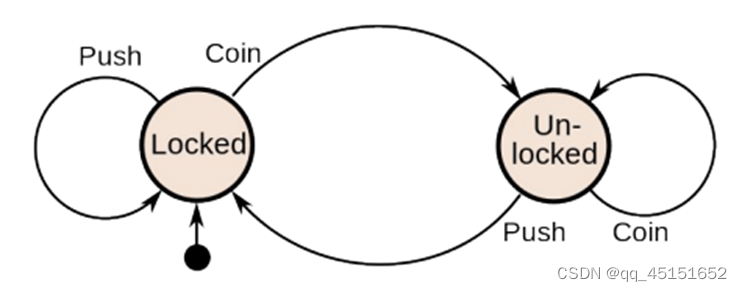

FSM 可以使用“状态图”来描述——这是一个有向图,其中包含状态以及这些状态之间的转换。 具有两个状态的 FSM 最简单的例子之一是十字转门。 在旋转门的输入槽中投入硬币可解锁臂(状态“解锁”)。 顾客通过后,手臂被锁定,直到插入另一枚硬币(状态“锁定”)。

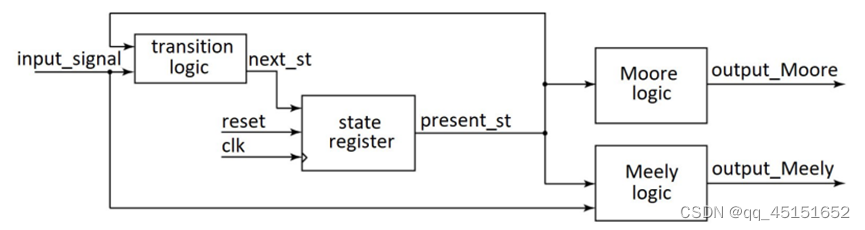

有两种流行的 FSM 实现:Moore FSM(输出仅取决于当前状态)和 Mealy FSM(输出取决于当前状态和输入信号)。 典型 FSM 的流程图如图 2 所示。它由转换逻辑、状态寄存器(更新当前状态)和解码逻辑组成。

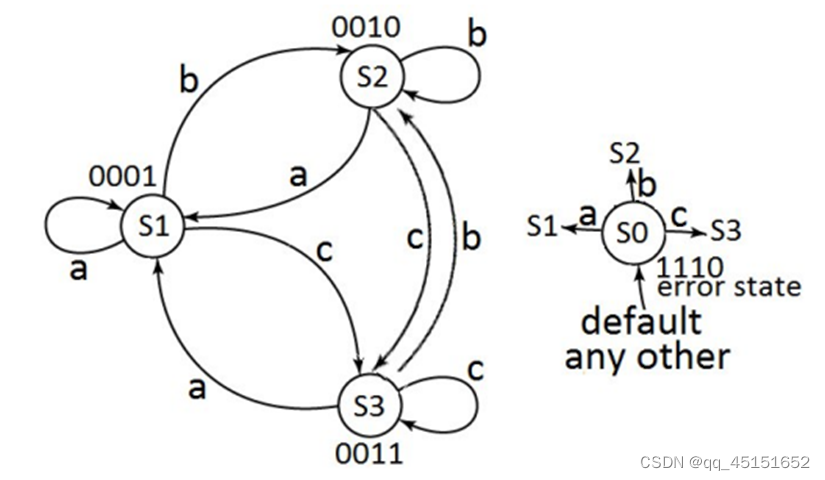

在我们的项目中,将描述简单的 Moore FSM。 设计的 FSM 的状态图如图 3 所示。应该注意的是,我们将为未声明的状态、转换或输入信号添加额外的 ERR_STATE(参见下面的 Verilog 代码)。 只采用逻辑综合,没有映射和拟合到 FPGA 中。

FSM.v

`timescale 1ns / 1ps

module FSM(clk,reset,abc,state_out);

input wire clk,reset;

input wire [2:0] abc;

output reg [3:0] state_out;

localparam STATE_1 = 2’d1;

localparam STATE_2 = 2’d2;

localparam STATE_3 = 2’d3;

localparam ERR_STATE = 2’d0;

reg [1:0] present_state;

reg [1:0] next_state;

always @()

begin

case(present_state)

STATE_1:

begin

case(abc)

(3’b100): next_state = STATE_1;

(3’b010): next_state = STATE_2;

(3’b001): next_state = STATE_3;

//default: next_state = ERR_STATE;

endcase

end

STATE_2:

begin

case(abc)

(3’b010): next_state = STATE_2;

(3’b100): next_state = STATE_1;

(3’b001): next_state = STATE_3;

//default: next_state = ERR_STATE;

endcase

end

STATE_3:

begin

case(abc)

(3’b001): next_state = STATE_3;

(3’b010): next_state = STATE_2;

(3’b100): next_state = STATE_1;

//default: next_state = ERR_STATE;

endcase

end

ERR_STATE:

begin

case(abc)

(3’b001): next_state = STATE_3;

(3’b010): next_state = STATE_2;

(3’b100): next_state = STATE_1;

//default: next_state = ERR_STATE;

endcase

end

//default:

//next_state = ERR_STATE;

endcase

end

//state register

always @(posedge clk)

if (reset)

present_state <= ERR_STATE;

else

present_state <= next_state;

//output state decoder

always @()

begin

case(present_state)

STATE_1: state_out = 4’d1;

STATE_2: state_out = 4’d2;

STATE_3: state_out = 4’d3;

//ERR_STATE: state_out = 4’d14;

default: state_out = 4’d14;

endcase

end

endmodule

FSM_TB.v

`timescale 1ns / 1ps

module FSM_TB;

// Inputs

reg clk;

reg reset;

reg [2:0] abc;

// Outputs

wire [3:0] state_out;

// Instantiate the Unit Under Test (UUT)

FSM uut (

.clk(clk),

.reset(reset),

.abc(abc),

.state_out(state_out)

);

initial

begin

// Initialize Inputs

clk = 0;

reset = 1;

abc = 0;

// Wait 2 ns for global reset to finish

#20;

reset = 0;

//terminate simulation after 100ns

#100 $finish;

end

//Add stimulus here

initial forever

#1 clk = ~clk;

always @(posedge clk)

begin

abc <= abc +3’d1;

$display("time = %d,reset = %b,abc = %b,state_out = %d,",$time,reset,abc,state_out);

end

endmodule

然后看RTL,Technology Schematic图,以及Simulation里的simulate Behavioral Model。

问题:

1、为什么用localparam语句而不是parameter语句? 我们如何使用单热状态编码在 Verilog 中描述这个 FSM?

2. 尝试注释“ERR_STATE”case 语句并模拟设计。 为什么我们会得到这些结果? 请画出获得的 FSM 的状态图。

7918

7918

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?