IP Catalog:属于数电中的功能块集成,在进行FPGA设计时可直接调用。用于产品应用专用集成电路(ASIC)或者可编辑逻辑器件(FPGA)的逻辑块或数据块,是一种知识产权核。

基于Vivado应用IP核进行了三个小项目的实践工作,其中包括IP核中的MMCM/PLL、RAM和FIFO,了解IP核的具体使用,并获悉Testbench仿真的编写、ILA调式的使用等!Let’s go ahead.

一、IP核之MMCM/PLL实验

PLL(Phase Locked Loop):锁相环,是一种反馈控制电路,能够对时钟网络进行系统级的时钟管理和偏移控制。特点:能够利用外部输入信号控制环路内部震荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪。

锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

MMCM:混合模拟时钟管理器,MMCM功能是PLL的超集,在PLL的基础上可以实现动态调整,动态的实现与AXI4的接口协议有关;PLL 是模拟的,而动态调相是数字电路,所以称为混合模式。

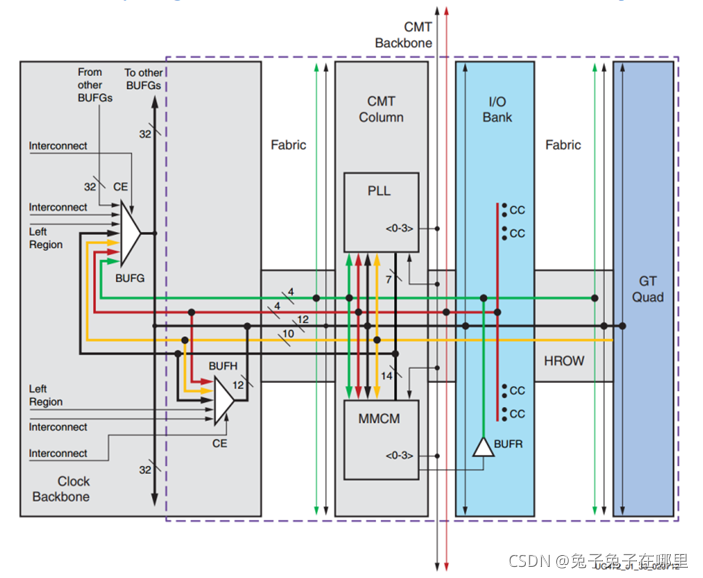

图1:BUFG/BUFH/CMT 在一个时钟区域内的连接

(BUFG:全局时钟 BUFR:区域时钟,控制部分区域的资源 CMT:内部包括PLL和MMCM可以发生分频和倍频)

读者可以简单地理解为:外部时钟连接到具有时钟能力的输入引脚 CCIO(Clock-Capable

Input),进入 MMCM/PLL,产生不同频率和不同相位的时钟信号,然后驱动全局时钟资源 BUFG。但是要进行更深入的 FPGA 开发,就必须理解器件的时钟资源架构。

实践项目:基于Zynq-7010,利用IP核生成不同频率和相位的时钟驱动Led灯

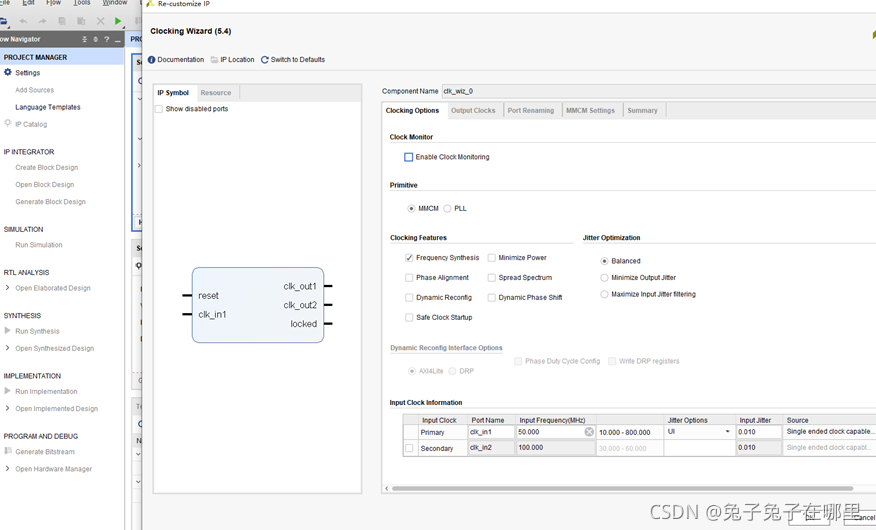

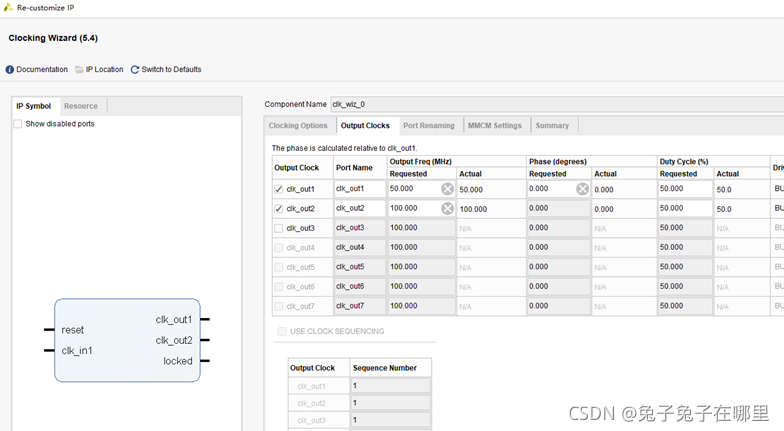

step1:IP核Clock设置

step2:顶层文件——功能设计

`timescale 1ns / 1ps

module top(

input wire clk, //时钟

input wire rst_n, //复位

output reg [1:0] led

);

//=====================================

//parameter define

//=====================================

parameter cnt_max = 50_000_000-1;

//======================================

//internal signals:为两个led设置两个计时器,定义一个锁存线和两个时钟脉冲输出

//======================================

reg [27:0] timer1;

reg [27:0] timer2;

wire locked;

wire clk_50m;

wire clk_100m_90deg;

//-------------timer1-------------------

always @(posedge clk_50m or negedge rst_n)

begin

if(rst_n == 1'b0)begin

timer1 <= 'd0;

end

else if(locked == 1'b1)begin //加上Ip核后,要明白clocking含有一个锁存器PLL,明白这里加上locked的作用

if(timer1 == cnt_max)

timer1 <= 'd0;

else

timer1 <= timer1 + 1'b1;

end

本文介绍了基于Vivado的FPGA开发中,如何利用IP核进行MMCM/PLL时钟生成、RAM双端口操作和异步FIFO的实践。详细阐述了锁相环的工作原理、RAM的类型以及FIFO在跨时钟域数据传递的作用,并提供了实际操作步骤和注意事项。

本文介绍了基于Vivado的FPGA开发中,如何利用IP核进行MMCM/PLL时钟生成、RAM双端口操作和异步FIFO的实践。详细阐述了锁相环的工作原理、RAM的类型以及FIFO在跨时钟域数据传递的作用,并提供了实际操作步骤和注意事项。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7039

7039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?