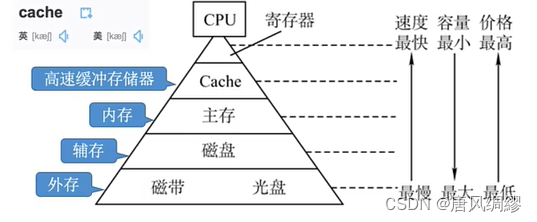

存储器层次化结构

内存及其以上的部分可以直接被CPU访问

内存及其以上的部分可以直接被CPU访问

寄存器如加法、乘法寄存器

例:微信的各种代码程序存储在辅存,要运行时将微信程序复制到主存,假设微信语音功能经常被用到,则该功能会复制到高速缓冲区以便更快速的调用。

存储器分类:

按存储介质分类:半导体存储器(如主存、高速缓存);磁表面~(磁带);光~(光盘)

按存取方式分类:随机存取存储器(类比链式存取);顺序~(磁带);直接存取~(随机+顺序:唱片原理);相连~(按内容访问存储器:通过内容找到存储位置)

按信息更改性:只读存储器;读写存储器

按信息可保存性:易失性/非易失性存储器(断电存储信息消失);破坏性/非破坏性~(读出数据后原存储信息被破坏)

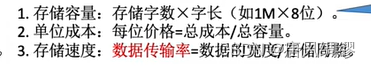

存储器性能指标:

存储时间和存储周期是不同的:

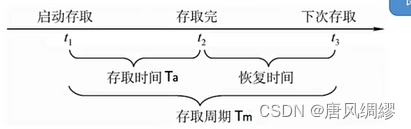

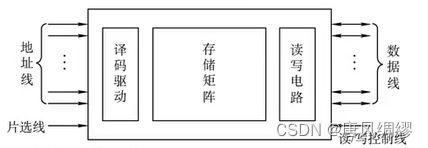

主存储器的基本组成:

存储器由存储体,MAR,MDR组成

存储体由若干存储字/存储单元组成,每个存储单元由若干存储元组成,一个存储元存一个0/1

电容用于存储信息,MOS管是读取该存储元信息的开关。将一排存储元用一条电路(字选择线)串联记为一个存储字,通电时同时可读出一个存储字中的信息(01数据从绿色的数据线流出)。(存储字的长度不固定,取决于硬件设计;而1字节(B)固定为8bit。别记混了)

片选线:一个内存条有多个存储芯片构成

片选线:一个内存条有多个存储芯片构成

读写控制线(一根或两根):控制当前读出 或写入数据

每个箭头对应一个金属引脚;读写控制线对应一个或两个

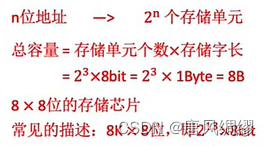

存储容量:

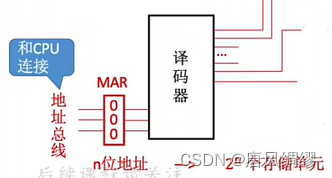

地址线用法:

译码器输入二进制地址,每个地址对应一个输出,通过这种方法,每个地址都对应一个存储单元

译码器输入二进制地址,每个地址对应一个输出,通过这种方法,每个地址都对应一个存储单元

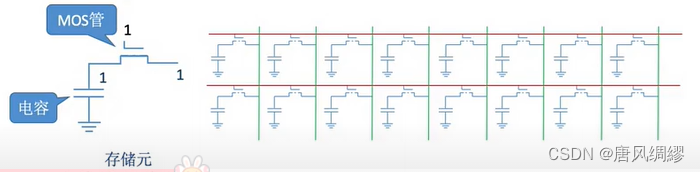

RAM随机存取存储器:

DRAM和SRAM最主要的区别在于:存储元不同

DRAM(已过时,逐渐淘汰):栅极电容

上面讲的就是DRAM

破坏性读出;每次读出需要重写;读写速度慢;成本低;存储元体积小集成度高

常用作主存

需要刷新(电容中的电荷会不断流失,需要给电容充电)

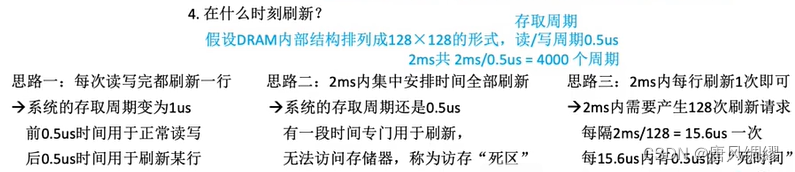

DRAM的刷新:刷新频率:2ms;

每次刷新多少存储单元:一行

一行:为了减少译码器输出的选通线,存储单元有行地址和列地址

如何刷新:有硬件支持,读出一行信息后重新写入占用1个读/写周期

地址线复用技术:一根地址线同时用于发送行列地址,分不同时间发送

考引脚个数是要注意复用技术使引脚数减半(因为地址线减半)

二 者都是易失性存储器(断电则信息消失)

SRAM:双稳态触发器

非破坏性读出;读写速度快;成本高,存储元体积大(需要6个MOS管)集成度低

常用作cache(高速缓冲存储器)

不需要刷新(只要连接电源,电荷就不会消失)

行列地址同时发送,因为SRAM集成低,容量小,地址少,不需要过多的地址线,所以没必要用地址线复用技术

只读存储器:ROM

非易失性存储器:断电信息不消失

MROM:信息由厂家写入,任何人不能重写(超级只读)

PROM:用户用专门的PROM写入器写信息,只能写一次

EPROM:允许用户写入信息,可以用某些方法擦除信息

Flash memory(闪速存储器):可多次快速写入擦除

SSD(固态硬盘): 可多次快速写入擦除,与闪速存储器核心区别在于控制单元不同

主存储器与CPU的连接

存储器的扩展

A:读入端 D:数据端

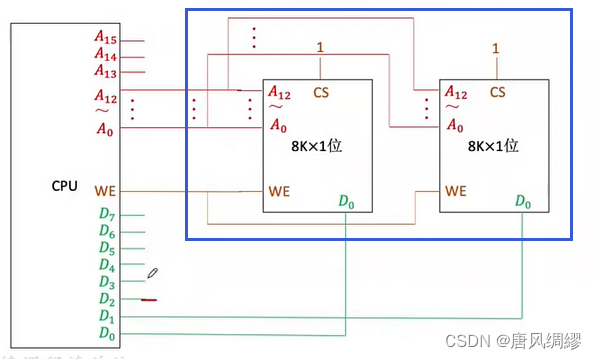

位扩展:

8k*1位的芯片不能成分利用CPU的D端接口,将两个芯片用图示的方法连接可以将内存扩大一倍,用此方法,这样的芯片可以接8个

8k*1位的芯片不能成分利用CPU的D端接口,将两个芯片用图示的方法连接可以将内存扩大一倍,用此方法,这样的芯片可以接8个

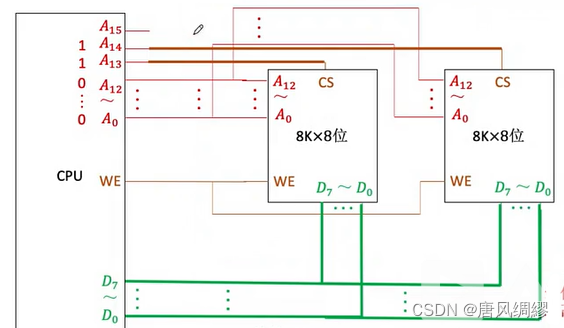

字扩展:线选法

8K*8的芯片不能充分利用CPU的A端接口,于是如图将A13,A14分别与芯片的CS相接通过控制13/14的0/1输入来控制读写哪个芯片的信息。该方法的弊端在于A13~15利用不充分,最多只能操控三个芯片

8K*8的芯片不能充分利用CPU的A端接口,于是如图将A13,A14分别与芯片的CS相接通过控制13/14的0/1输入来控制读写哪个芯片的信息。该方法的弊端在于A13~15利用不充分,最多只能操控三个芯片

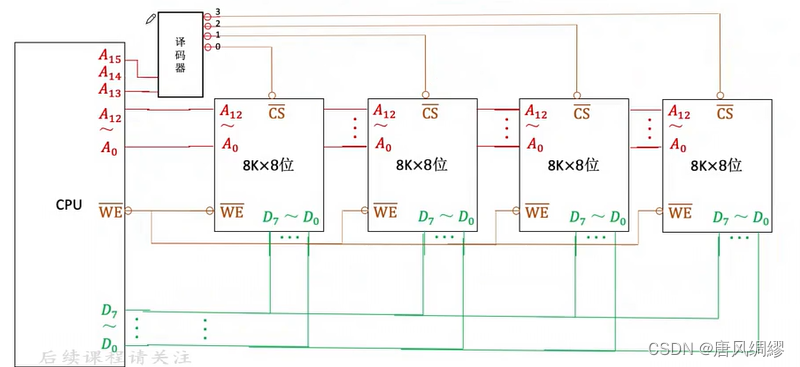

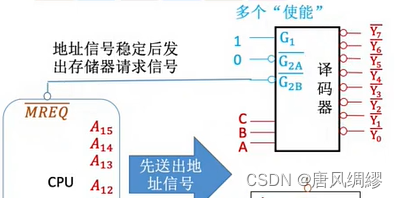

字扩展:片选法

通过 2-4译码器或3-8译码器可以充分利用A端,使地址空间连续

2-4译码器或3-8译码器可以充分利用A端,使地址空间连续

`C`S是指低电平有效,与CS高电平有效相对

![]() 低电平有效会在上面画个圈,上横线与小圆圈是表示同一个意思,不是取两次反!

低电平有效会在上面画个圈,上横线与小圆圈是表示同一个意思,不是取两次反!

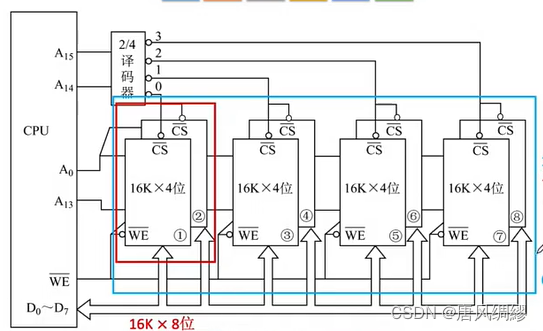

此图为字位同时扩展,就是单纯的两种方法同时使用

此图为字位同时扩展,就是单纯的两种方法同时使用

由CPU控制,使能端激活时,译码器才工作

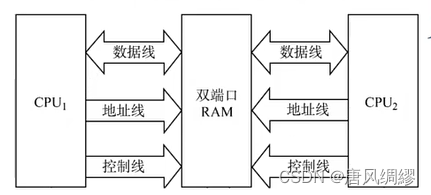

双端口RAM:

现在的CPU都是多核的,双端口RAM可以优化多核CPU访问一根内存条的速度

原理很简单:双端口RAM拥有两套数据线,地址线等

两端口可以同时对不同地址单元存取数据,对同一单元读出数据;

两端口可以同时对不同地址单元存取数据,对同一单元读出数据;

但对同一地址写数据会写入错误,一读一写会读出错误

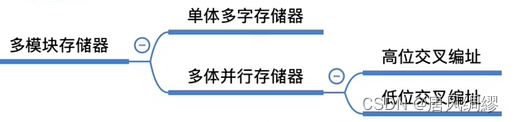

多模块存储器:内存由多个存储体组成

因为存储周期=存取时间+恢复时间。在恢复时间CPU不能再次访问内存,效率低

多体并行存储器:

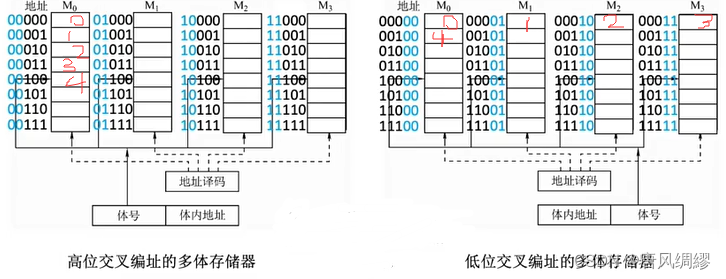

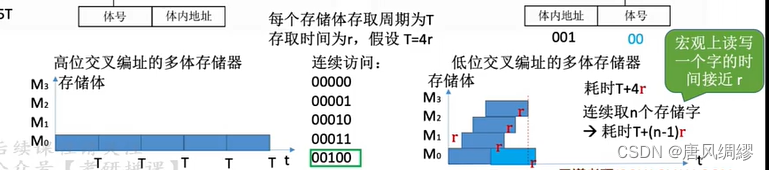

高位交叉编址存储器:将存储单元地址的高位作为体号,低位为体内地址

因此顺序地址是竖着排列的

连续访问时仍然要连续访问一块存储体,不能提高效率

低位交叉编址存储器:将存储单元地址的低位作为体号,高位为体内地址

顺序地址是横着排列的

连续访问时会依次、连续访问每个存储体,避免了恢复时间等待,提高了效率

几个存储体最合适:存储体数m>=T/r 若小于则需等待恢复时间,大于则存储体有空闲,等于时最佳 (注意,这里说的都是地址连续的存取)

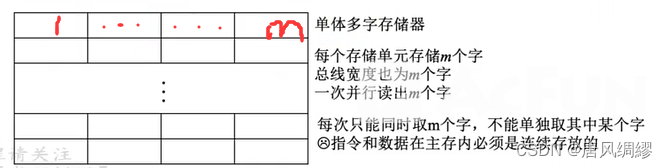

单体多字存储器:

将多个存储体合一,图为四合一,共用一套存取地址、地址线、数据线等

将多个存储体合一,图为四合一,共用一套存取地址、地址线、数据线等

灵活性差于多体并行,数据连续时效率高

35万+

35万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?