目录

一、I/O控制器的组成

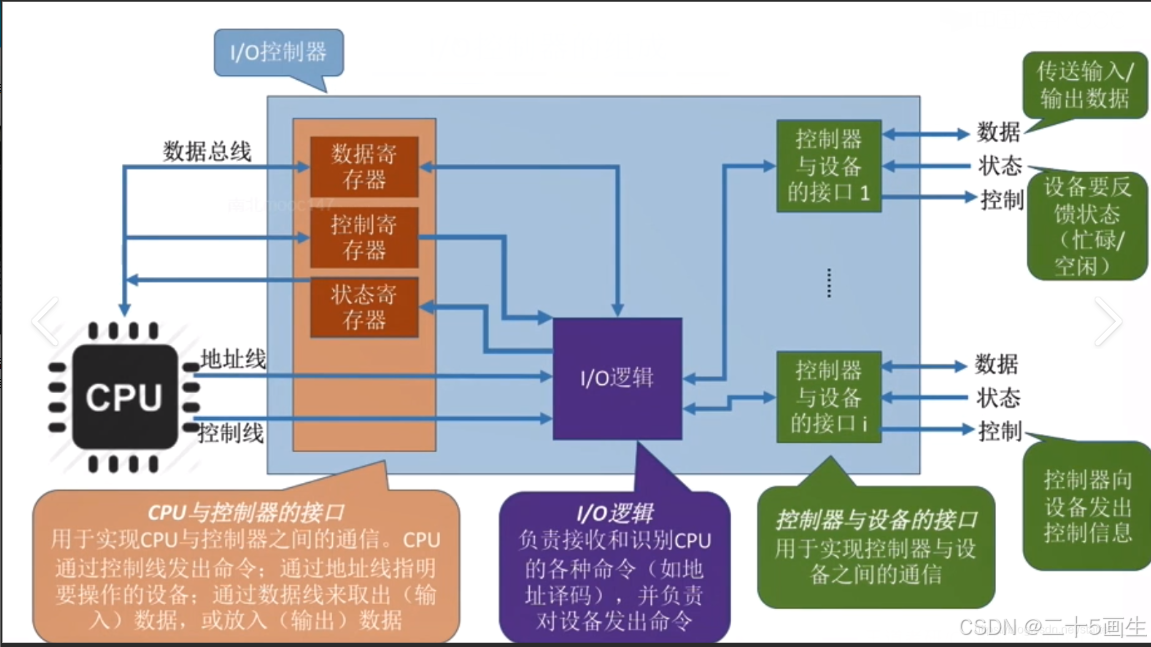

CPU接口 - I/O逻辑-设备接口(设备可以有多个,连接多个设备)

CPU接口:负责CPU和控制器的通信

I/O逻辑:负责识别CPU的命令,并负责对设备发出命令

设备接口:负责设备和控制器的通信

1、I/O控制器工作的过程

当CPU要对某个设备进行输出时,

首先使用地址线发送信息,指明要对哪个设备进行操作

使用控制线发送信息,指明要对设备做什么操作

再用数据总线,向控制器自带的数据寄存器输入数据

之后,I/O逻辑区就可以从数据寄存器中读取数据,将之发送到对应的设备中

同时,CPU在数据的传输过程中,还需有一些控制参数

这些参数发送给控制寄存器

同时,CPU为了及时实时掌握设备的状态,还通过状态寄存器读取各个设备的状态情况等信息

因此,各个设备还需将自己的状态不断的向状态寄存器写入,以便CPU读取

此外,由于控制器可以有多个设备接口

可是设备很多,不可能所有设备都共同使用一个控制器

因此,需要同时存在多个控制器,对不同的设备进行分别管理

有多个控制器,就有多个寄存器

这就涉及对寄存器进行编址以识别的问题

怎么编?

两种方式:内存统一编址和寄存器独立编址

2、寄存器的统一编址和独立编址

内存统一编址:

和内存一样的编址方式

例如内存的编址是从0-n个地址

设备控制器0:

寄存器0:地址为n+1

寄存器1:地址为n+2

寄存器2:地址为n+3

设备控制器1:

寄存器0:地址为n+3

寄存器1:地址为n+4

寄存器2:地址为n+5

….

所有寄存器按统一的顺序进行编排

以此类推

这种方式的优点是:

不需要单独设计专门的访问控制指令

只需要和内存访问指令一致就可以

寄存器独立编址:

设备控制器的三个寄存器:

寄存器0:0

寄存器1:1

寄存器2:2

设备控制器1的三个寄存器:

寄存器0:0

寄存器1:1

寄存器2:2

设备控制器2的三个寄存器:

寄存器0:0

寄存器1:1

寄存器2:2

每一个控制器内部独立的进行编址

如此类推

这种方式的缺点是:

需要设计单独的访问控制指令

因为在访问寄存器之前,

还需要指明到底是哪一个设备控制器的设备

二、I/O控制方式

有四种方式:程序直接控制、中断驱动、DMA、通道控制

1、程序直接控制方式:

1、读/写操作

(注意,首先要清晰设备控制器的各个部件结构和对应功能)

当要读一个设备时,

第一步,CPU向控制器发出读指令,设备启动,并且将设备状态寄存器设为1(表示忙碌)

可是,外部设备的数据传输速度很慢,因此

第二步,CPU不断的对设备状态寄存器进行轮询

如果设备状态寄存器一直是1,说明设备还在忙碌,数据还没有传输完,于是CPU等待

第三步,输入设备的数据传输完毕,并将设备状态寄存器设置为0,表示传输完毕

第四步,CPU检测到设备状态为0(表明已就绪),从数据寄存器读取数据,读到CPU自己的寄存器,再送到内存

2、CPU干预频率

很频繁,因为CPU需要不断的进行轮询

3、数据传输单位

一个字节

4、数据流向

读操作:I/O设备->CPU->内存

写操作:内存->CPU->I/O设备

5、优缺点

优点:简单,只需要写循环语句即可

缺点:CPU和I/O设备只能串行工作,且CPU利用率低

2、 中断控制

程序直接控制方式对于CPU利用率很低

因为CPU要一直等待设备

那可不可以不等?

可以,

这就是中断控制方式:

即不要让CPU去等设备

而是在设备比较忙的时候,去做别的事情

当设备完成时,再向CPU发出中断,

此时,CPU响应中断,再转回来处理事务

因此,CPU会在每个指令周期的末尾检查中断

(注意:每一个中断处理,只能从控制器读取一个字节的数据送到CPU寄存器,再写入内存

而后恢复中断,执行其他任务)

中断处理中,仅仅读取一个字节的数据!!!

务必注意!!!

因此,如果中断太多,CPU效率也会很低

1、读写操作

和程序直接控制方式一样

2、CPU干预频率

每次I/O操作开始前,完成后都需要CPU参与

等待过程中切换到其他任务

3、数据传送单位

每次读/写一个字节

4、数据流向

读操作:I/O设备->CPU->内存

写操作:内存->CPU->I/O设备

5、优缺点

优点:不需要轮询,效率更高,设备和CPU可以并行工作

缺点:每一次只能传输一个字节的数据,而且都需要CPU控制

频繁的中断处理消耗很大

3、DMA方式

中断处理克服了轮询的CPU效率低

可是每一次中断处理只能处理一个字节

效率实在是低

有没有什么新的方式,可以避免每一次CPU只能传送一个字节的数据?

可以不可以一次多传送几个数据呢?

答案是可以

这就是DMA方式,直接存储器方式

如何实现?

1、数据传送单位是”块“,即使用块设备

2、不需要CPU参与,设备和内存直通,直接抵达(用物理电线连接)

3、只有在数据传送的开始和结束时间才需要CPU干预

DMA通道模式结合了中断的优点

但CPU向设备读取数据时

过程和程序直接控制方式一样

但是,CPU不会等待,而是去执行其他任务

当设备完成数据传输,控制器向CPU发出中断,进行相关操作

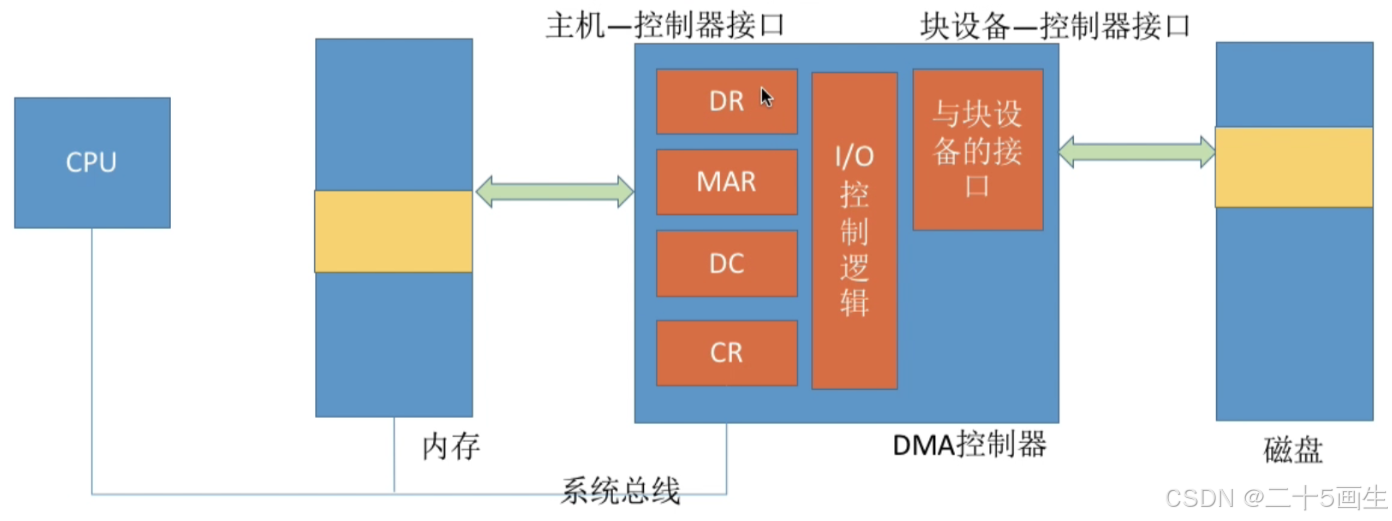

DMA控制方式,单独对应一个DMA控制器

其结构如下:

其中:

DR数据寄存器:暂存数据的地方

MAR内存地址寄存器:输入时,表示数据存放在内存什么位置;输出时,表示数据存放在外部设备的什么位置

DC数据计数器:指明需要读/写的数据字节数

CR命令/控制寄存器:存放CPU发出的I/O命令,或者设备状态信息

(注意:事实上,设备和内存之间的数据传输本质上还是一个字节一个字节的进行

这整个过程,都是通过DMA控制器进行的)

1、读写操作

和中断控制方式一样

2、CPU干预频率

仅仅在数据传送的开始和结束才需要CPU干预

3、数据传输单位

一个数据块/多个数据块

(注意:如果是多个数据块,则必须要求数据块连续,连续读,连续存,即不支持离散存取)

4、数据流向(不需要经过CPU)

因为在控制器和内存之间有直接的系统总线进行物理连接

因此,数据可以直接在设备和内存之间进行传输

读:I/O设备->到内存

写:内存->I/O设备

5、优缺点

优点:数据传输以块为单位,且CPU不需介入

数据传输效率提高,CPU效率提高,CPU和I/O设备并行性提高

缺点:每一次只能读/写一个或者多个连续的数据块

也就是说,不能读/写分散的数据块,或者将数据块存放到不同的位置,只能连续

如果要实现上述的操作,则只能CPU进行多次操作

4、通道控制方式

有缺点,就会有人改进

于是,为了克服DMA的不能离散存储的问题,

就有了一个新的控制方式:通道控制方式

1、读写操作

通道本质是一个硬件,可以理解为简单版CPU(通道=丐版CPU)

通道这个硬件可以识别并且执行一系列的通道指令

也就是说,在内存中会存在一个叫做通道程序的系列指令集合(通道程序=序列指令集合)

当CPU要对某个设备进行操作时

首先向通道发出指令,说明通道程序在哪里,要对哪个设备进行操作,而后CPU执行其他任务

剩下的事情交给通道来处理

此时通道已经知道通道程序在哪里,要操作哪个设备

剩下的,就是去调用通道程序即可

通道程序的信息有:读/写多少操作、读/写到哪里等信息

执行完毕通道程序后,向CPU发出中断信号

CPU介入处理,搞完撒花

注意:通道需要访问内存,因此通道和内存共享内存

2、CPU干预频率

很低,只有两个参与过程:

CPU发出指令,通道执行完后CPU处理中断

3、数据传输单位

每次读/写一组数据块

4、数据流向(通道控制)

读:I/O设备->内存

写:内存->I/O设备

5、优缺点

缺点:实现复杂,需要通道硬件支持

优点:CPU、I/O设备、通道而可并行过工作,资源利用率高

一个通道可以控制多个I/O控制器

一个I/O控制器可以控制多个设备

1959

1959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?