input delay 分析:

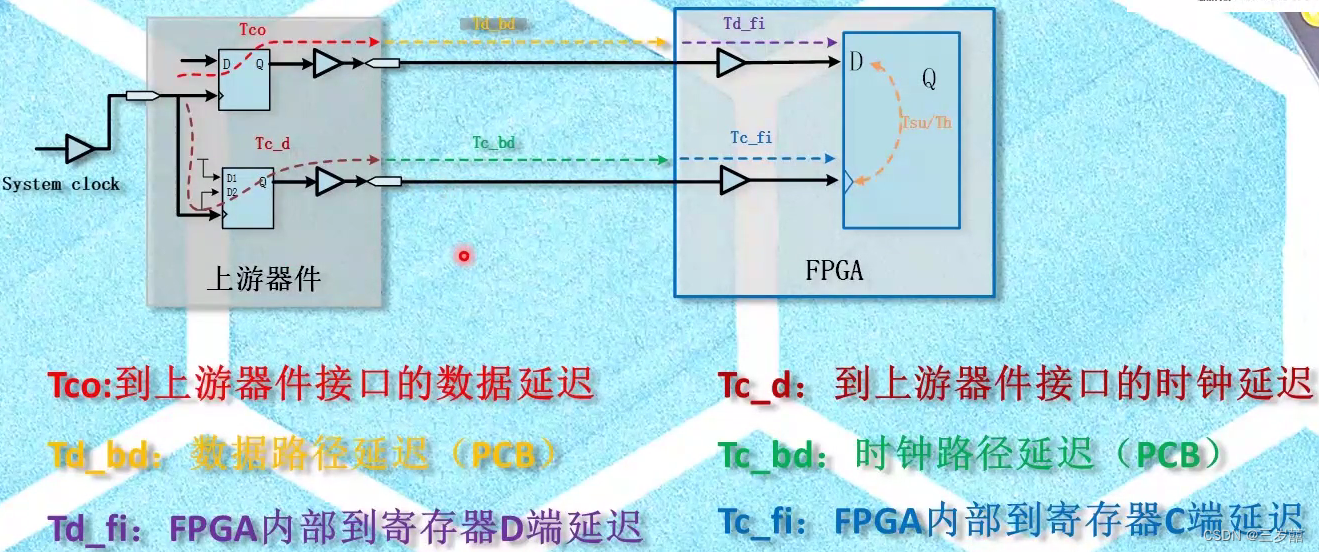

整个系统的电路时序分析图:

时序分析:

极限input delay(以系统为中心)

极限input delay即从发射沿(lunch edge) 开始,到FPGA内部寄存器接收所允许的最大延迟。此时间是针对整个系统进行分析,即整个系统不违例所允许的最大input delay。

此时Tsu_slack为0

极限input delay = Tcycle + Tc_d+Tc_bd+Tc_fi-Tsu

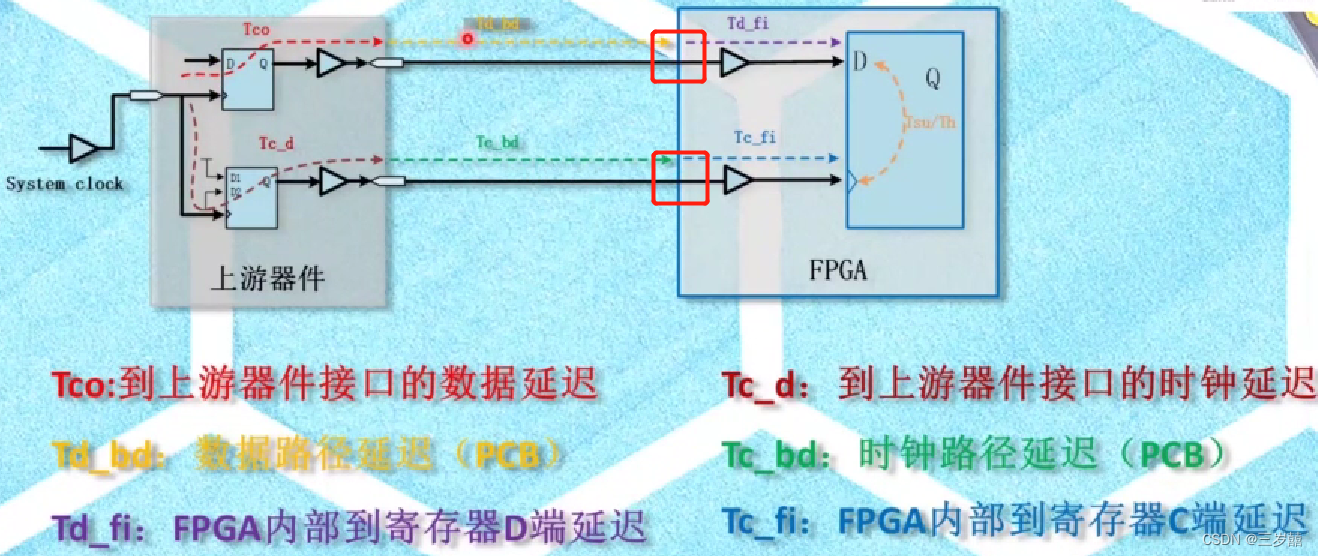

接下来以FPGA为中心,针对FPGA的IO分析input delay,并将此值填入FPGA的时序分析软件中。即针对下图中红色圈中对应额IO端口进行时序分析:

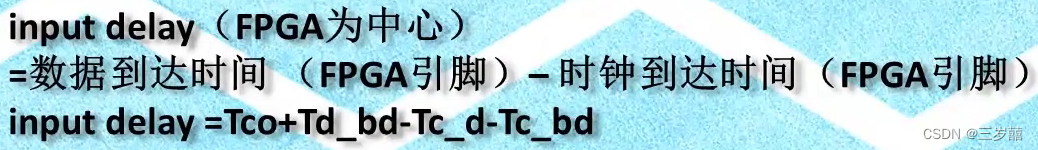

input delay = 数据到达的时间-时钟到达的时间

= Tco+Td_bd-(Tc_d+Tc_bd)

由于PCB可能多根线有着不同的延时时间,即Td_bd有不同的延迟效果,因此input delay也有最大最小之分。当Td_bd变大时,影响的是Tsu_slack,当Td_bd变小时,影响的是Th_slack。

当PCB布线延时最大时,Td_bd最大,

input delay max = Tco max + Td_bd max - (Tc_d+Tc_bd)

input delay min = Tco_min + Td_bd min - (Tc_d+Tc_bd)

参考资料:v3学院时序分析课程

3613

3613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?