一、DDR(Double Data Rate SDRAM(双倍速率的SDRAM))

SDRAM: Synchronous Dynamic Random Access Memory,同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。通常用来作为电脑的内存使用。

而DDR是在此基础上进行双边沿采样,也就是一个周期可以传输两个数据,因此称为Double Data Rate。纵观DDR的发展史可以看出,DDR的架构思路不是一味的增加主频,而是采用更精巧的结构进行数据速率的提升。

二、DDR基本结构

1.DDR的基本单元:cell

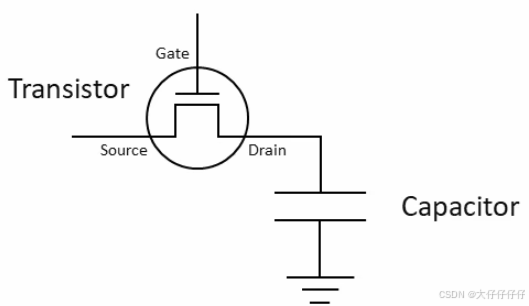

DRAM的数据存储策略是电容,电容存储了电量代表1,电容放空电量代表0,同时使用一个晶体管作为电容的充放电开关,以便实现1bit数据的读写,如下图:

当要读取 cell 的存储值,首先打开电子开关(即晶体管),然后根据电容的充放电信息获得存储值。如果 cell 保存“ 1 ”,即电容存有电荷,那么当打开开关,电容就会放电;如果 cell 保存“ 0 ”,即电容不保存电荷,那么打开开关之后电容不会放电。

当要向 cell 中写入值,仍然先打开电子开关,然后在电子开关的另一侧施加电压。如果要写入“ 1 ”,则施加高电压,此时电流会通过晶体管向电容充电;如果要写“ 0 ”,则让电子开关另一端接地。施加电压一段时间后即可断开开关,此时 cell 已经保存好写入值,因为电容很小,所以施加电压的时间会很短。

DDR4的Cell阵列大小是65536行x1024列,即65536根word line,1024根bit line,每根word line上联了1024个Cell,可以存储1Kbit数据,整个Cell整列可存储65535*1Kbit=64Mbit=8MB数据。行地址输入端配16位的地址解码器,列地址输入端配10位的选通器。为了减少引脚数,DDR4对行地址线和列地址线做了复用

原文链接:https://blog.csdn.net/ctbinzi/article/details/131410883

如下图,原文作者已经说的很详细,我想补充的是,以读出数据为例,当数据从cell读出时会进入信号放大器(兼锁存器),进入后数据将锁存在其中,如果我们选择了某根word line (即解码后的行地址),我们只需要再将列地址解码即可知道我们要读取哪些cell的值,这些数据会进入数据锁存器等待输出。假设我们这次读取了8bit数据后就结束了任务不再操作DDR,那么根据上文所述原理我们知道,读出的原理是电容放电。电容充放电后电容已经失去了原有的电压,按照这个思路难道说我们读取一次DDR,DDR的数据就清空了吗?答案是不是的,读完后就算我们不再操作DDR亦或者我们读取下一根word line,这时DDR会先将数据锁存器中的数据再充电回原有cell。 这样其实导致花费的时间就比较多了下文中会再次提到这一点。

另外还有一点,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

354

354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?