文章目录

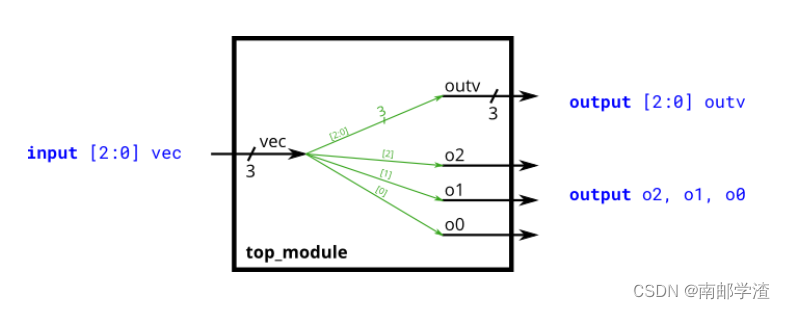

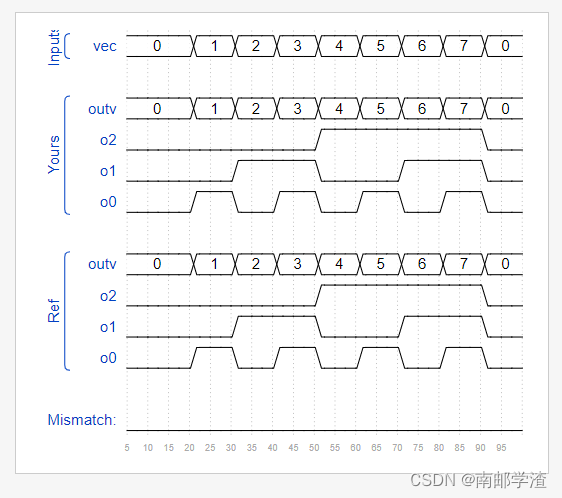

一、Vectors:Vectors

Vectors:向量,定义一组向量,可以整体赋值给另一个变量,也可以拆分为单个位数据赋值。

- RTL代码

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv = vec;

assign o0 = vec[0];

assign o1 = vec[1];

assign o2 = vec[2];

endmodule

- 仿真波形图

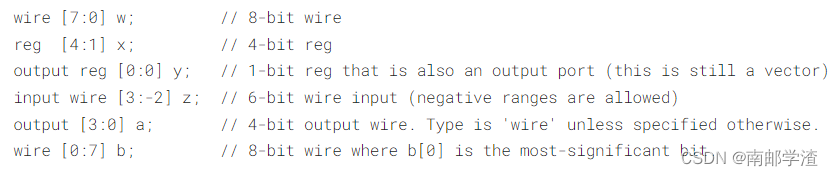

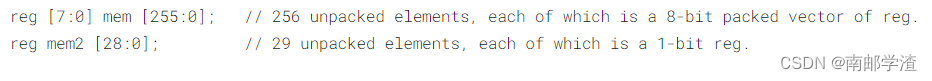

二、Vetors:Vetors in more detail

声明向量,需要说明的是[7:0]w表示最高位是w[7],而[0:7]w最高位是w[0];

未打包和打包阵列,变量名前面是位宽,后面是深度,可以近似理解为c语言中的二维数组。

- RTL代码

实现将输入的十六位数据平均分配给两个输出数据。

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

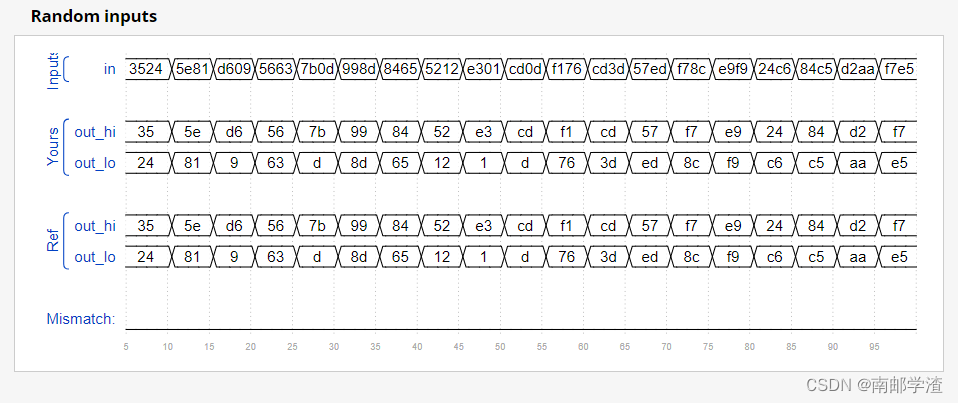

- 仿真波形图

三、Vectors:Vector part select

实现将一个32位数据分成四个字节,再进行字节的翻转

- RTL代码

module top_module(

input [31:0] in,

output [31:0] out );//

assign out[31:24] = in[7:0];

assign out[23:16] = in[15:8];

assign out[15:8] = in[23:16];

assign out[7:0] = in[31:24];

endmodule

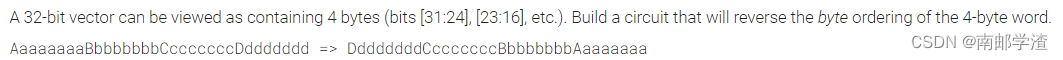

- 仿真波形图

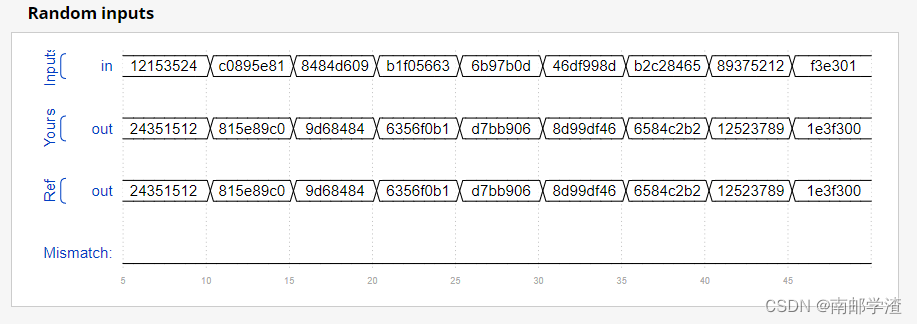

四、Vectors:Bitwise operators

实现将a和b按位或赋值给out_or_bitwise,将a和b逻辑或赋值给out_or_logical,将a和b按位非、非b赋值给高三位out_not、非a赋值给第三位out_not。

- RTL代码

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not[5:3] = ~b;

assign out_not[2:0] = ~a;

endmodule

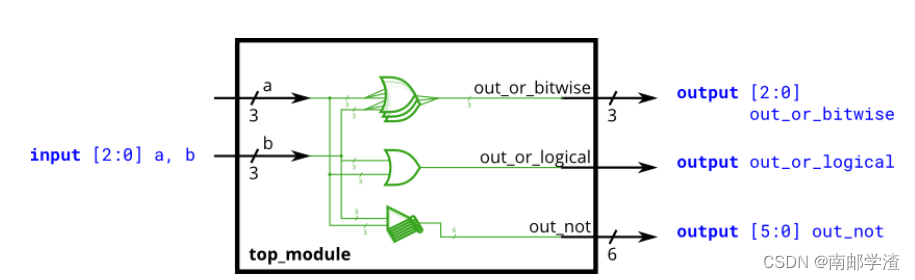

- 仿真波形图

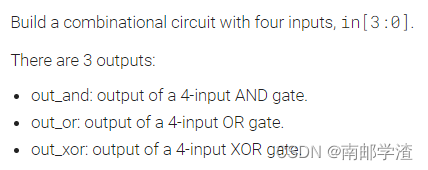

五、Vectors:Fout-input gates

对四位输入进行按位与、按位或、按位同或

- RTL代码

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = in[0] & in[1] & in[2] & in[3];

assign out_or = in[0] | in[1] | in[2] | in[3];

assign out_xor = in[0] ^ in[1] ^ in[2] ^ in[3];

//或者还可以

//assign out_and = ∈

//assign out_or = |in;

//assign out_xor = ^in;

endmodule

- 仿真波形图

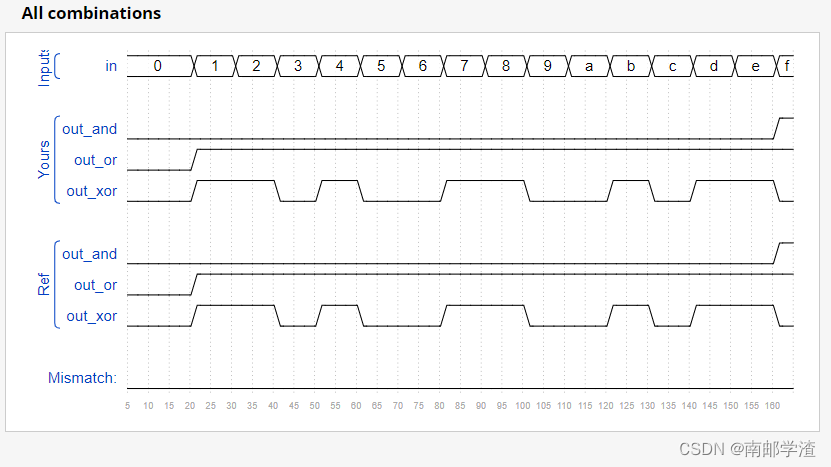

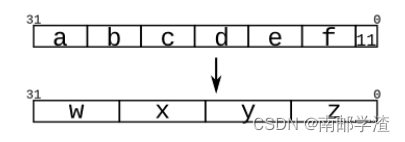

六、Vectors:Vector concatenation operator

对输入实现拼接

- RTL代码

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

assign {w,x,y,z} = { a,b,c,d,e,f,2'b11 };

endmodule

- 仿真波形图

七、Vectors:Vector reversal 1

将输入的八位数据颠倒

- RTL代码

module top_module(

input [7:0] in,

output [7:0] out

);

assign out = {in[0],in[1],in[2],in[3],in[4],in[5],in[6],in[7]};

endmodule

- 仿真波形图

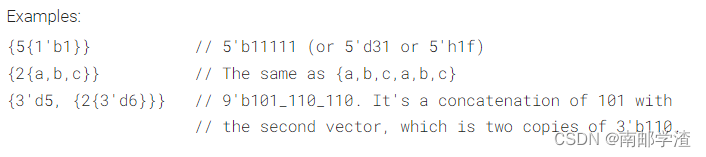

八、Vectors:Replication operator

实现将一个八位数据扩展为32位数据,数据符号不改变。

- RTL代码

module top_module (

input [7:0] in,

output [31:0] out );//

assign out = { {24{in[7]}} , in };

endmodule

九、vectors:More replication

- RTL代码

module top_module (

input a, b, c, d, e,

output [24:0] out );//

// The output is XNOR of two vectors created by

// concatenating and replicating the five inputs.

// assign out = ~{ ... } ^ { ... };

assign out = ~({{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}}) ^ ({5{a,b,c,d,e}});

endmodule

663

663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?