目录

5. 输入输出系统

5.1 概述

发展概况:

- 早期CPU与I/O设备串行工作,分散连接。使用程序查询方式连接。

- 后来使用总线连接(一条总线可以连接多个设备),出现了I/O接口和DMA控制器,并行工作。

- 具有通道结构的阶段。

- 具有I/O处理机的阶段(I/O的独立性更强,使用I/O处理器)。

I/O系统的组成:

- I/O软件:

- CPU中的I/O指令,来控制外部设备与主机协调工作,格式为==操作码+命令码+设备码==。

- 通道指令,通道自身的指令。

- I/O硬件:

- 设备以及I/O接口,或者设备以及设备控制器,通道。

I/O设备与主机的联系方式:

- 对I/O设备进行编址:统一编址(将I/O地址放在内存的地址空间中,可以直接使用指令对外部设备进行存取数),不统一编址(需要使用专门的I/O指令来调用设备)。

- 设备选址:使用设备选择电路识别某个设备是否被选中。

- 数据传送方式:串行(一位一位传输)/并行(多位同时传输)。

联络方式:

- 立即响应,接收到数据/指令,直接响应。

- 异步工作,使用应答信号,可以并行也可以串行(I/O设备与接口之间)

- 同步工作,使用同步时标。

I/O设备与主机的连接方式:分散连接(辐射式连接,每台设备都配有一套控制线路和信号线),总线连接。

I/O设备与主机信息传送的控制方式:

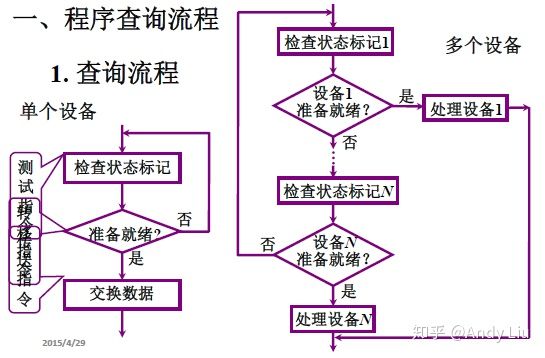

- 程序查询方式(CPU与I/O串行工作,CPU需要等待,效率很低,CPU连接I/O设备和内存)

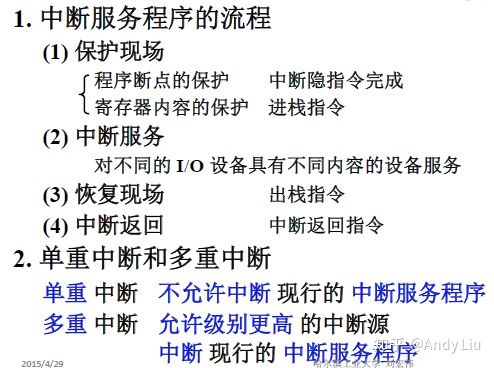

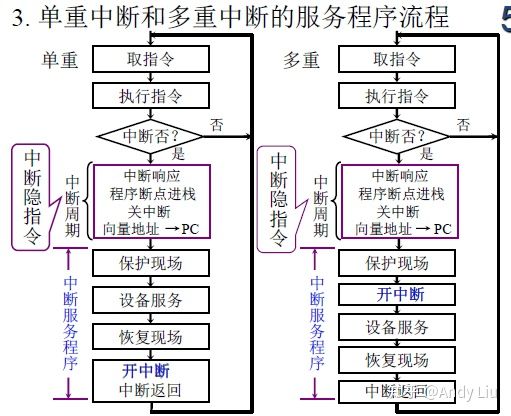

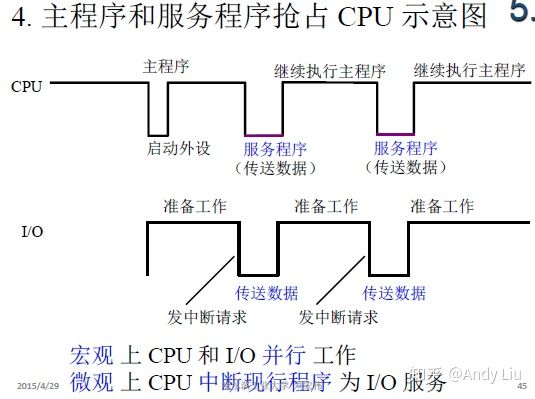

- 程序中断方式(部分并行,CPU被一定程度解放,在IO设备自身准备的时候,CPU可以先进行自己的工作,当IO与主机进行信息交换的时候,CPU暂停自身程序,来参与信息交换)。

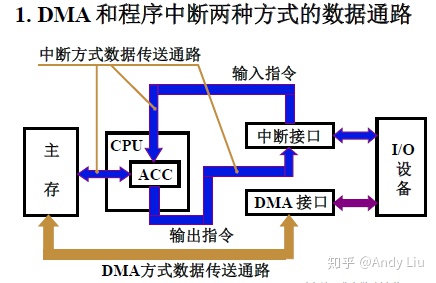

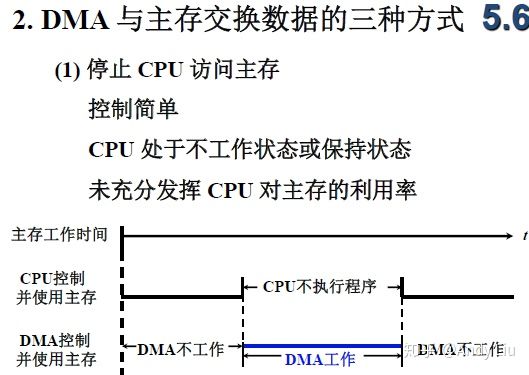

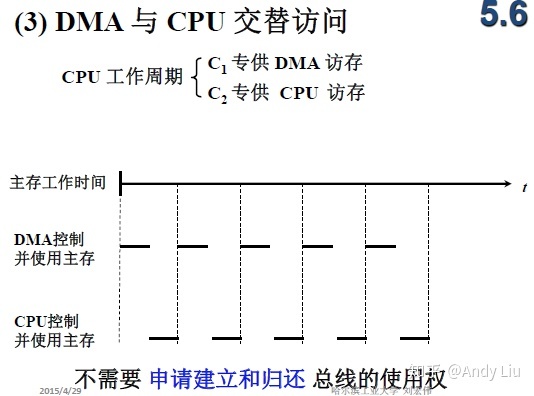

- DMA方式(使外部设备与内存建立连接,解放cpu,主存与IO之间有一条直接数据通道,通过DMA控制器可以直接进行数据交换,==采用周期窃取,借用一个存取周期,使得DMA控制总线,完成数据在IO和主存之间的传送==,在这个周期中,CPU不能控制总线,但可以继续执行不需要访存的指令)。

5.2 外部设备

- 输入设备:键盘、鼠标、触摸屏

- 输出设备:显示器、打印机

- 其他:A/D,D/A转换器,终端,汉字处理

- 多媒体技术:VR等

5.3 I/O接口

5.3.1 概述

为什么要设置接口:

- 实现设备的选择

- 实现数据缓冲,达到速度匹配

- 实现数据串/并格式转换

- 实现电平转换(主机和IO设备工作电平可能不一致)

- 传送控制命令

- 反映设备的状态(忙、就绪、中断请求)

5.3.2 接口的功能和组成

主机通过IO总线与IO设备相连接。

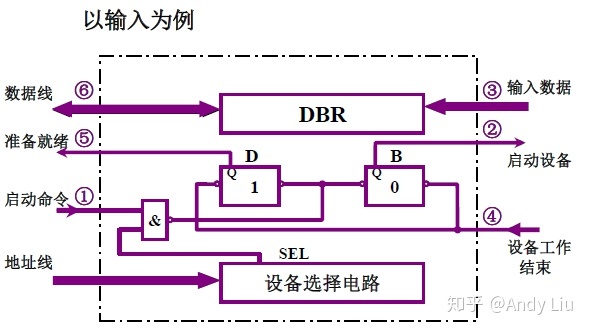

五大部分:数据缓冲寄存器、设备状态标记、控制逻辑电路、设备选择电路、命令寄存器和命令译码器。

5.3.3 接口类型

- 按照数据传送方式:串行/并行

- 按照功能选择的灵活性:可编程接口/不可编程接口

- 按通用性:通用接口/专用接口

- 按数据传送的控制方式:中断接口/DMA接口

5.4 程序查询方式

程序查询方式的接口电路:

- 当D等于1的时候,IO完成了送入数据到DBR,此时CPU通过数据线读入数据,在D等于1之前,CPU一直在原地踏步等待。

5.5 程序中断方式

5.5.1 中断的概念

CPU在执行程序的时候,遇到特殊事件或异常事件,暂停原来的程序,去处理这个事件(执行中断服务程序),之后再继续执行原来的程序。

5.5.2 I/O中断的产生

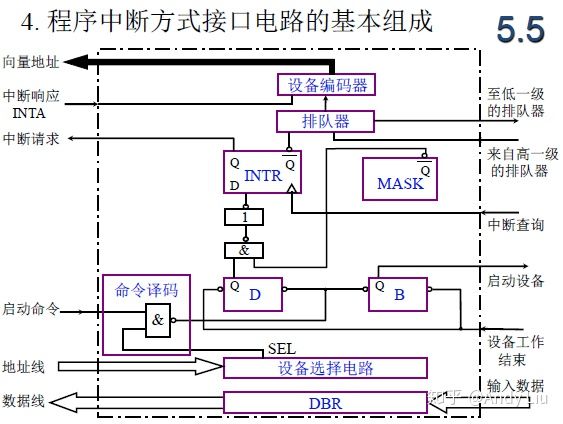

5.5.3 程序中断方式的接口电路

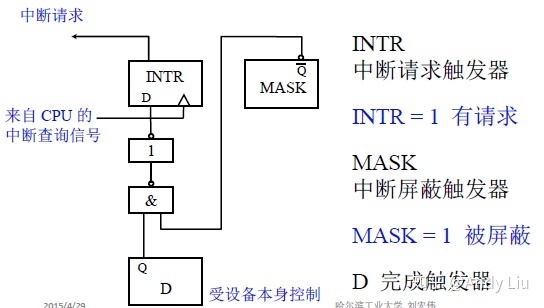

- 配置中断请求触发器和中断屏蔽触发器(如果目前执行的程序比请求的设备优先级高,则屏蔽该中断请求)

- 排队器(有多个中断的话,需要使用排队器,根据优先级进行排队)

- 中断向量地址形成部件(形成中断服务程序的入口地址)

配置中断请求触发器和中断屏蔽触发器:

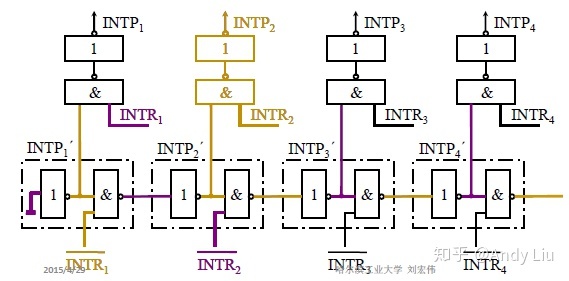

排队器:

排队器可以使用硬件电路来实现(在CPU内或接口电路中),也可以在软件中实现。

链式排队器,输出只有一位是高电平,其他都是低电平,高电平表示此时最高优先级的中断。

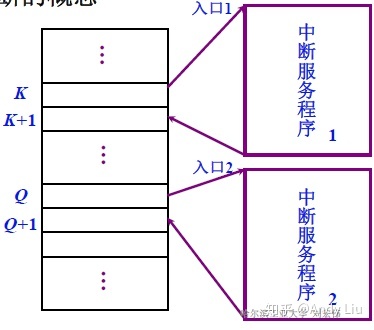

中断向量地址形成部件:

找到中断服务程序的入口地址,同样可以使用软件或硬件方法(硬件向量法)。

硬件向量法由硬件产生向量地址,再由向量地址找到入口地址。

中断向量地址形成部件的输入为排队器的输出(只有一位是高电平,其他都是低电平),==输出为该种中断的向量地址,再通过向量地址,找到该种中断的中断服务程序的入口地址。==

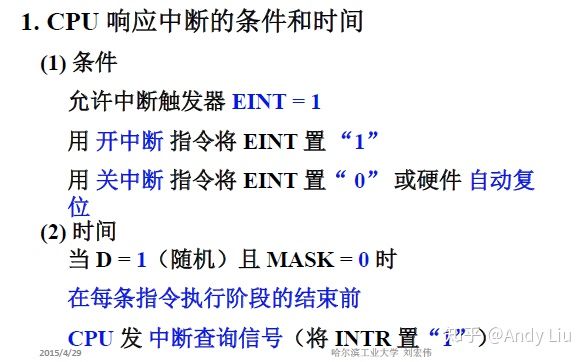

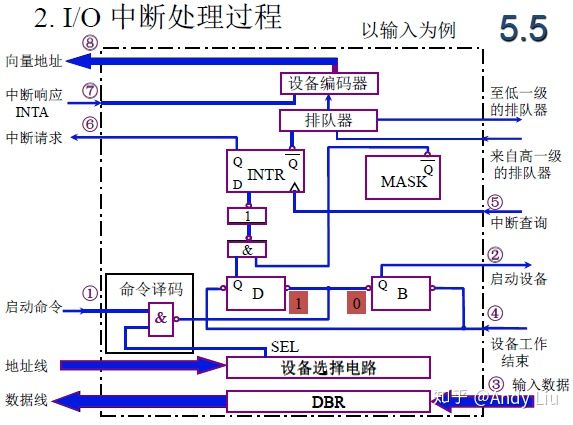

5.5.4 I/O中断处理过程

5.5.5 中断服务程序流程

5.6 DMA(直接存储器访问)方式

5.6.1 DMA方式的特点

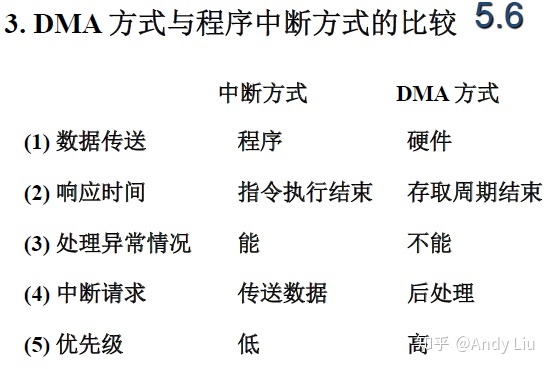

程序中断方式必须使用CPU来作为缓冲(即使是主存和IO之间进行信息交换)。

DMA方式,不需要CPU作为缓冲。

- 这种方法的实用性不强。

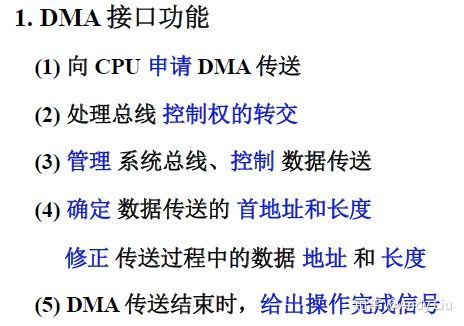

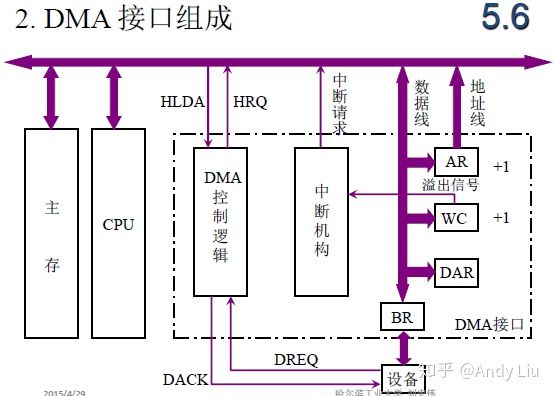

5.6.2 DMA接口的功能和组成

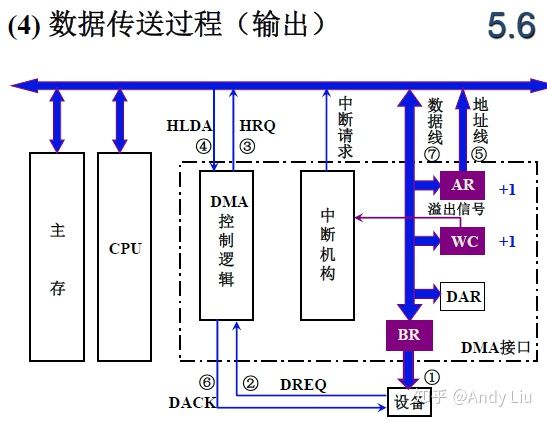

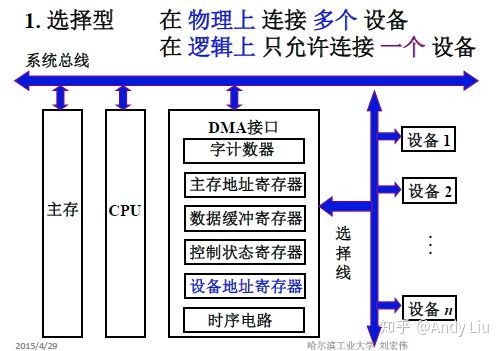

- AR:地址寄存器,WC:计数器,对传输数据量计数。

- BR:数据缓冲器,DAR:设备地址寄存器,供设备选择电路使用;对于硬盘等设备,可以保存扇区号等。

- DMA控制逻辑:完成与设备之间的请求回答,与总线的请求回答。

- 中断机构:传输结束之后的后续处理。

5.6.3 DMA的工作过程

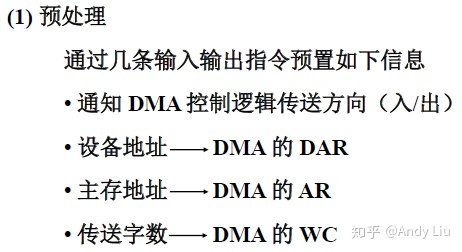

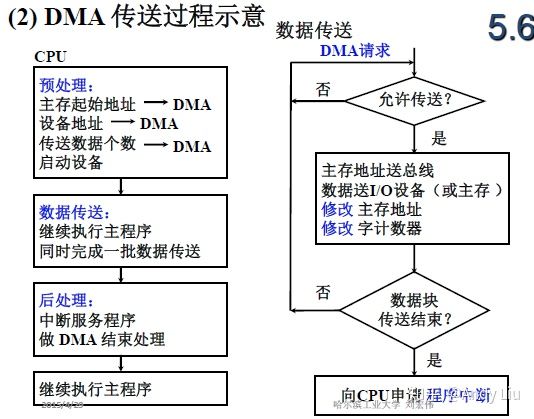

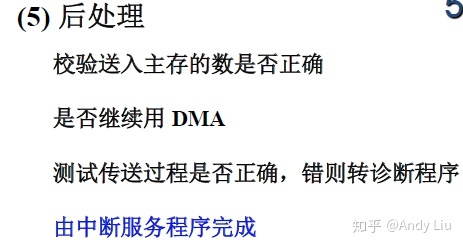

DMA的传送过程:预处理、数据传送、后处理。

DMA接口与系统的连接方式:

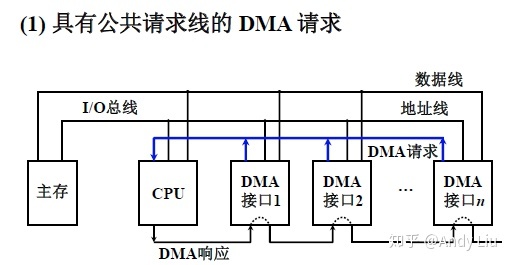

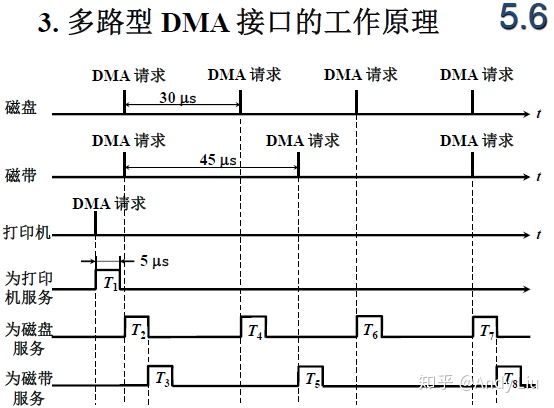

- 多个DMA接口连在一起,共享一条请求线。各DMA同样有优先级顺序。

5.6.4 DMA接口的类型

- 一个接口连了多个设备,但是每次只能与一个设备使用。

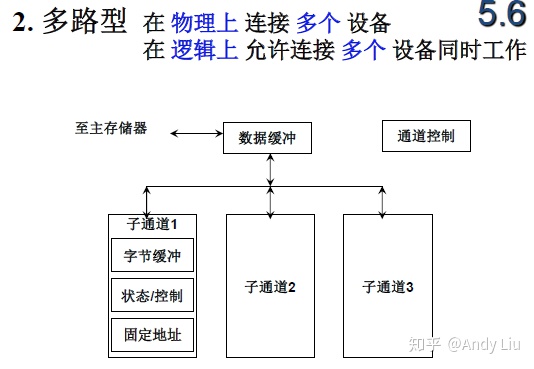

- 每个通道有多个子通道,子通道可以并行使用。

942

942

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?