精通APB (Advanced Peripheral Bus) 总线设计通常意味着你不仅理解其基础概念,而且能够在实际的硬件设计中灵活运用APB总线,解决复杂问题,并优化设计。以下是一些关键点,当你掌握这些方面时,可以说你对APB总线设计有了深入的理解:

-

理论知识:

- 理解APB总线的基本原理和架构。

- 熟悉APB总线的信号定义,包括地址、数据、控制和握手信号。

- 了解APB总线的时序要求和协议规范。

-

设计能力:

- 能够设计APB主控器(通常是APB桥接器)和APB从设备。

- 熟练使用Verilog、VHDL或其他硬件描述语言实现APB接口。

- 能够集成APB总线到系统级芯片(SoC)设计中。

-

验证技能:

- 掌握APB总线的验证方法,能够创建测试用例并执行功能验证。

- 使用形式验证或模拟来确保APB接口的正确性。

-

调试技巧:

- 能够使用逻辑分析仪或波形查看器调试APB总线上的问题。

- 理解如何定位和解决时序和数据完整性问题。

-

优化与分析:

- 理解APB总线的性能瓶颈,并知道如何优化设计以提高效率。

- 能够进行功耗分析,确保设计符合低功耗目标。

-

标准与兼容性:

- 理解APB总线与其他AMBA总线(如AHB、AXI)的交互。

- 确保设计遵循ARM AMBA APB规范。

-

实践经验:

- 拥有多个成功的APB总线设计和集成经验。

- 能够处理跨芯片设计的复杂性。

-

持续学习:

- 关注APB总线和AMBA架构的发展趋势,保持更新知识。

精通任何技术都需要时间和实践,对于APB总线设计而言,这同样适用。你需要通过阅读官方文档、参考设计、参与项目和不断实践来积累经验。同时,加入相关的技术论坛和社区,与同行交流,也是提高技能的好方法。

总线会有按照协议规定的一组信号,除此之外,总线所连接的从设备也会有独立的时钟与复位信号,不会和总线用相同的时钟,所以两者之间传输的数据和信号会要做跨时钟处理。

基本原理

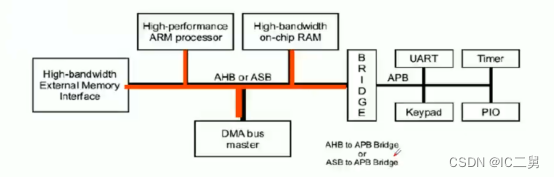

高级外设总线(APB:Advanced Peripheral Bus)是高级微控制器总线体系结构(AMBA:Advanced Microcontroller Bus Architecture)协议系列的一部分。它定义了一个低成本的接口,优化了最小的功耗和降低的接口复杂性。

APB是非流水结构,所以它主要用在不需要用到高性能总线(AXI)的低带宽外围设备上。

特点:

- 成本低

- 功耗小

- 接口简单

- 非流水结构

常见用法:使用APB总线来访问外围设备的可编程控制寄存器。

架构

信号定义

| 信号 | 方向 (对主设备) | 源 | 位宽 | 信号描述 |

|---|---|---|---|---|

| PCLK | 输入 | 系统时钟源 | 1bit | 时钟信号,APB协议中所有信号只和时钟上升沿有关 (同步APB总线上的所有操作) |

| PRESETn | 输入 | 系统复位 | 1bit | 复位信号,低电平有效 |

| PADDR | 输出 | APB桥 | 32bit | 地址总线,指示要访问的寄存器地址 支持的最大地址空间是2^32=4G |

| PWRITE | 输出 | APB桥 | 1bit | 方向信号,指示当前传输的是读操作还是写操作 高电平写,低电平读 |

| PSEL | 输出 | APB桥 | 根据系统需求 | 片选信号,指示选择的从设备 每个从设备都有一个对应的PSEL信号 |

| PENABLE | 输出 | APB桥 | 1bit | 使能信号,在传输的第二个和后续时钟周期有效, 它表明数据传输已经开始,但尚未完成 |

| PWDATA | 输出 | APB桥 | 32bit | 写数据总线,用于从主设备向从设备传输数据。 在写操作期间,数据在PENABLE的上升沿被锁存 |

| PSTRB | 输出 | APB桥 | 4bit | 字节选通信号,用于指示哪些字节应当被写入。 PSTRB中的一位对应写数据总线中的一个字节 |

| PRDATA | 输入 | 从设备 | 32bit | 读数据总线,用于从设备向主设备传输数据。 在读操作期间,数据在PENABLE的上升沿被采样 |

| PREADY | 输入 | 从设备 | 1bit | 准备信号,用于告知主设备从设备是否准备好接收或发送数据。 在传输过程中,如果从设备需要更多时间来准备数据,它可以延迟PREADY信号,从而延长传输周期 |

| PPROT | 输出 | APB桥 | 3bit | 保护类型。指示事务的正常、特权或安全保护级别, 以及该事务是数据访问还是指令访问 |

时序要求

无需等待的写操作

- 在T0阶段,所有总线处于IDLE状态。

- 在T1阶段,PADDR、PWRITE、PWDATA和PSEL在时钟的上升沿被寄存,即主设备APB桥把这些数据发送到总线上。此时处在Setup状态。

- 在T2阶段,PENABLE拉高,指示传输开始,与此同时从设备已经接收到主设备发送过来的地址和写控制命令,知道主设备要准备发数据过来,于是拉高PREADY表示已经做好准备。此时处在Access状态。

- T3时刻,PADDR和PWRITE会一直保持有效直到传输结束(T3时刻)。表示传输结束的时钟上升沿到来后,PENABLE和PSEL拉低。

PREADY有效就表示从设备可以在下一个时钟上升沿完成传输。

有等待的写操作

只有当从设备准备好接收数据后,PREADY信号才会拉高,传输才得以开始。因此当从设备没准备好的时候,可以保持PREADY的低电平,来延长传输。

传输被延长的时候,PADDR,PWRITE,PSEL,PENABLE,PWDATA,PSTRB和PPROT会一直保持原来的值。

无需等待的读操作

无等待的读操作和写操作唯一的区别在于此时的PWRITE是低电平,从设备需要在读操作结束前将数据传输到总线上。

需要等待的读操作

在读操作中同样可以使用PREADY来延长传输。

注意的是,在读操作中,PSTRB所有位必须设置为低电平。

Note:

传输过程中可以一直保持地址PADDR和读写操作PWRITE信号的不变,直到开始新一轮的传输,这有助于系统节省功耗。

错误响应

PSLVERR用于指示APB传输时读写操作中出现的错误情况。

- 当PSEL、PENABLE和PREADY都为高电平时,会出现错误状态。

- 出现错误状态后,PSLVERR会在传输的最后一个时钟周期内保持有效。

APB外围设备不要求必须支持PSLVERR引脚,当不使用该引脚时,应被置低。

映射关系:

- AXI -> APB RRESP[1]/BRESP[1] = PSLVEER

- AHB -> APB HRESP[0] = PSLVERR

保护单元支持

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?