1.结构冒险

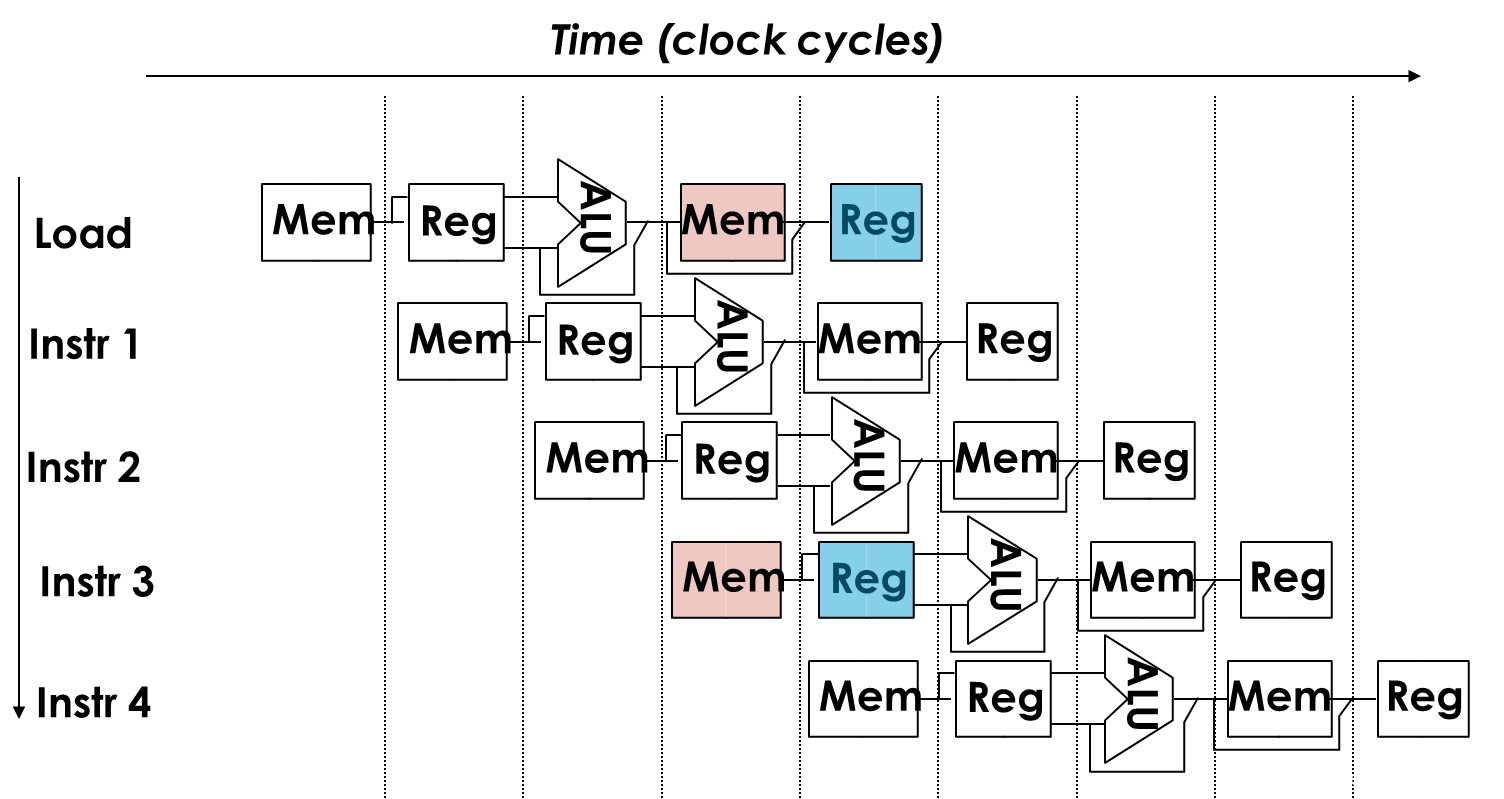

定义:同一个部件同时被不同指令所使用而引起的流水线阻塞。

正如上面的Load和Instr 3指令的Mem和Reg两处都发生了结构冒险[Mem同时使用了存储器,Reg同时使用了寄存器]。

解决办法:

正如上面的Load和Instr 3指令的Mem和Reg两处都发生了结构冒险[Mem同时使用了存储器,Reg同时使用了寄存器]。

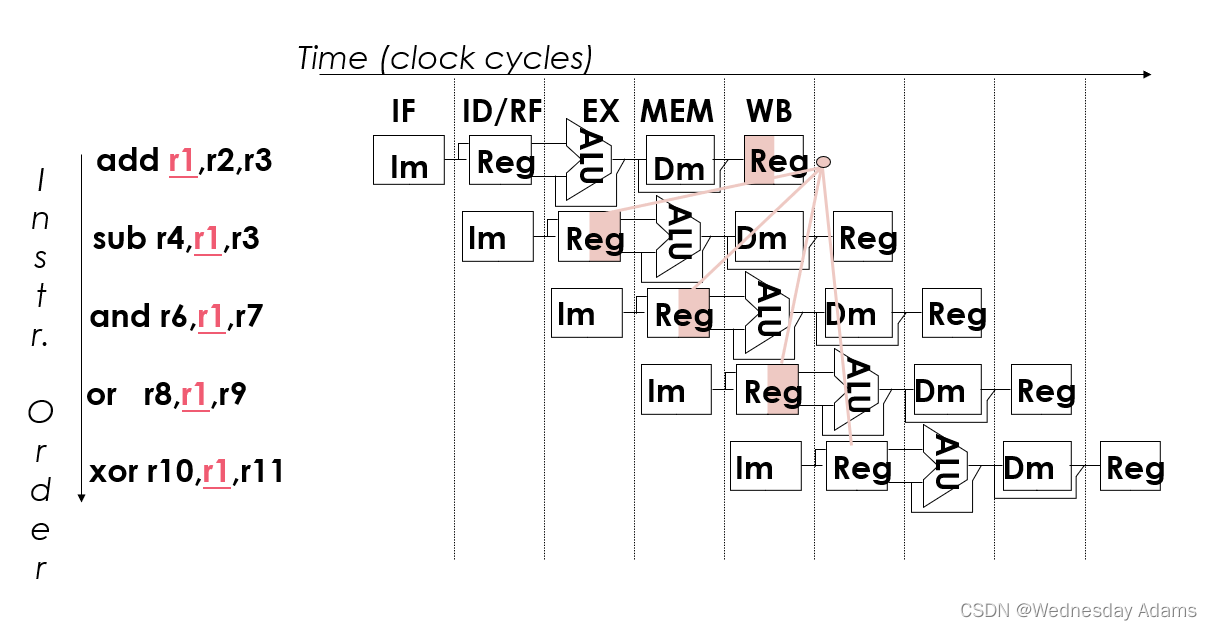

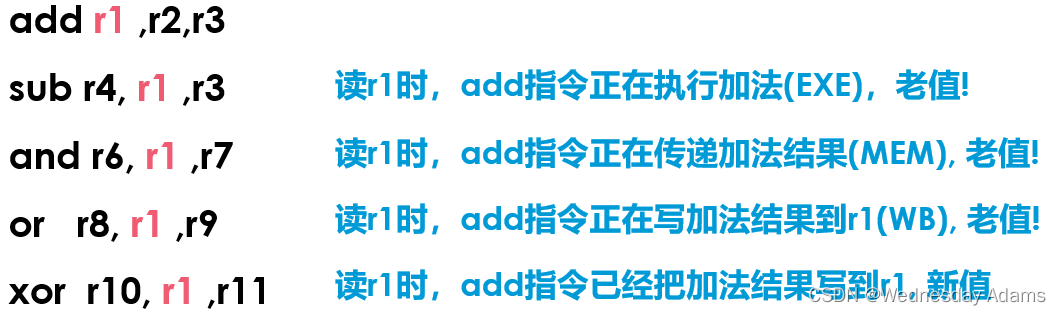

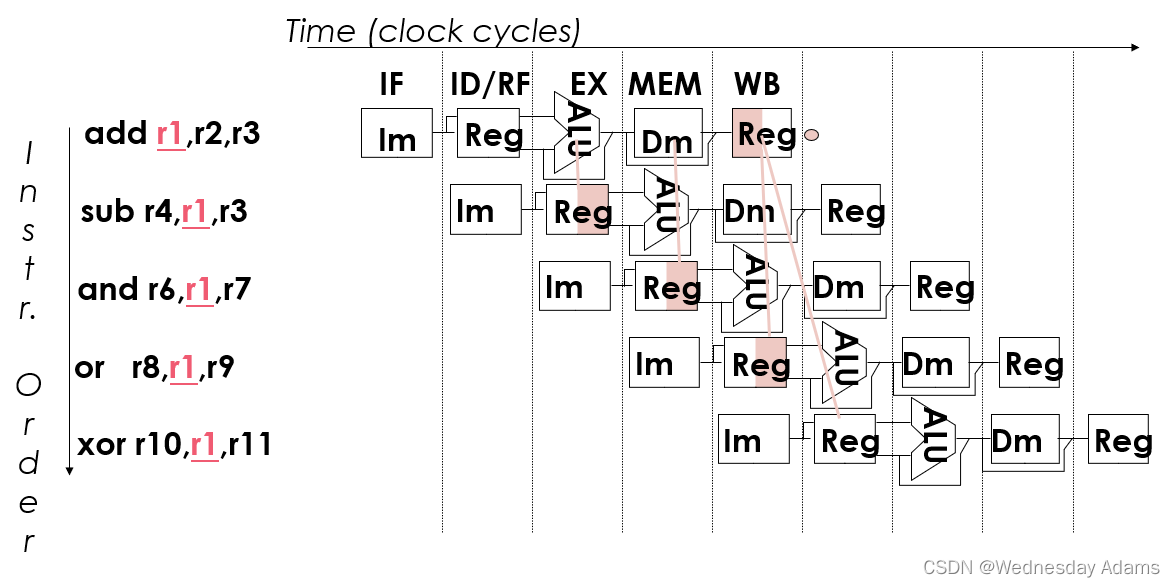

2.数据冒险

2.1普通结构冒险

定义:后面指令要用到前面指令产生的结果而前面的结果还没产生而引起的流水线阻塞。

正如上面的sub、and、or和xor都要用到add产生的r1,但r1在WB阶段才产生,因此存在以下问题:

解决办法:

方法1: 转发技术

定义:当后面指令要用到前面指令的结果数据时,前面流水线部件中得到的数据直接通过连线传送到后面流水段的部件中,而不等前面指令的结束。这种方式称为转发或旁路,它能解决部分数据冒险。

方法2:合理实现寄存器堆的读/写操作

前半时钟周期写,后半时钟周期读,若同一个时钟内前面指令写入的数据正好是后面指令所读数据,则不会发生数据冒险

- 在

sub处使用转发技术,让add在ALU的运算结果直接传到sub的Reg处 - 在

and处使用转发技术,让add在ALU或Dm的运算结果直接传到and的Reg处 - 在

or处使用转发技术,让add在Reg前半部分产生结果,然后将结果在后半部分直接传到or的Reg处

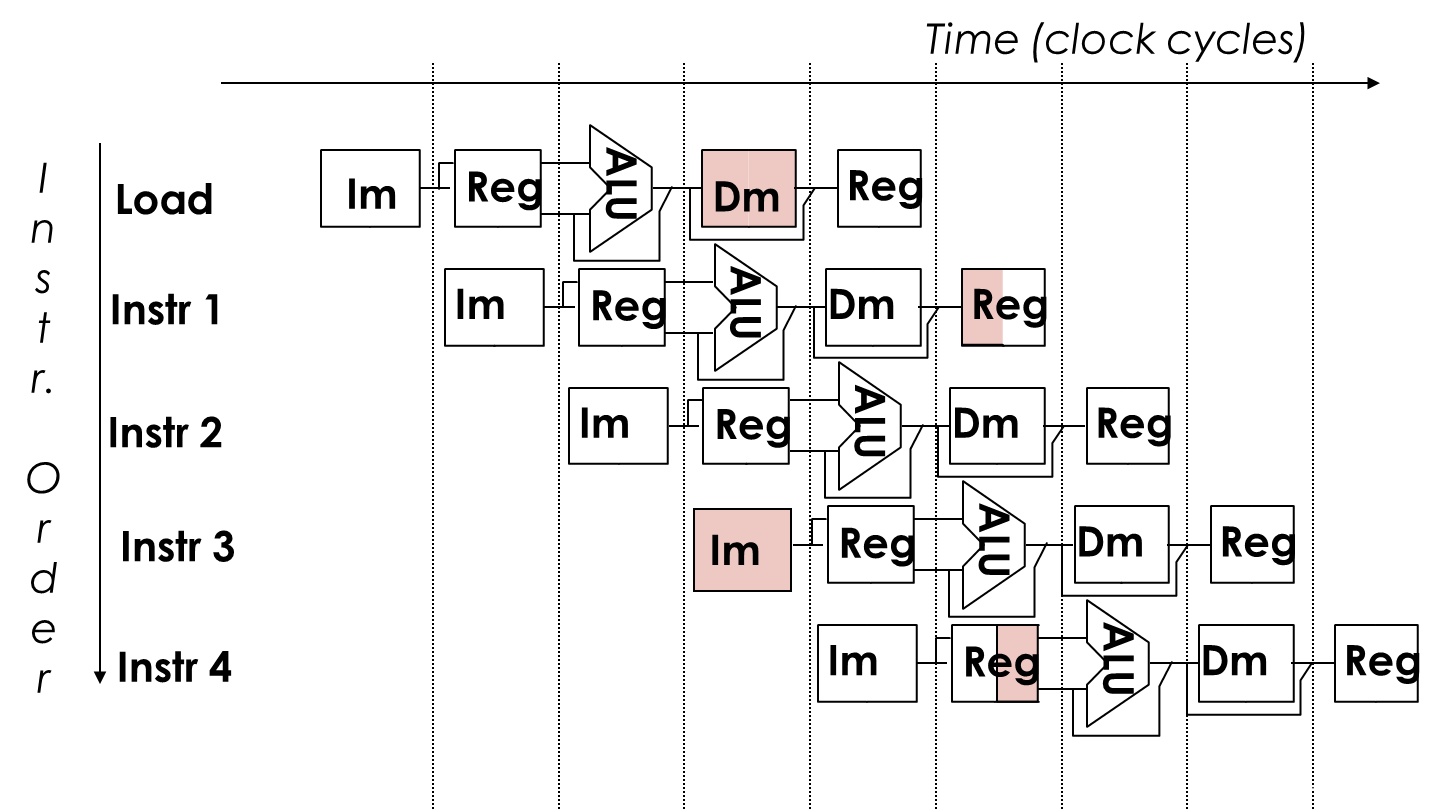

2.2.Load-use结构冒险

定义:和普通结构冒险差不多,后面的非Load指令要用到前面的Load指令产生的结果而前面的结果还没产生而引起的流水线阻塞。

解决办法:

合理调整指令指令顺序

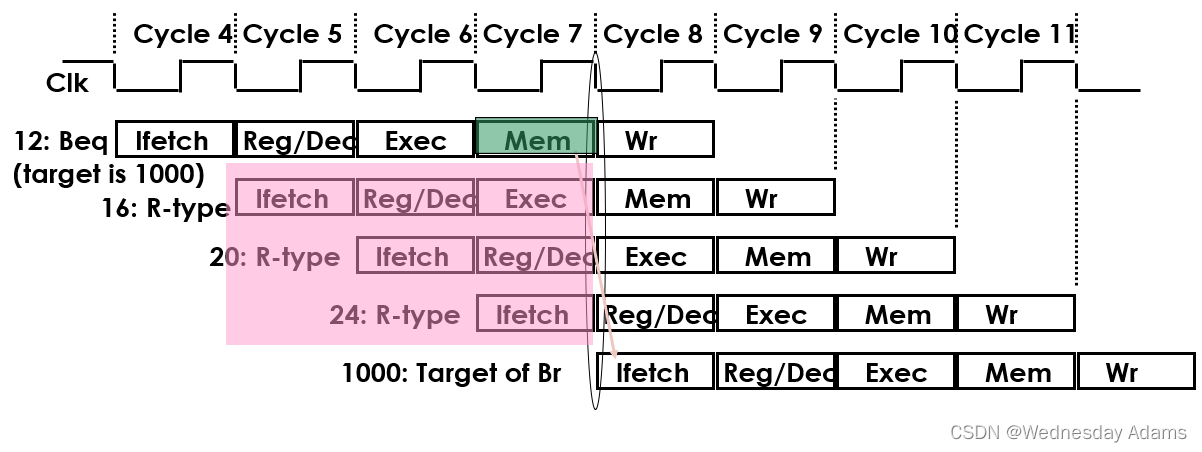

3.控制冒险

定义:由于发生了指令执行顺序的改变引起的流水线阻塞。

如上图的Beq指令,是一条转移指令,到Mem才知道要转移到1000:Target of Br指令,但这是已经执行了16、20和24这三条指令了,因此取错了三条指令。

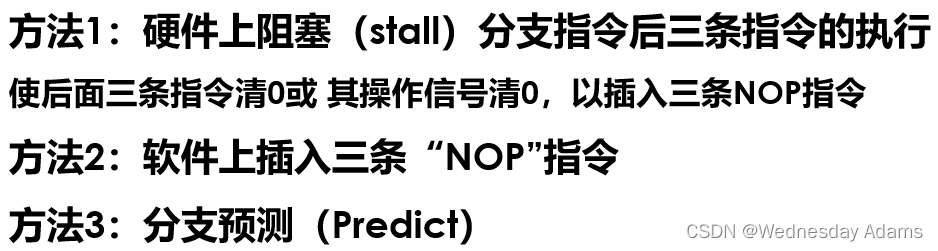

解决办法:

文章讨论了处理器流水线中的三种冒险类型:结构冒险、数据冒险(包括普通结构冒险和Load-use结构冒险)以及控制冒险。结构冒险发生在同一部件被不同指令同时使用时,可以通过改进硬件设计避免。数据冒险是由于指令间依赖导致的,转发技术可以部分解决这个问题。Load-use结构冒险类似,解决方法是优化指令顺序。控制冒险主要由分支指令引起,解决策略涉及预测技术。

文章讨论了处理器流水线中的三种冒险类型:结构冒险、数据冒险(包括普通结构冒险和Load-use结构冒险)以及控制冒险。结构冒险发生在同一部件被不同指令同时使用时,可以通过改进硬件设计避免。数据冒险是由于指令间依赖导致的,转发技术可以部分解决这个问题。Load-use结构冒险类似,解决方法是优化指令顺序。控制冒险主要由分支指令引起,解决策略涉及预测技术。

7284

7284

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?