-

SPI协议简解

SPI是一个同步的数据总线,也就是说有单独的数据线和单独的时钟信号来保证发送端和接收端的完美同步。

1、SPI总线包括4条逻辑线

- MISO:(Master Input Slave Output)主机输入,从机输出。

- MOSI:(Master Output Slave Input)主机输出,从机输入。

- SCLK:(Serial Clock)串行时钟信号,由主机发送给从机。

- CS:(Slave Select)片选信号,由主机发送,控制与哪个从 机进行通信,低电平有效。

2、时钟频率

SPI总线的主机必须在通信开始时配置并生成相应的时钟信号,在每个SPI时钟周期内,都会发生全双工数据的传输。

3、时钟极性(Clock polarity ---- CPOL)

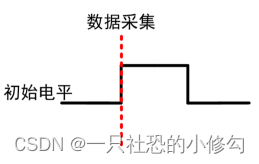

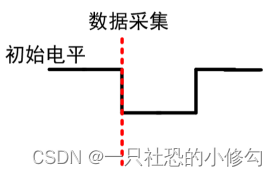

CPOL = 0:时钟空闲时,SCLK初始为低电平。

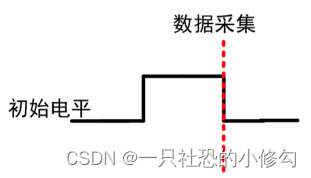

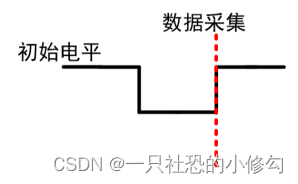

CPOL = 1:时钟空闲时,SCLK初始为高电平。

4、时钟相位(Clock phase ---- CPHA)

不同的时钟相位,采集数据时在时钟信号的具体边沿有所不同。

CPHA = 0:在时钟信号SCLK的第一个跳变沿进行采样,也就是在时钟信号SCLK的奇边沿进行采样。

CPHA = 1:在时钟信号SCLK的第二个跳变沿进行采样,也就是在时钟信号SCLK的偶边沿进行采样。

5、时钟配置总结

SPI的时钟根据时钟极性和时钟相位的不同,可以相应的配置成4中模式。

| SPI Mode | CPOL | CPHA |

| 0[0 0] | 0 | 0 |

| 1[0 1] | 0 | 1 |

| 2[1 0] | 1 | 0 |

| 3[1 1] | 1 | 1 |

| 模式0 | 模式2 |

|

|

|

| 模式1 | 模式3 |

|

|

|

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?