摘要:本文主要根据《深入浅出玩转FPGA》一书,对前几讲的内容进行了一些概括,主要讲解了FPGA的基本概念,FPGA的内部结构的讲解,最后讲解了FPGA开发的基本流程。

1.FPGA的基本概念

简单来说,FPGA就是可以反复进行编程的逻辑器件,FPGA的四个英文单词取自Field Programmable Gate Array。FPGA的开发本质上是一些逻辑电路之间互连从而实现特定的逻辑功能,早期的FPGA开发就是通过绘制原理图来完成的。

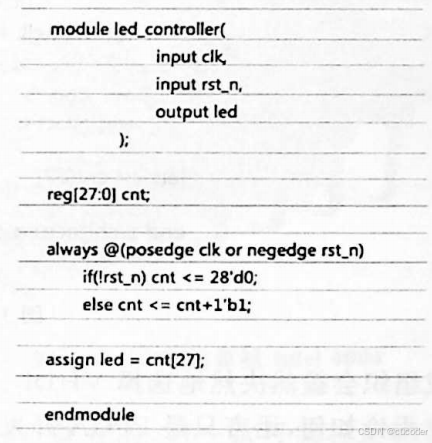

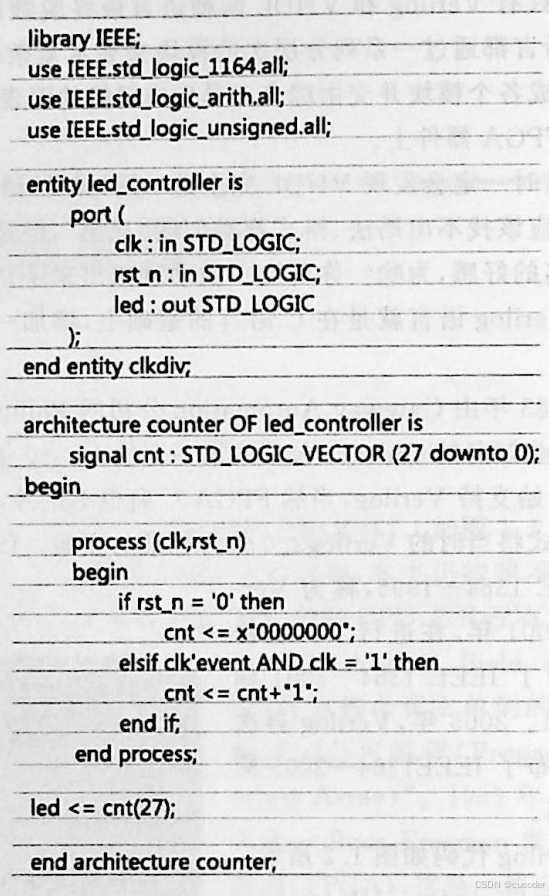

FPGA的发展历史上出现过许多用于描述电路功能的语言,但是最终只有Verilog和VHDL脱颖而出。这两种语言通过一系列分层次的模块来表示复杂的数字系统,逐个模块仿真验证之后,再集成各个模块并交由综合工具生成门级的网表,最后由布局布线工具将其映射到目标FPGA器件上。

Verilog代码 VHDL代码

2.FPGA的内部结构

FPGA器件中通常包括以下的基本模块单元:

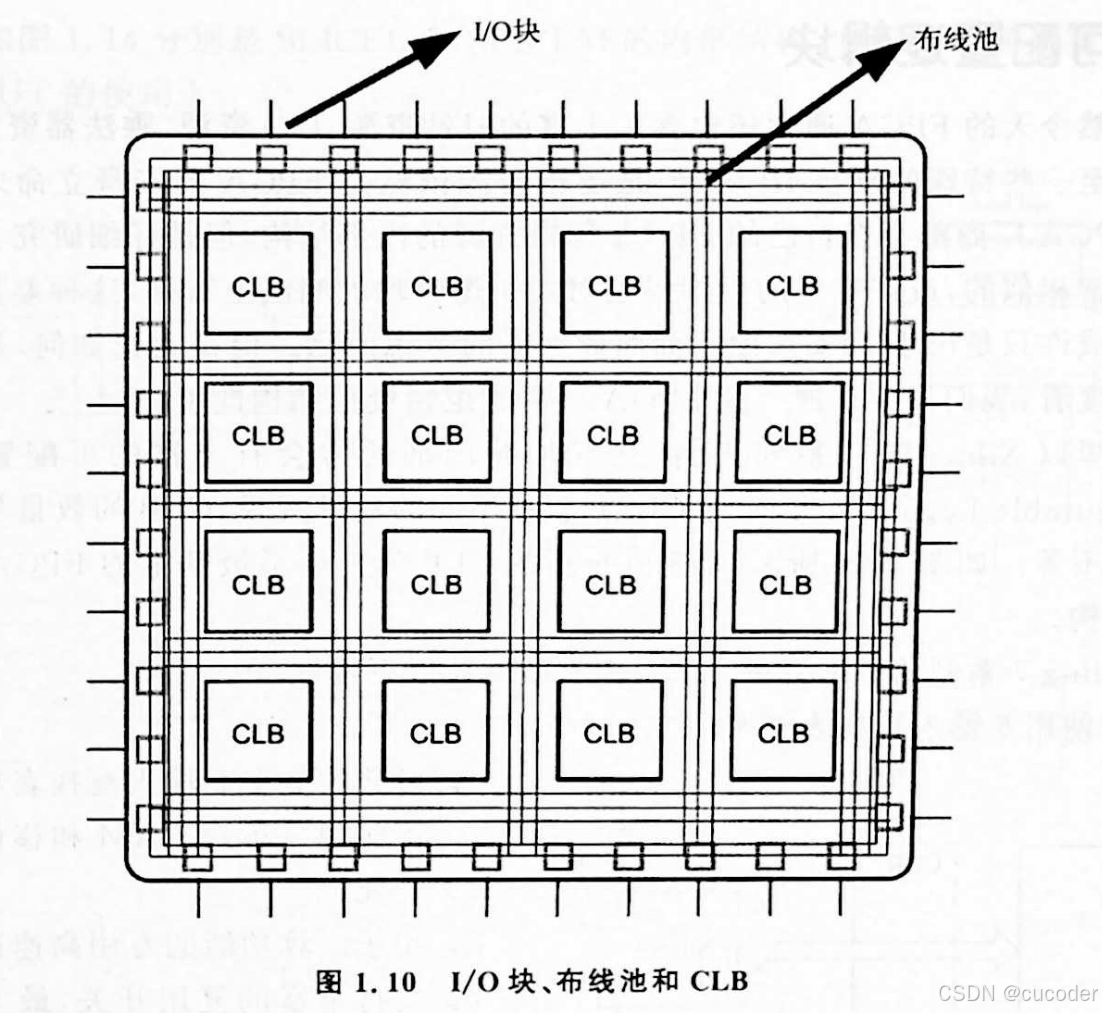

1.可配置逻辑块(CLB):通常包含了丰富的FPGA逻辑电路资源。

2.线(Wires):用于连接各个不同的模块单元,FPGA内部通常有非常丰富的预连线资源,这些连线也都是根据实际应用设计可编程的。

3.输入/输出端口(IO ports):FPGA器件与外部芯片互连的引脚。

围绕在CLB周围丰富的行、列走线被称为布线池,用于衔接FPGA的各个CLB以及其他相关的资源;FPGA芯片周围的小矩形以及延伸出去的短线,则是FPGA和外部芯片接口的IO块的示意。

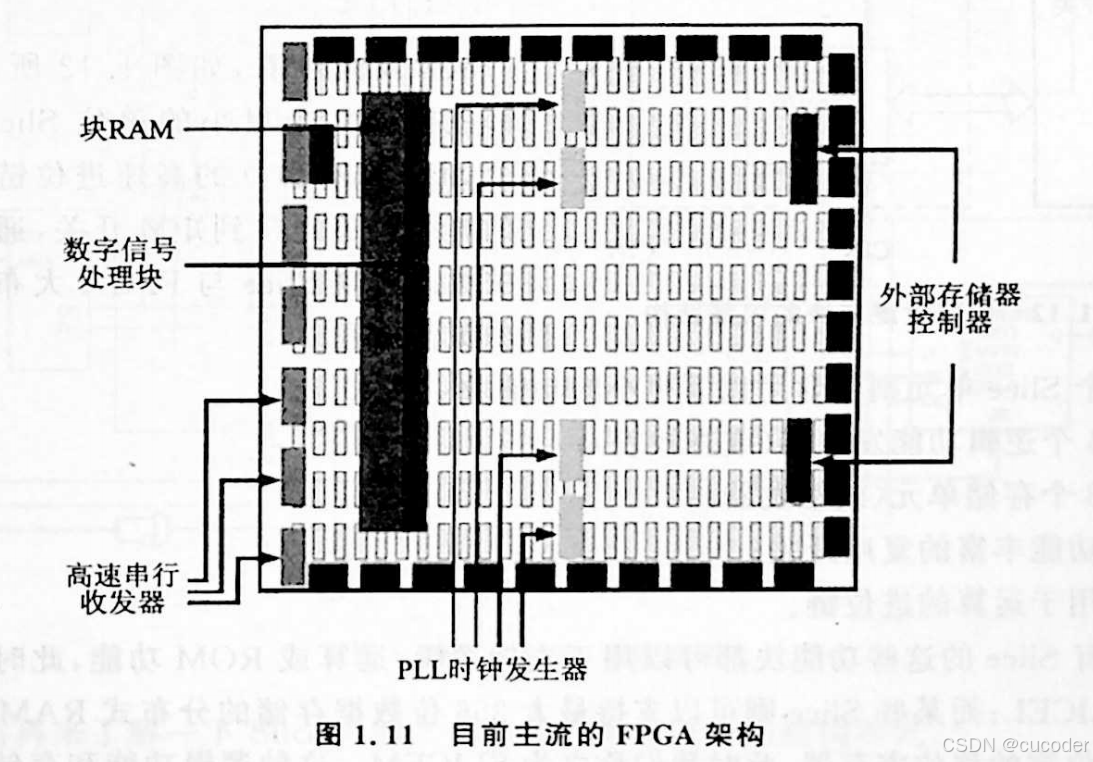

现在的FPGA器件为了保证在各种应用中都能够最大程度地发挥其性能优势,以满足用户不同的应用需求,所以内部增加了很多额外的用于数学院算、数据存储、时钟管理等特定功能的模块单元。这些额外的FPGA资源主要包括以下的模块单元:

1.成块出现的FPGA内嵌存储器(块RAM)。

2.用于产生不同时钟频率的锁相环(PLL时钟发生器)以及相应的时钟不限资源。

3.高速串行收发器。

4.外部存储器控制器(硬核IP)。

5.用于实现数字信号处理的乘累加模块(DSP Slice)。

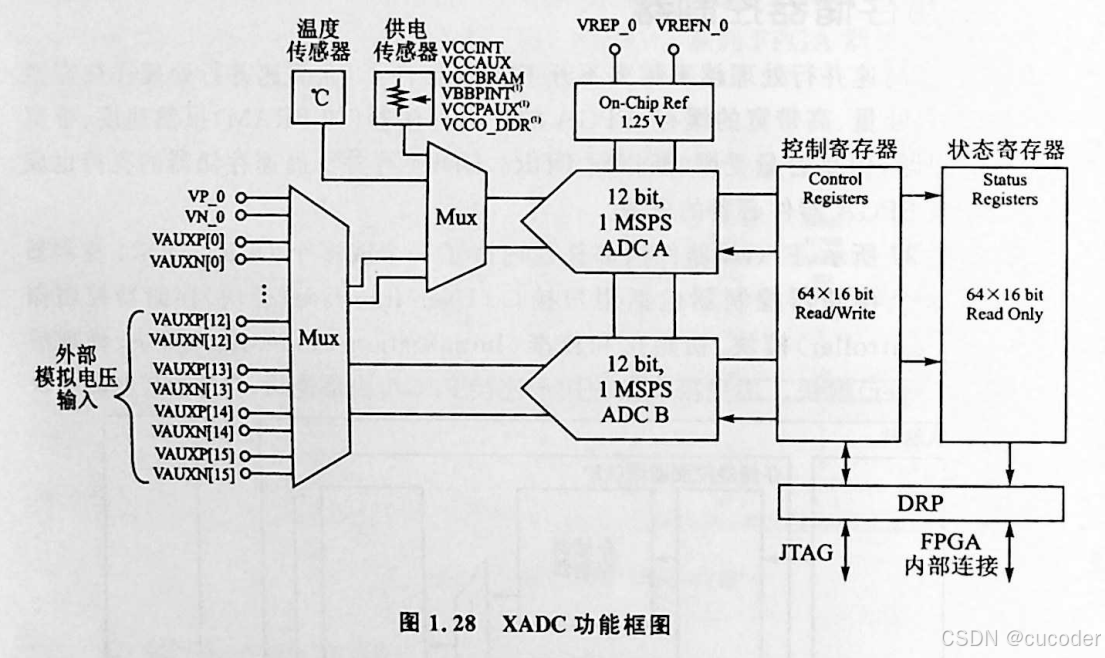

6.模拟数字转换模块。

可配置逻辑块

虽然今天的FPGA通常还包含了丰富的时钟资源、IO资源、乘法器资源、RAM资源甚至一些特殊的硬核IP块,但是逻辑资源依然是FPGA的安身立命之本。CLB是最基本的FPGA逻辑资源。

下面以Xilinx 7系列的可配置逻辑块为例进行讲解:

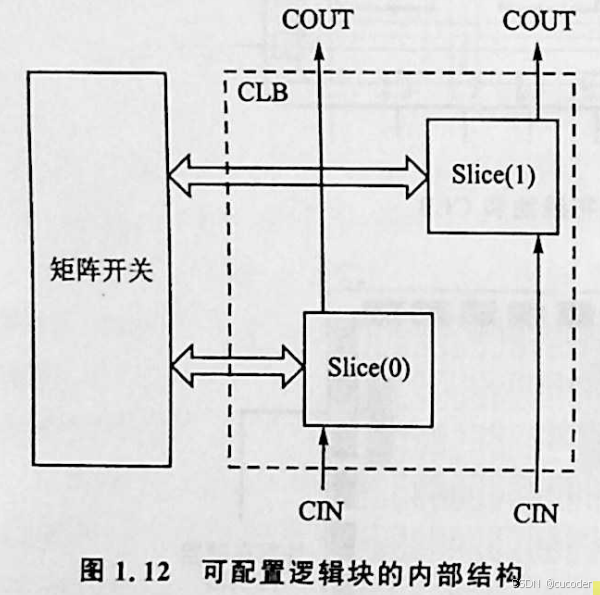

CLB内部主要由2个更小的单元Slice组成。每个Slice都有独立的高速进位链以及独立的布线通道连接到矩阵开关,通过矩阵开关可以实现Slice与FPGA大布线池之间的灵活编程。

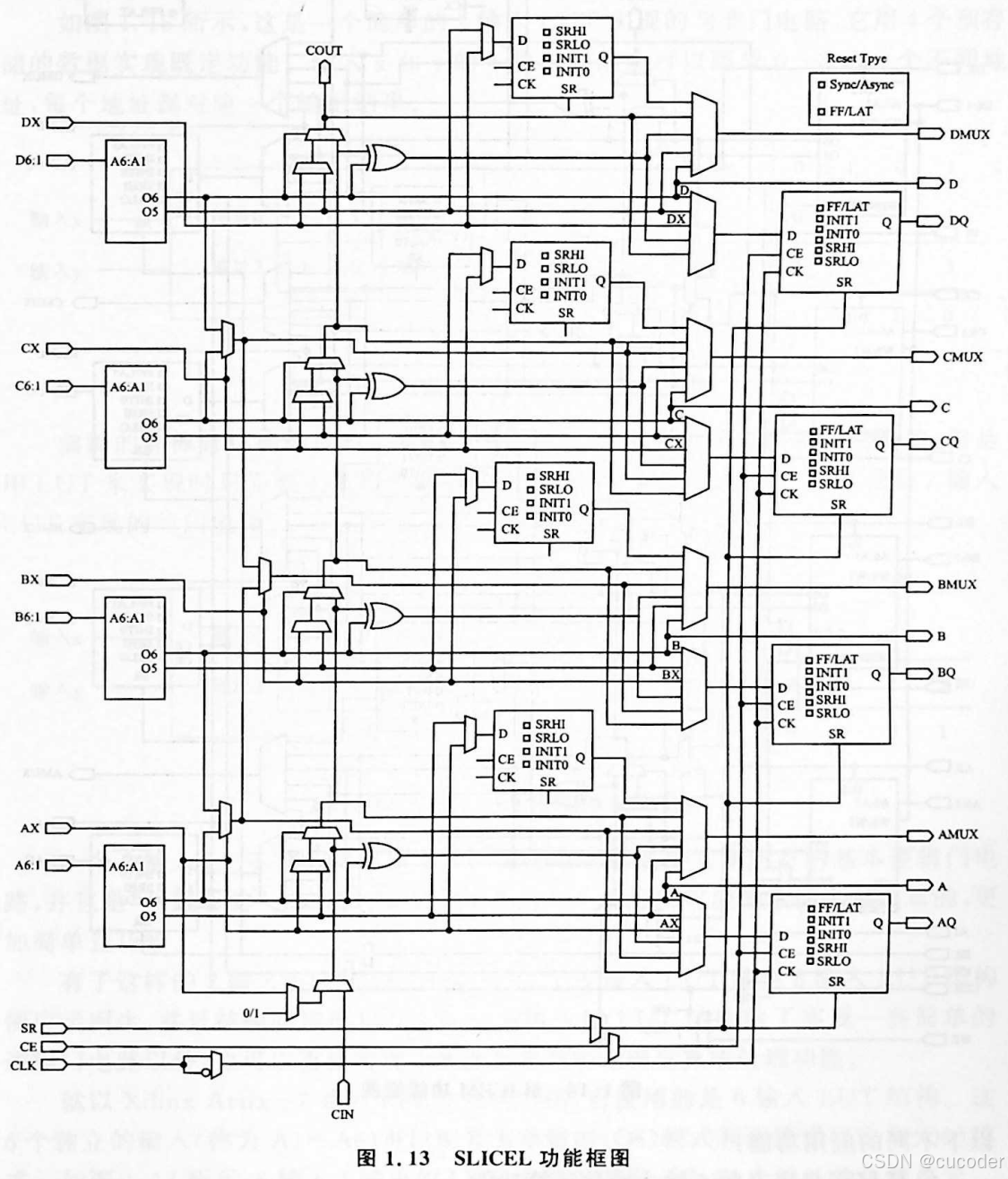

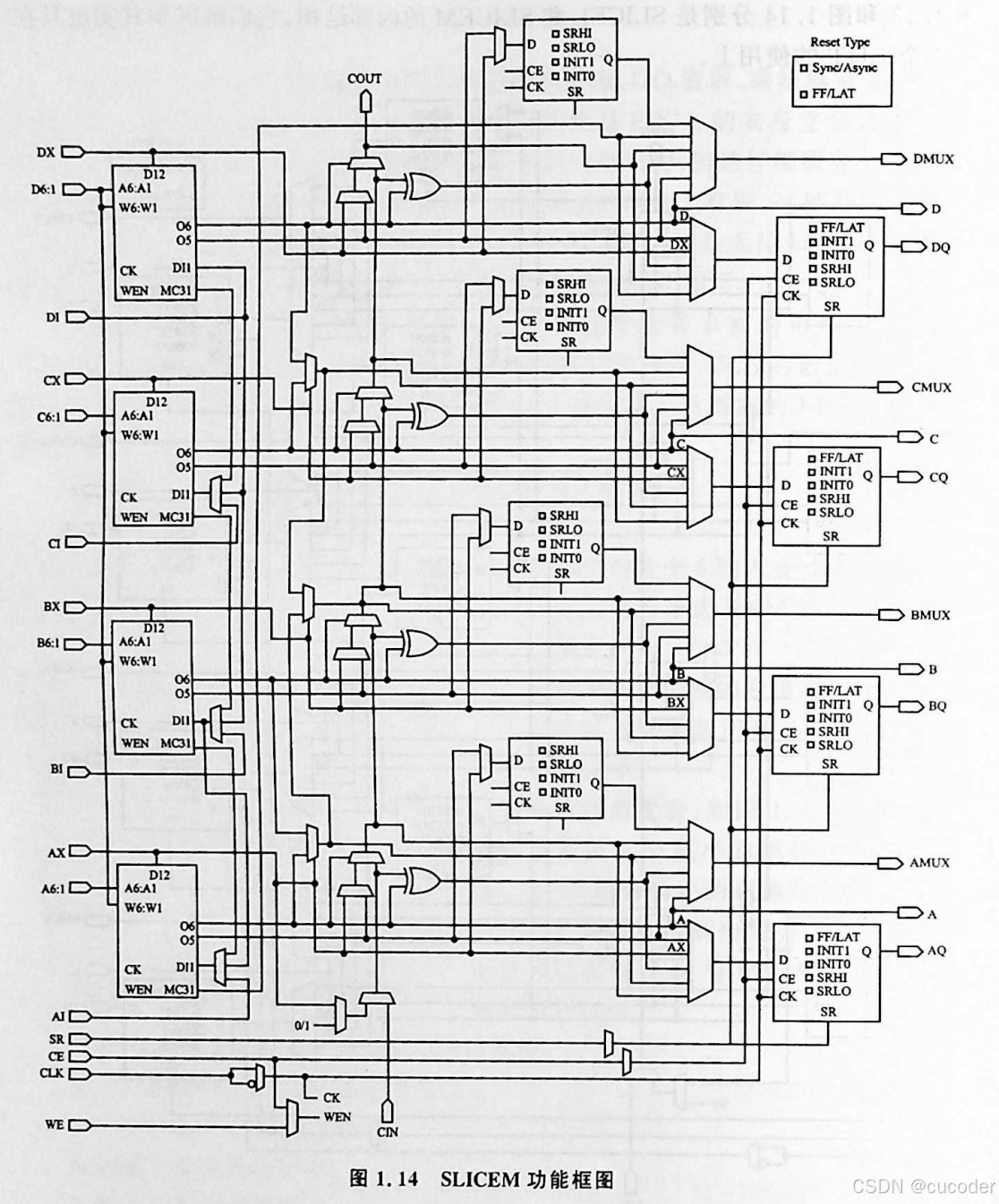

每个Slice单元则还包含了以下更小的功能块:4个逻辑功能的发生器(或查找表),8个存储单元(触发器),功能丰富的复用开关以及用于运算的进位链。所有Slice的这些功能块地可以用于支持逻辑、运算或ROM功能,此时我们称之为SLICEL;某些Slice可以支持最大256位数据存储的分布式RAM或最大32个8位宽的移位寄存器,此时我们称之为SLICEM。由于Slice内部的4个LUT本身就是一种存储器实现的结构,所以可以被轻易设计成ROM、RAM或移位寄存器功能。

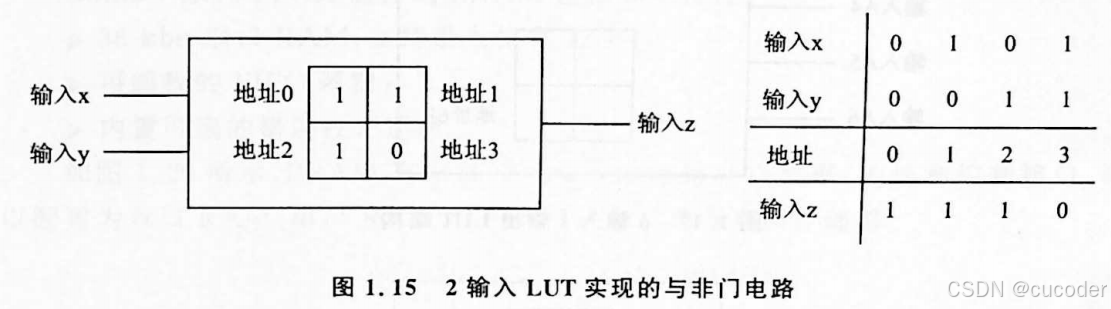

查找表(LUT)是用于执行最基本的逻辑操作的单元,触发器适用于存储LUT操作结果的寄存器单元。FPGA内部的LUT结构可用于设计出一张张结果已知的查找表,这个表存储着和不同输入对应的所有可能结果。每一个不同的输入在这个查找表中都对应一个唯一的地址,这个地址也有唯一的输出。比如一个2输入LUI实现的与非门电路。输入x,y组合成4个不同的地址,然后将地址的结果送到输出z上面。对于多输入的LUT结构,除了可以实现一些简单的逻辑门电路以外,也可以直接实现一些更为复杂的逻辑运算或处理功能。

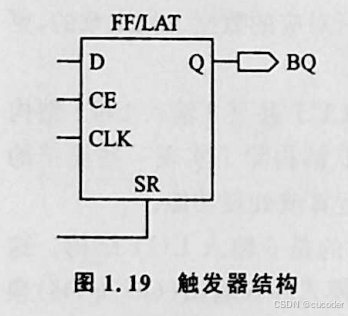

触发器也是FPGA内部基本的存储单元,触发器单元通常用于配对LUT进行逻辑流水线处理和数据存储。基本的触发器结构包括一个数据输入,一个时钟输入,一个时钟使能信号,一个复位信号和一个数据输出。正常操作过程中,数据输入端口上的任何值在每个时钟上升沿将被锁存并送到输出端口上。时钟使能信号是为了使触发器能够连续在多个时钟周期内保持某个固定电平值。

片内存储器

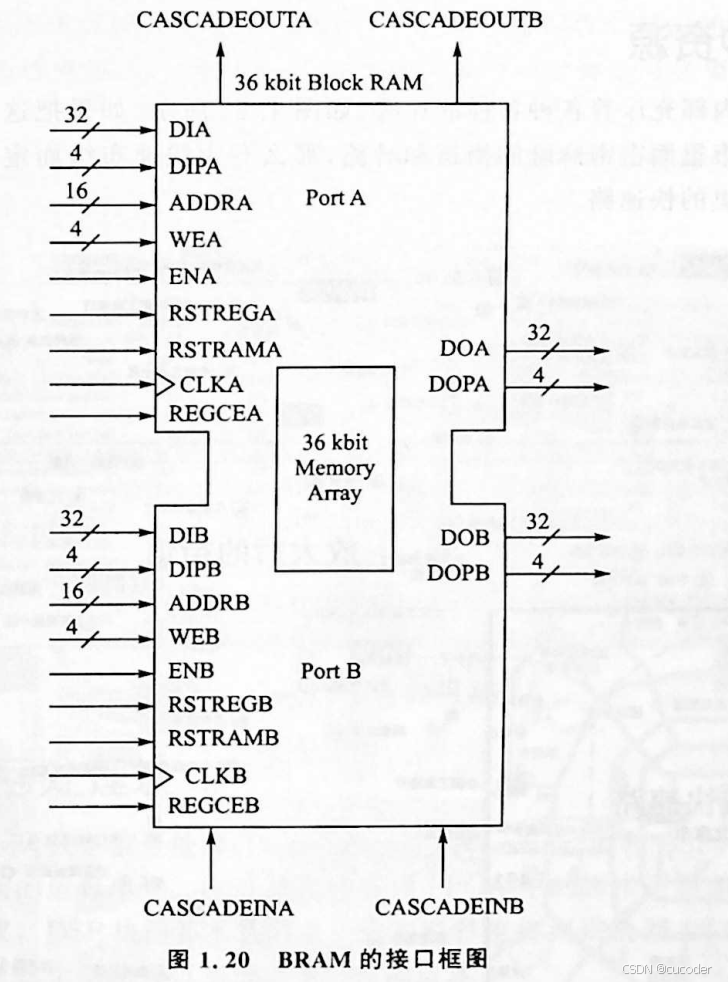

FPGA内嵌的存储单元包括块RAM(BRAM)和分布式RAM,它们都可以用于随机存取存储器(RAM)、只读存储器(ROM)或移位寄存器。分布式RAM是基于CLB的查找表,而块RAM是内嵌于FPGA的双口RAM。BRAM的双口特性使其在同一个时钟周期可以并行访问两个不同的地址单元。如下图所示,BRAM有风度的可编程的两组独立数据、地址和控制接口,可以配置为双口RAM、单口RAM、FIFO、移位寄存器等常用存储器。

时钟资源

如果将FPGA内部充斥着的各种连线比喻为大城市里的街道和马路,那么专为快速布线而定制的时钟布线资源则是城市里的快速路。FPGA内部的时钟布线池是横平竖直的矩阵式排布,意图让每一条“小路”都能够尽快找到上高速的匝道。

FPGA的开发工具通常在编译综合过程中会自动识别代码中的一些时钟信号和高扇出信号,在实现过程中将其布线布置到“时钟布线资源”。Xilinx FPGA内部将时钟布线资源划分到不同的“时钟区”,它对应一定的IO数量、逻辑资源、存储器资源或DSP SLices资源,同时也会有一个时钟管理单元(CMT),这个CMT包含一个混合时钟管理器(MMCM)和一个锁相环(PLL),用于产生不同频率的时钟、去时钟偏斜、时钟抖动滤波等功能。

数字信号处理块

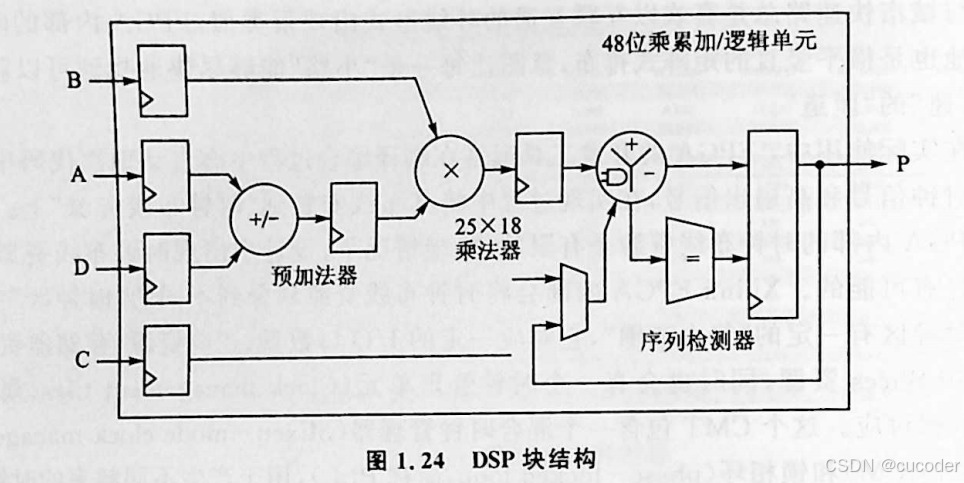

数字信号处理(DSP)块是Xilinx FPGA内部最复杂的运算单元。DSP块是内嵌到FPGA中的算术逻辑单元,由3个不同的链路块组成。DSP块的算术链路由一个加法器连接到乘法器,再连接到一个乘累加器所组成。这个链路可以实现如下公式的运算:P=A*(B+D)+C与P+=A*(B+D)。

高速串行收发器

FPGA的IO接口支持丰富的电平标准和协议,尤其是对高速差分对的支持,从几百MHz的普通LVDS接口,到上GHz或数十GHz的Gbit串行收发器,可以满足各种高数数据传输的需求。

外部存储器控制器

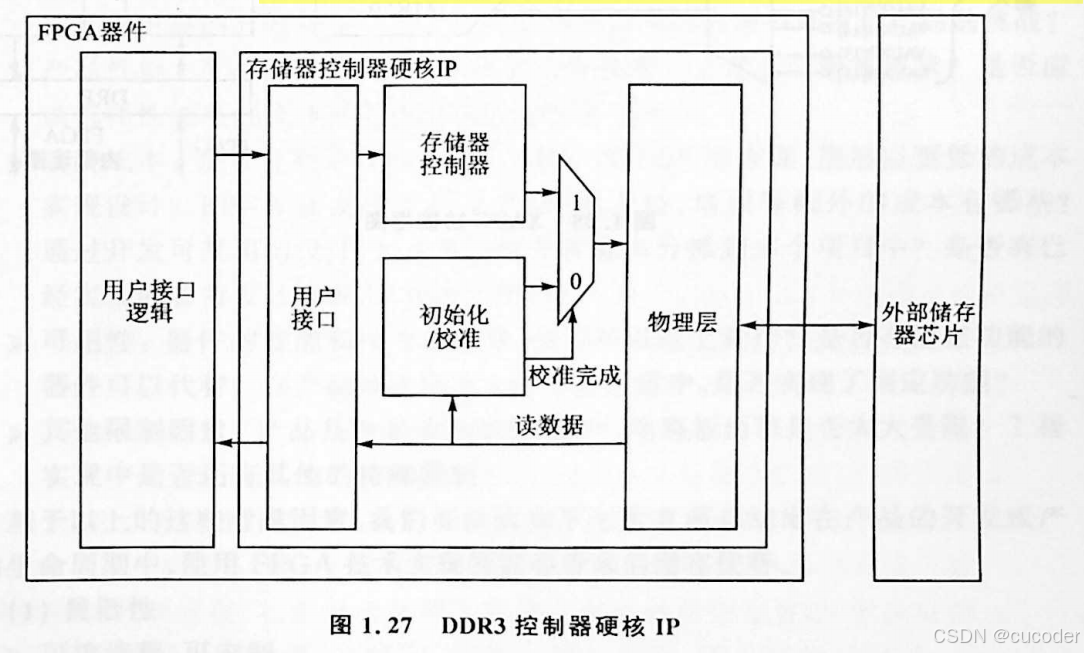

高速并行处理往往需要大容量、高吞吐量、高带宽的缓存,FPGA的片内存储器(如BRAM)虽然速度、带宽上不是问题,但是容量受到限制,搜易对DDR3、DDR4等外部高速存储器的支持也是FPGA器件必备的资源(中高端)。

FPGA器件内部往往内嵌了一个或多个DDR3、DDR4控制器硬核IP。这个存储器控制器包括用户接口模块,存储器控制器模块、初始化和校准模块、物理层模块。用户接口模块用于连接FPGA内部逻辑,存储器控制器模块用于实现外部存储器芯片的主要读/写时序和数据缓存交互,初始化/校准模块用于实现外部存储器芯片的上电初始化配置以及时序校准,物理层模块则用于实现和外部存储器芯片的接口。

模拟/数字转换模块

Xilinx FPGA器件特有的ADC模块创新性地将模拟信号处理混合到FPGA器件中,便于对板级模拟信号进行采集、处理以及对板级温度、电源电压的监控。

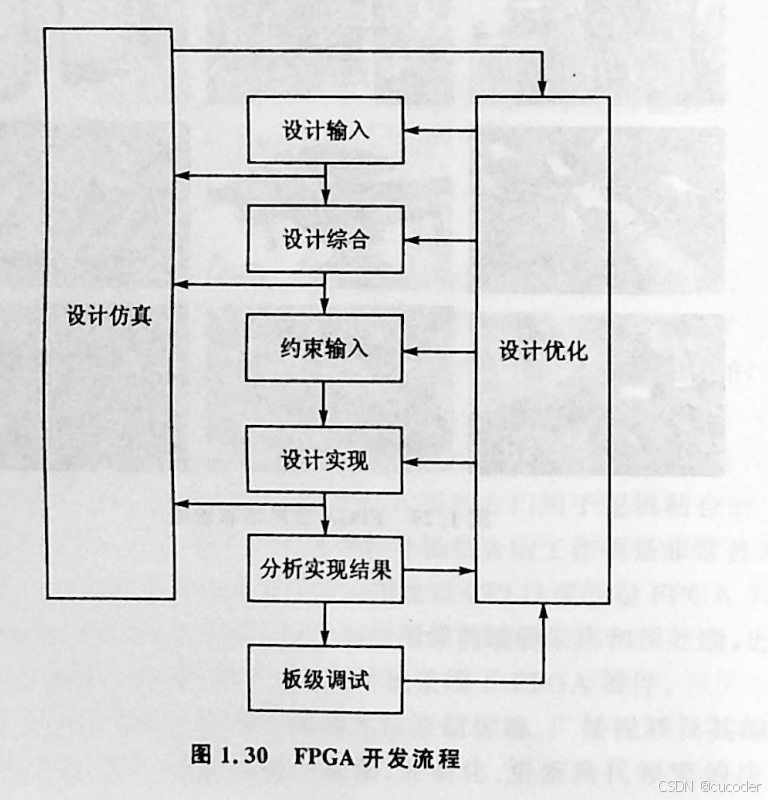

3.FPGA开发流程

设计输入阶段:设计者需要创建FPGA工程,并且创建或添加设计源文件到工程中。

设计综合阶段:FPGA开发工具的综合引擎将编译整个设计,并将HDL源文件转译为特定结构的设计网表。

约束输入阶段:设计者可以通过指定时序、布局布线或其他的设计要求。

设计仿真阶段:设计者可以使用仿真工具对FPGA工程进行功能验证。

设计实现阶段:设计综合之后,可以接着进行设计实现,将逻辑设计进一步转译为可以被下载烧录到目标FPGA器件中的特定物理文件格式。

分析实现结果:设计实现后,必须对设计约束、器件资源占用率、实现结果以及功耗等设计性能进行分析。

设计优化阶段:基于对设计结果的分析,设计者可以对设计源文件、编译属性或设计约束进行修改,然后重新综合、是西安以达到设计最优化。

End!

本文资料主要来源于《深入浅出玩转FPGA》一书,感兴趣的读者可以查阅本书获得更为详细的信息,欢迎勘误和探讨。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?