前言:这里只写了从一个设备,向另外一个主设备(比如CPU的MEM)发送请求包的过程,所以我这里也只分析了PCIE_TX的monitor的思路,后续再补上返回包过程(PCIE_RX的driver)

一:关于PCIE TLP包的格式基础知识

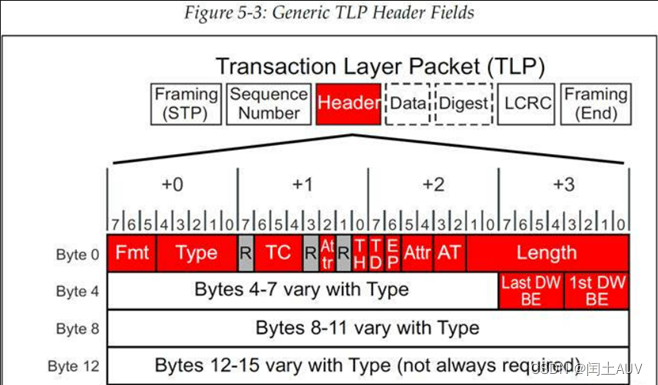

1 PCIE事务层TLP包格式:

(知道红色部分的Header与Date就行)

2 其中Header具体格式为:

(主要关心前两行的fmt、type和length即可,后两行是目标地址,分为32位和64位)

3 其中fmt信号:

(理解一个TLP包包括很多数据包,一个数据包是256位,一个DW是32位,所以一个数据包是8DW,上面图Header部分占了4DW,其余的全是Date部分)

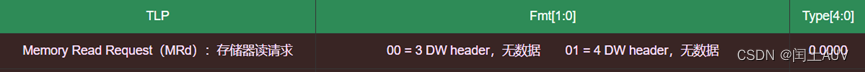

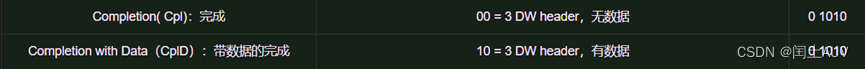

4 Type信号:

(以下只写出关于存储器读写和返回包类型)

![]()

![]()

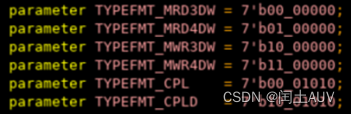

二:PCIE UVC代码内容解析

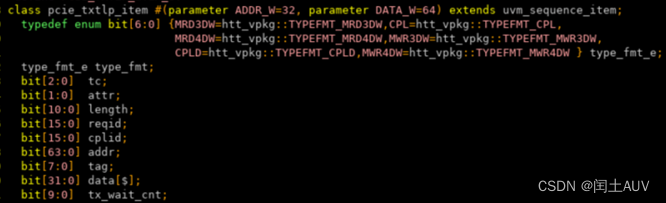

1 Pcie_uvc中:

(把type和fmt一起定义为参数类型)

2 包的内容:

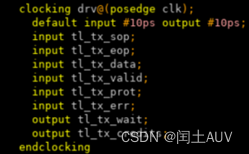

3接口信号:

(sop拉高表示TLP包的开始,eop拉高表示TLP包的结束,data是TLP包整个内容,valid[7:0]对应一个数据包有效DW,每个DW是32位,一个数据包是256位也就是8DW,wait是等待信号)

(sop拉高表示TLP包的开始,eop拉高表示TLP包的结束,data是TLP包整个内容,valid[7:0]对应一个数据包有效DW,每个DW是32位,一个数据包是256位也就是8DW,wait是等待信号)

4 run_phase:

(这里是pcie_tx的monitor核心代码)

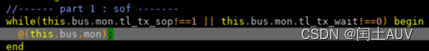

4.1

当sop有效并且没有wait信号时,开始去分解包和产生包

当sop有效并且没有wait信号时,开始去分解包和产生包

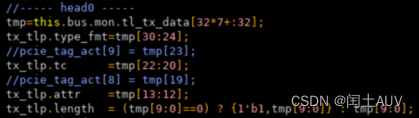

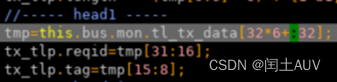

4.2

包的前两个DW拆分,得到变量type、fmt、tc、attr、length、reqid、tag;其中重点关心type、fmt(两个组成一个变量),length就行

包的前两个DW拆分,得到变量type、fmt、tc、attr、length、reqid、tag;其中重点关心type、fmt(两个组成一个变量),length就行

4.3

![]()

![]() 根据type_fmt去分析地址是32位的还是64位,分别对应data拆分第三个DW还是第三个加第四个DW

根据type_fmt去分析地址是32位的还是64位,分别对应data拆分第三个DW还是第三个加第四个DW

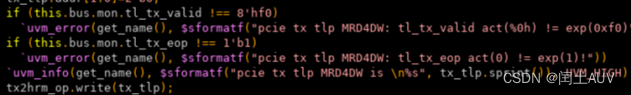

4.4

从上面基础知识中知道存储器读请求不带数据,所以valid在只有4DW有效的情况下是8'hf0,3DW情况下为8‘he0,并且eop在该时钟沿下也拉高

从上面基础知识中知道存储器读请求不带数据,所以valid在只有4DW有效的情况下是8'hf0,3DW情况下为8‘he0,并且eop在该时钟沿下也拉高

4.5

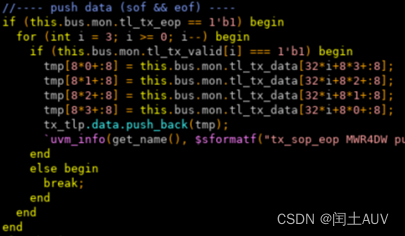

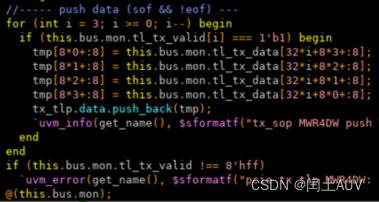

![]()

写请求携带数据,数据长度由length[10:0]决定,也确定了eop在何时拉高。(要注意一个TLP包只能携带4KB有效数据,所以length最高是10000000000,就是4KB),后面根据sop和eop的拉高情况拆分我们的有效数据

写请求携带数据,数据长度由length[10:0]决定,也确定了eop在何时拉高。(要注意一个TLP包只能携带4KB有效数据,所以length最高是10000000000,就是4KB),后面根据sop和eop的拉高情况拆分我们的有效数据

sof+eof:只有一个数据包,然后根据valid去确定具体哪些有效;

sof+!eof:数据包大于一个,第一个包8DW都有效,所以valid必须是8‘hff;从第二个包开始sof为0,然后等到eof为1,不然就一直拆数据给变量data;

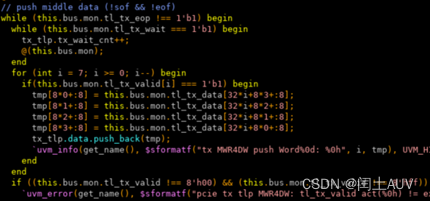

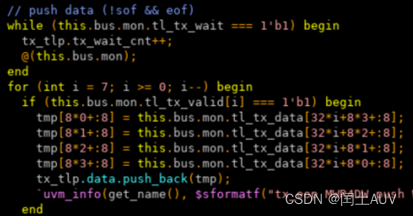

代码如下:

![]() 当type为3DW时一样的分析。

当type为3DW时一样的分析。

4.6

![]() 最后把包广播出去即可

最后把包广播出去即可

三:总结

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?