任何一种信号都是共模与差模的结合,要区分是差模还是共模,具体就是要看参考的信号是多少。对于比较器和运放来说,一般而言都是取GND为参考电压,此时如果运放一端是V1,一端是V2,那么此时输入共模信号就是(V1+V2)/2,差模信号为(V1-V2)/2。

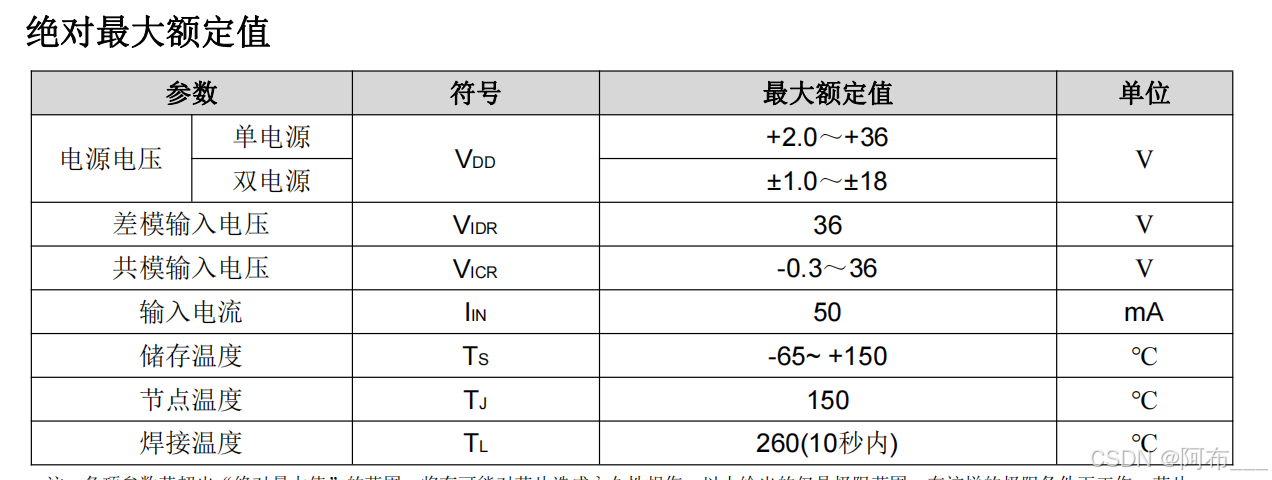

如上图LM393的datasheet中提供的差模输入电压和共模输入电压,在使用器件的过程中要保证不超过该最大值,比如最大差模输入电压为36V,那么在IN+和IN-两端就不能超过36V,同样共模电压最大36V也是如此。如果IN+=48V,IN-=15V,那么此时也是符合要求的,因为差模电压为48-15=33V,共模输入电压为(48+15)/2=31.5V。

1520

1520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?