- 实验目的

- 通过实验观察,发现 Basys3 的四个七段数码管中的各个发光二极管码段的性能对实验方案的约束。

- 利用实验一中的经验,判断刷新周期(四个数码管循环点亮一次的时间叫做刷新周期)取值下限。

- 学会使用触发器分频。

- 意识到人眼局限性也是可以利用的。

- (进阶要求)使用编码器和/或数据选择器等器件,合理改造电路,减少实验测试时刷写Basys3 的次数。

- 实验仪器设备

软件:Multisim 14.1 Education Edition

软件:Xilinx ISE

硬件:Digilent Basys 3

- 实验设计过程

基本要求:

以 16 位拨码开关作为输入(4 组BCD码),4 位数码管为输出,四个七段式数码管为输出,设计电路使得输入的四个七段式数码管能同时独立地显示正确的字型。

步骤如下:

- 用1个时钟信号驱动触发器,使得“触发器输出+CLK输入”这2位二进制数按照…00→01→10→11→00→…的规律变化。使用 Multisim 14.1 Education Edition 仿真验证即可。

- 将这两位接入到实验三的实验电路中的 BTNL 和 BTNR。

- 将板载 100MHz(10ns)的 CLK 作为时钟源,观察显示效果。

- 使用触发器实现分频,降低时钟频率,直至显示效果令人满意即无闪烁或者拖影。

进阶要求:

在不同刷新周期下,观察显示效果,给出刷新周期的合理范围,设法避免多次刷写 Basys3。尝试设计电路,利用 BTN 按键,一次刷写 Basys3 就可以同时测试多个分频倍数,以减少等待时间。大致判断刷新周期的合理范围。

实验设计思路:

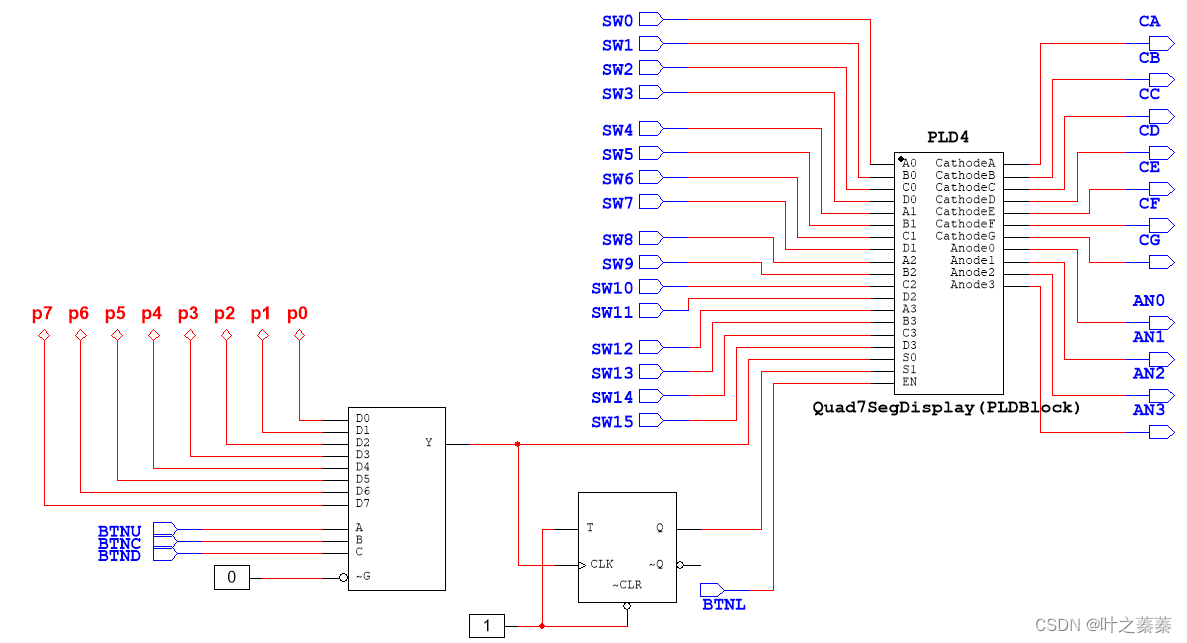

将实验三原本选择数码管输出信号的BTNL和BTNR改为两个时钟信号,其中一个信号的频率是另一个的二分之一,达到二位二进制输入的效果。再将板载的CLK用多个T触发器分频,将不同频率的时钟信号作为被选信号,接入数据选择器,用BTNU、BTNC、BTND三个按键进行三位二进制输入,测试不同频率的时钟信号。

实验步骤:

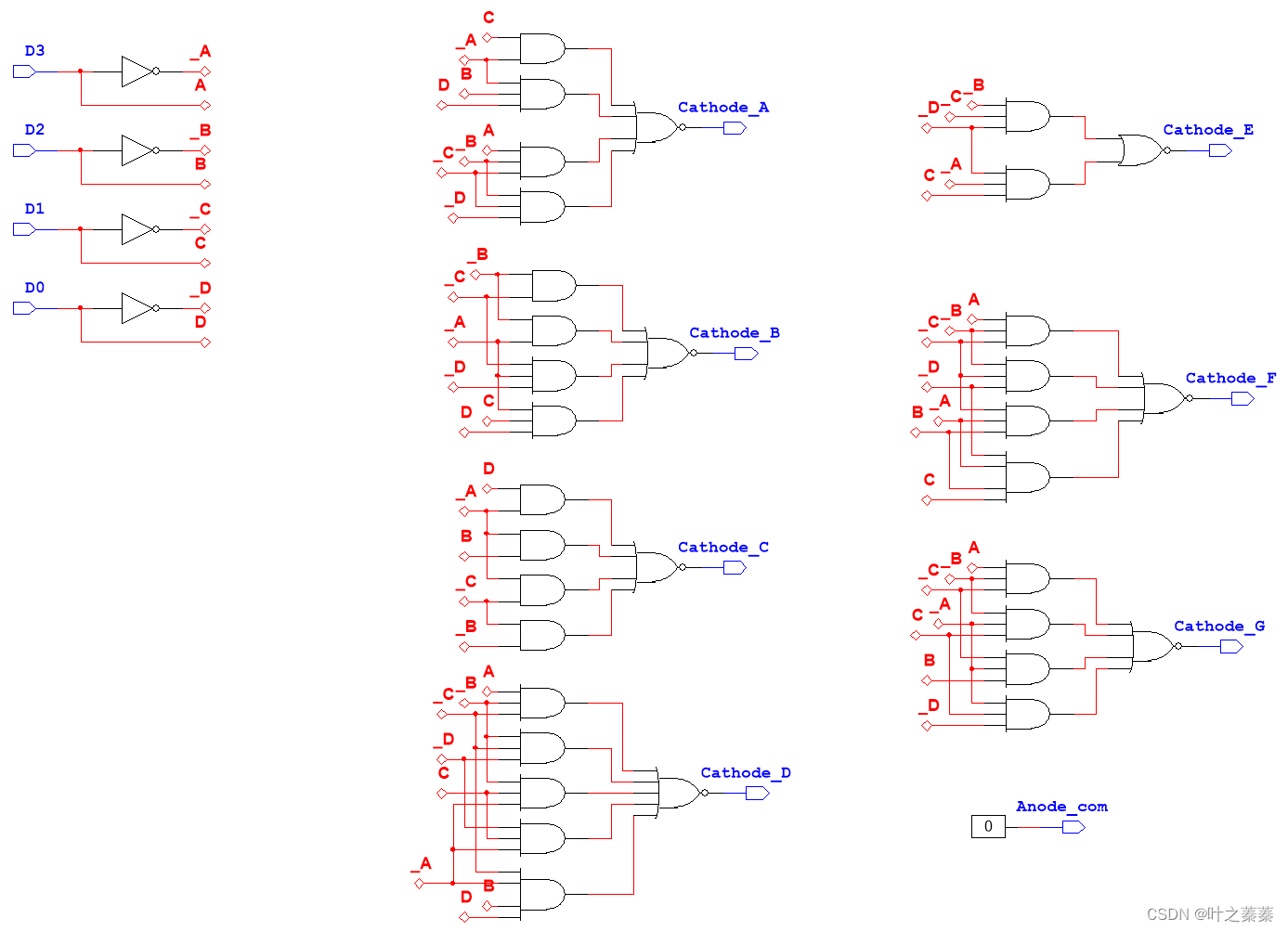

1完成BCDtoSevenSegDisplay(PLDBlock).ms14,跟前面的实验一样,画真值表,卡诺图,确定每段数码管表达式,连接电路。

2完成Quad7SegDisplay(PLDBlock).ms14,跟实验三一样,将对应的网络接入选择器。

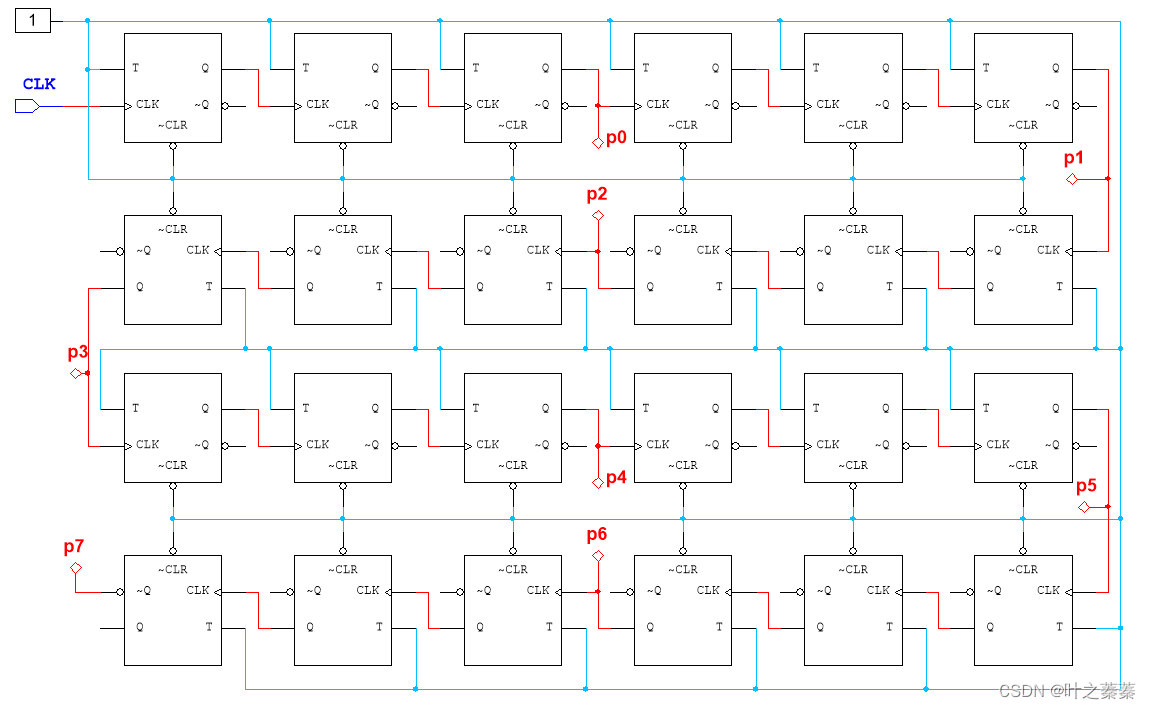

3完成SimutanouslndependentDisplay.ms14,先对CLK进行分频,在不同频率处设置在页连接器(每三个触发器接一个),

再设计频率选择器,将时钟信号依次接入。

如图完成设计。

2740

2740

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?