ADC:Analog-to-Digital Converter的缩写。指模/数转换器或者模拟/数字转换器。是指将连续变量的模拟信号转换为离散的数字信号的器件。典型的模拟数字转换器将模拟信号转换为表示一定比例电压值的数字信号。

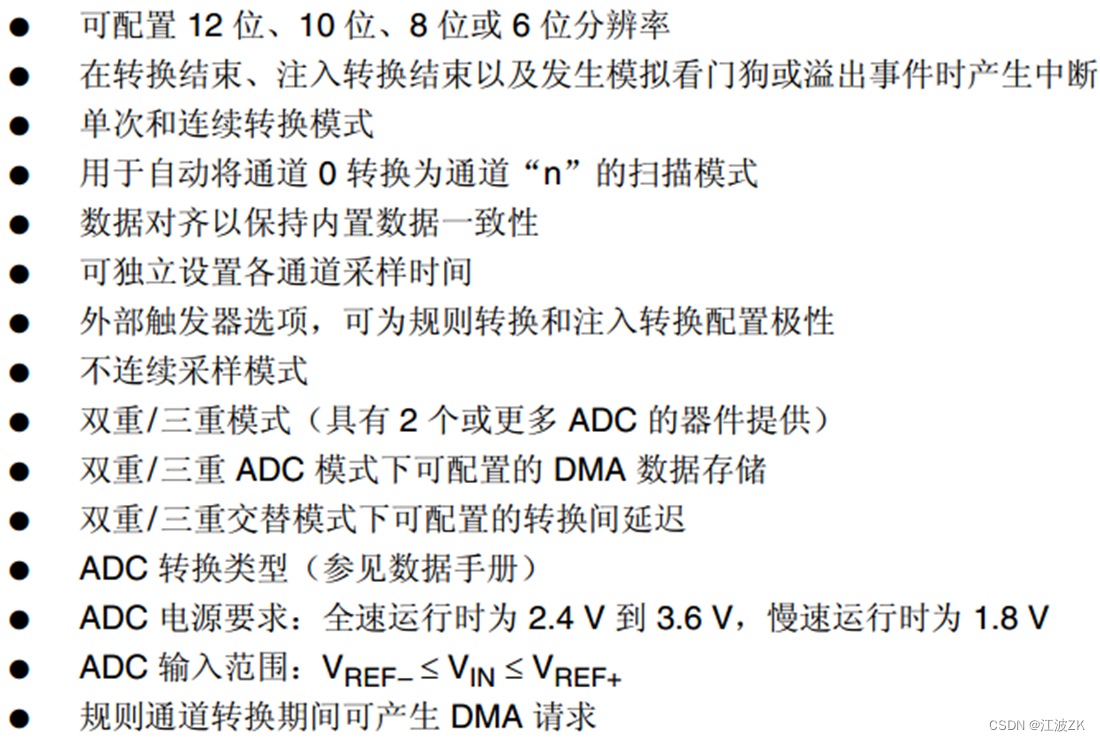

STM32F4x ADC特点:

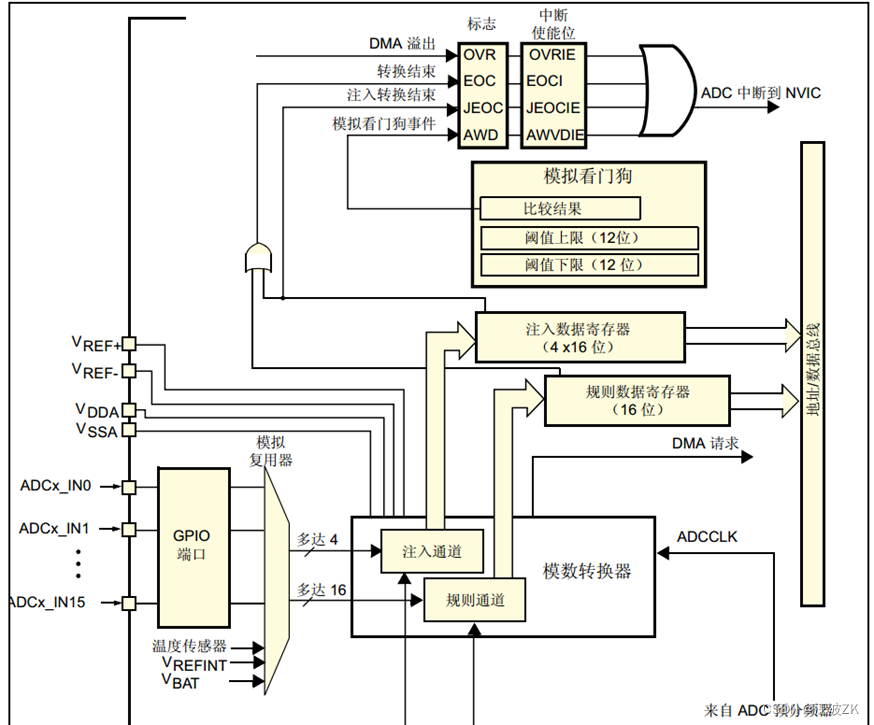

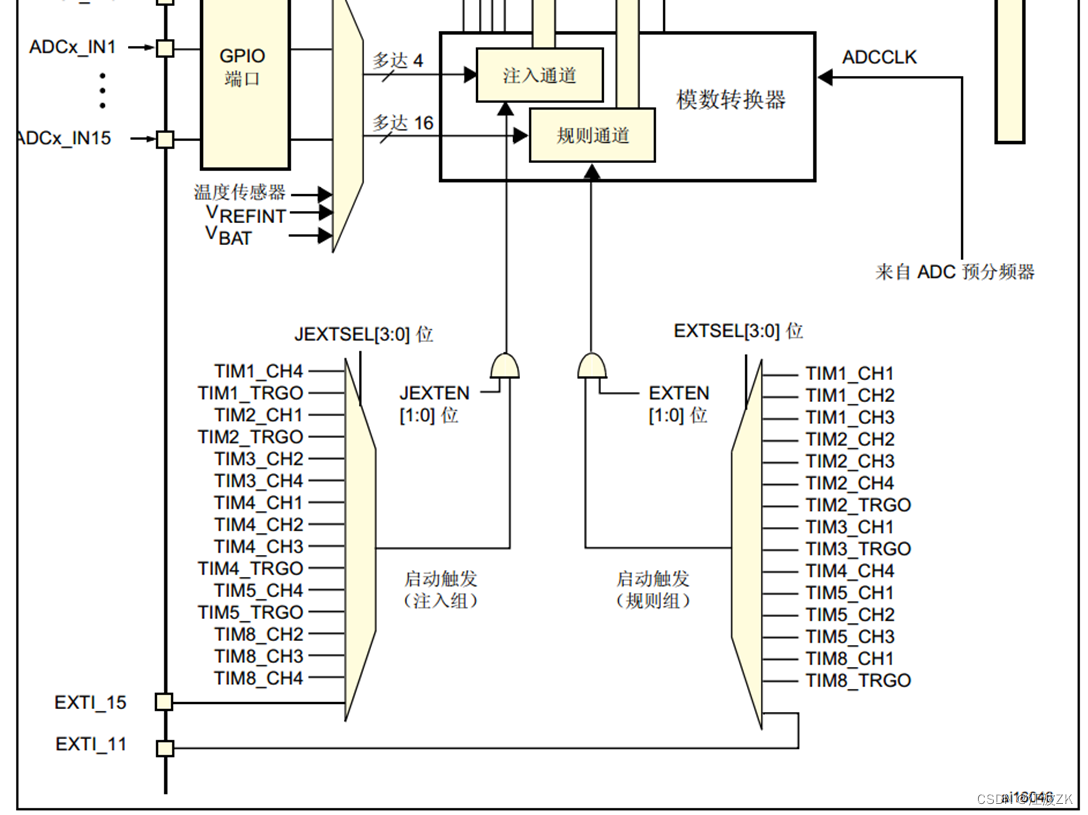

ADC框图

STM32F4 的 ADC 是 12 位逐次逼近型的模拟数字转换器。它有 19 个通道, 可测量 16 个外部源、2 个内部源和 Vbat 通道的信号。这些通道的 A/D 转换可以单次、连续、 扫描或间断模式执行。ADC 的结果可以左对齐或右对齐方式存储在 16 位数据寄存器中。 模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。

STM32F407ZGT6 包含有 3 个 ADC。STM32F4 的 ADC 最大的转换速率为 2.4Mhz,也就是 转换时间为 0.41us(在 ADCCLK=36M,采样周期为 3 个 ADC 时钟下得到),不要让 ADC 的时 钟超过 36M,否则将导致结果准确度下降。

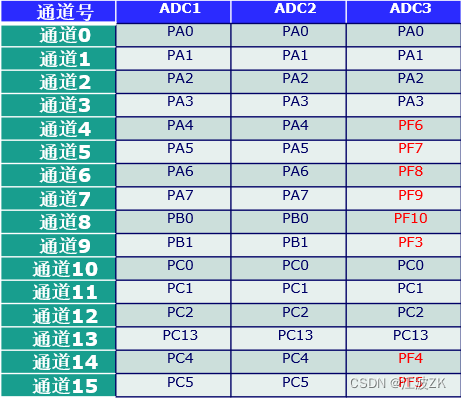

STM32F40x系列ADC外部通道和引脚对应关系

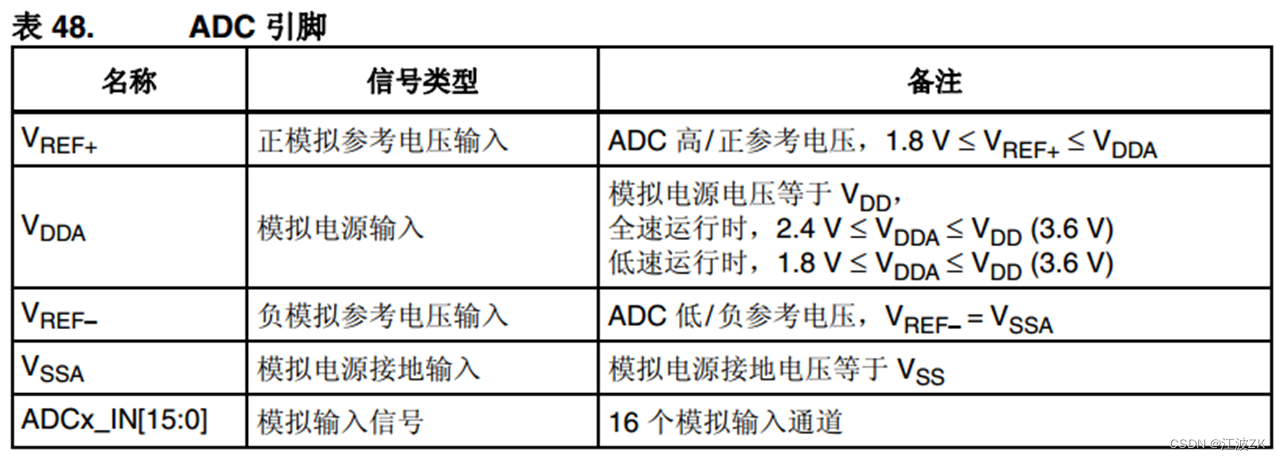

ADC引脚

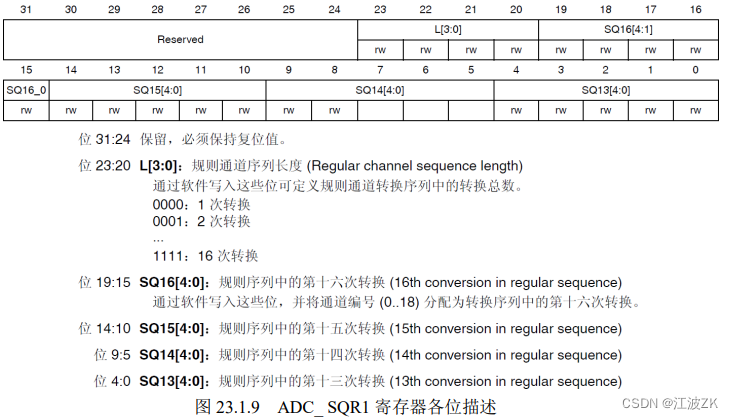

STM32通道组

①规则通道组:相当正常运行的程序。最多16个通道。规则通道和它的转换顺序在ADC_SQRx寄存器中选择,规则组转换的总数应写入ADC_SQR1寄存器的L[3:0]中。

② 注入通道组:相当于中断。最多4个通道。注入组和它的转换顺序在ADC_JSQR寄存器中选择。注入组里转化的总数应写入ADC_JSQR寄存器的L[1:0]中

STM32F4 将 ADC 的转换分为 2 个通道组:规则通道组和注入通道组。规则通道相当于你 正常运行的程序,而注入通道呢,就相当于中断。在你程序正常执行的时候,中断是可以打断 你的执行的。同这个类似,注入通道的转换可以打断规则通道的转换, 在注入通道被转换完成 之后,规则通道才得以继续转换。

单次转换模式

在单次转换模式下,ADC 执行一次转换。CONT 位为 0 时,可通过以下方式启动此模式:

将 ADC_CR2 寄存器中的 SWSTART 位置 1(仅适用于规则通道)

将 JSWSTART 位置 1(适用于注入通道)

外部触发(适用于规则通道或注入通道)

完成所选通道的转换之后:

如果转换了规则通道:

转换数据存储在 16 位 ADC_DR 寄存器中

EOC(转换结束)标志置 1

EOCIE 位置 1 时将产生中断

如果转换了注入通道:

转换数据存储在 16 位 ADC_JDR1 寄存器中

JEOC(注入转换结束)标志置 1

JEOCIE 位置 1 时将产生中断

然后,ADC 停止。

连续转换模式

在连续转换模式下,ADC 结束一个转换后立即启动一个新的转换。CONT 位为 1 时,可通过外部触发或将 ADC_CR2 寄存器中的 SWSTRT 位置 1 来启动此模式(仅适用于规则通道)。

每次转换之后:

如果转换了规则通道组:

上次转换的数据存储在 16 位 ADC_DR 寄存器中

EOC(转换结束)标志置 1

EOCIE 位置 1 时将产生中断

注意: 无法连续转换注入通道。连续模式下唯一的例外情况是,注入通道配置为在规则通道之后自动转换(使用 JAUTO 位)。

扫描模式

此模式用于扫描一组模拟通道。 通过将 ADC_CR1 寄存器中的 SCAN 位置 1 来选择扫描模式。将此位置 1 后,ADC 会扫描 在 ADC_SQRx 寄存器(对于规则通道)或 ADC_JSQR 寄存器(对于注入通道)中选择的 所有通道。为组中的每个通道都执行一次转换。每次转换结束后,会自动转换该组中的下一 个通道。如果将 CONT 位置 1,规则通道转换不会在组中最后一个所选通道处停止,而是再次从第一个所选通道继续转换。

如果将 DMA 位置 1,则在每次规则通道转换之后,均使用直接存储器访问 (DMA) 控制器将 转换自规则通道组的数据(存储在 ADC_DR 寄存器中)传输到 SRAM。

在以下情况下,ADC_SR 寄存器中的 EOC 位置 1:

如果 EOCS 位清零,在每个规则组序列转换结束时

如果 EOCS 位置 1,在每个规则通道转换结束时

从注入通道转换的数据始终存储在 ADC_JDRx 寄存器中。

ADC 控制寄存器(ADC_CR1 和 ADC_CR2)

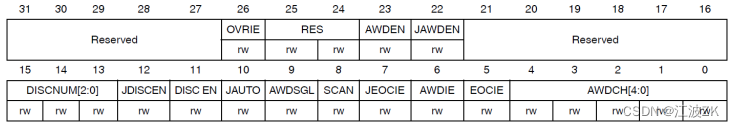

ADC_CR1

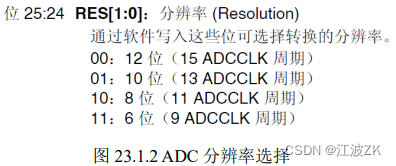

ADC_CR1 的 SCAN 位,该位用于设置扫描模式,由软件设置和清除,如果设置为 1,则使用扫描模式,如果为 0,则关闭扫描模式。在扫描模式下,由 ADC_SQRx 或 ADC_JSQRx 寄 存器选中的通道被转换。如果设置了 EOCIE 或 JEOCIE,只在最后一个通道转换完毕后才会产 生 EOC 或 JEOC 中断。 ADC_CR1[25:24]用于设置 ADC 的分辨率

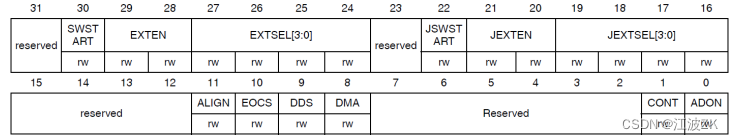

ADC_CR2

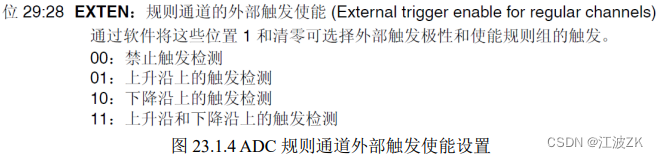

ADON 位用于开关 AD 转换器。而 CONT 位用于 设置是否进行连续转换,ALIGN 用于设置数据对齐,使用右对齐,该位设置为 0。 EXTEN[1:0]用于规则通道的外部触发使能设置

ADC_CR2 的 SWSTART 位用于开始规则通道的转换,我们每次转换(单次转换模式下)都需要向该位写 1。

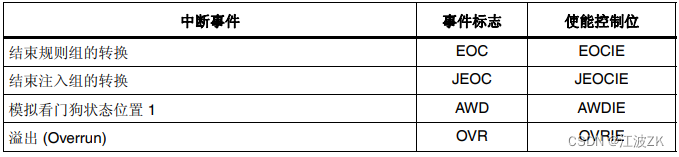

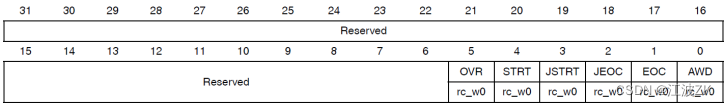

ADC 中断

当模拟看门狗状态位和溢出状态位分别置 1 时,规则组和注入组在转换结束时可能会产生中断。可以使用单独的中断使能位以实现灵活性。

ADC_SR 寄存器中存在另外两个标志,但这两个标志不存在中断相关性:

JSTRT(开始转换注入组的通道)

STRT(开始转换规则组的通道)

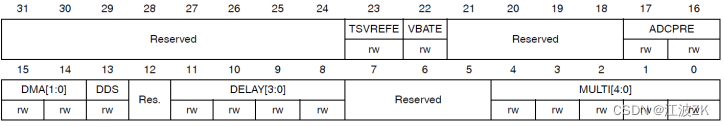

ADC 通用控制寄存器 (ADC_CCR)

TSVREFE 位是内部温度传感器和 Vrefint 通道使 能位,这里我们直接设置为 0。ADCPRE[1:0]用于设置 ADC 输入时钟分频,00~11 分别对应 2/4/6/8 分频,STM32F4 的 ADC 最大工作频率是 36Mhz, 而 ADC时钟(ADCCLK)来自 APB2,APB2频率一般是 84Mhz,所以我们一般设置 ADCPRE=01, 即 4 分频,这样得到 ADCCLK 频率为 21Mhz。

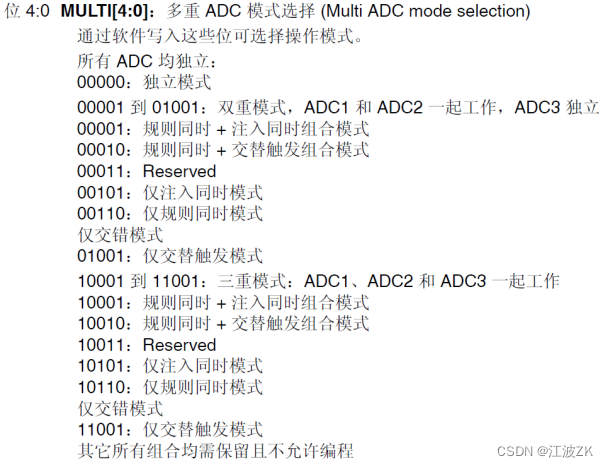

MULTI[4:0]用于多重 ADC 模式选择

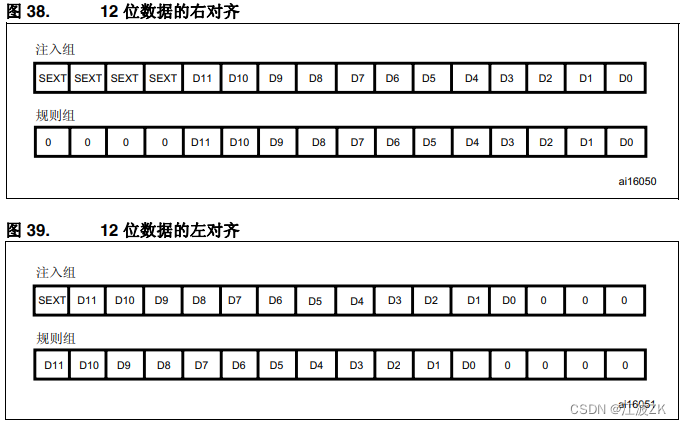

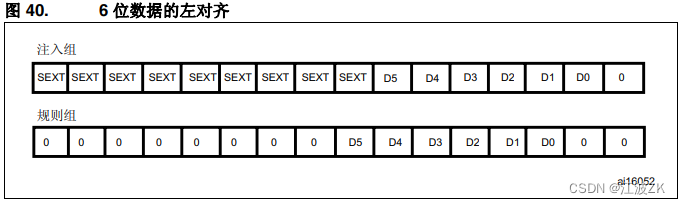

数据对齐

ADC_CR2 寄存器中的 ALIGN 位用于选择转换后存储的数据的对齐方式。可选择左对齐和 右对齐两种方式。 注入通道组的转换数据将减去 ADC_JOFRx 寄存器中写入的用户自定义偏移量,因此结果可 以是一个负值。SEXT 位表示扩展的符号值。 对于规则组中的通道,不会减去任何偏移量,因此只有十二个位有效。

特例:采用左对齐时,数据基于半字进行对齐,除了分辨率设置为 6 位时。分辨率设置为 6 位 时,数据基于字节进行对齐。

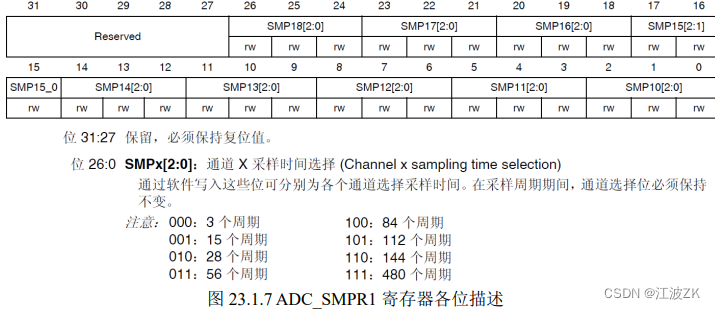

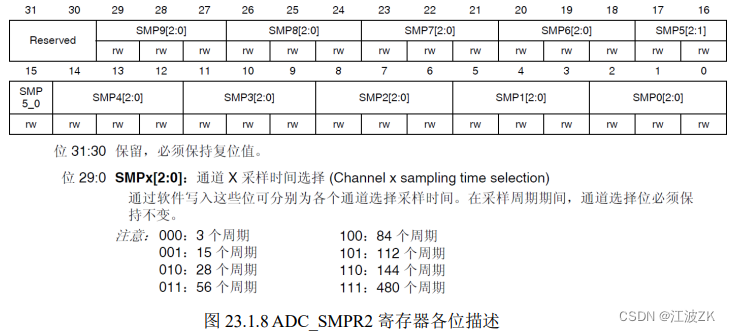

ADC 采样时间寄存器(ADC_SMPR1 和 ADC_SMPR2),这两个寄存器 用于设置通道 0~18 的采样时间,每个通道占用 3 个位。

ADC_SMPR1

ADC_SMPR2

对于每个要转换的通道,采样时间建议尽量长一点,以获得较高的准确度,但是这样会降低 ADC 的转换速率。ADC 的转换时间可以由以下公式计算:

Tcovn=采样时间+12 个周期

其中:Tcovn 为总转换时间,采样时间是根据每个通道的 SMP 位的设置来决定的。例如, 当 ADCCLK=21Mhz 的时候,并设置 3 个周期的采样时间,则得到:Tcovn=3+12=15 个周期 =0.71us。

ADC 规则序列寄存器(ADC_SQR1~3)

该寄存器总共有 3 个,这几个 寄存器的功能都差不多。

ADC_SQR1

L[3:0]用于存储规则序列的长度,我们这里只用了 1 个,所以设置这几个位的值为 0。其他的 SQ13~16 则存储了规则序列中第 13~16 个通道的编号(0~18)。另外两个规则序列寄存器 同 ADC_SQR1 大同小异,我们选择的是单次转换, 所以只有一个通道在规则序列里面,这个序列就是 SQ1,至于 SQ1 里面哪个通道,完全由我们自己设置,通过 ADC_SQR3 的最低 5 位(也就是 SQ1)设置。

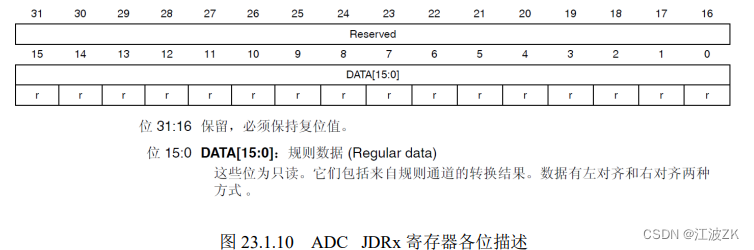

ADC 规则数据寄存器(ADC_DR)

规则序列中的 AD 转化结果都将被存 在这个寄存器里面,而注入通道的转换结果被保存在 ADC_JDRx 里面。

该寄存器的数据可以通过 ADC_CR2 的 ALIGN 位设置左对齐还是 右对齐。在读取数据的时候要注意。

ADC 寄存器为 ADC 状态寄存器(ADC_SR)

EOC 位,通过判断该位来决定是否此次规则通道的 AD 转换已经完成,如果该位位 1,则表示转换完成了,就可以从 ADC_DR 中读取转换结果,否则等待转换完成。

4829

4829

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?