1.四个代码

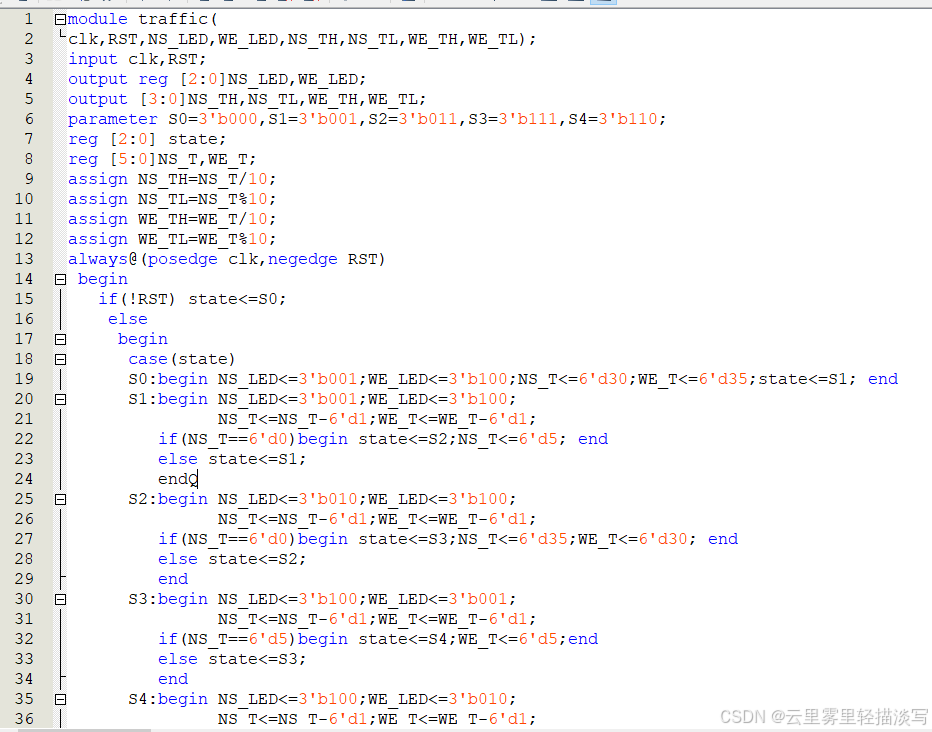

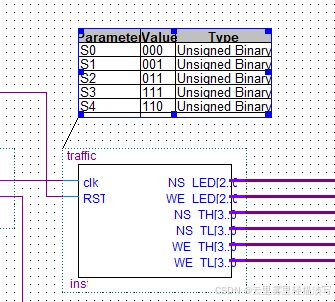

Traffic:module traffic(

clk,RST,NS_LED,WE_LED,NS_TH,NS_TL,WE_TH,WE_TL);

input clk,RST;

output reg [2:0]NS_LED,WE_LED;

output [3:0]NS_TH,NS_TL,WE_TH,WE_TL;

parameter S0=3'b000,S1=3'b001,S2=3'b011,S3=3'b111,S4=3'b110;

reg [2:0] state;

reg [5:0]NS_T,WE_T;

assign NS_TH=NS_T/10;

assign NS_TL=NS_T%10;

assign WE_TH=WE_T/10;

assign WE_TL=WE_T%10;

always@(posedge clk,negedge RST)

begin

if(!RST) state<=S0;

else

begin

case(state)

S0:begin NS_LED<=3'b001;WE_LED<=3'b100;NS_T<=6'd30;WE_T<=6'd35;state<=S1; end

S1:begin NS_LED<=3'b001;WE_LED<=3'b100;

NS_T<=NS_T-6'd1;WE_T<=WE_T-6'd1;

if(NS_T==6'd0)begin state<=S2;NS_T<=6'd5; end

else state<=S1;

end

S2:begin NS_LED<=3'b010;WE_LED<=3'b100;

NS_T<=NS_T-6'd1;WE_T<=WE_T-6'd1;

if(NS_T==6'd0)begin state<=S3;NS_T<=6'd35;WE_T<=6'd30; end

else state<=S2;

end

S3:begin NS_LED<=3'b100;WE_LED<=3'b001;

NS_T<=NS_T-6'd1;WE_T<=WE_T-6'd1;

if(NS_T==6'd5)begin state<=S4;WE_T<=6'd5;end

else state<=S3;

end

S4:begin NS_LED<=3'b100;WE_LED<=3'b010;

NS_T<=NS_T-6'd1;WE_T<=WE_T-6'd1;

if(NS_T==6'd0)begin state<=S0;end

else state<=S4;

end

default:state<=S0;

endcase

end

end

endmodule

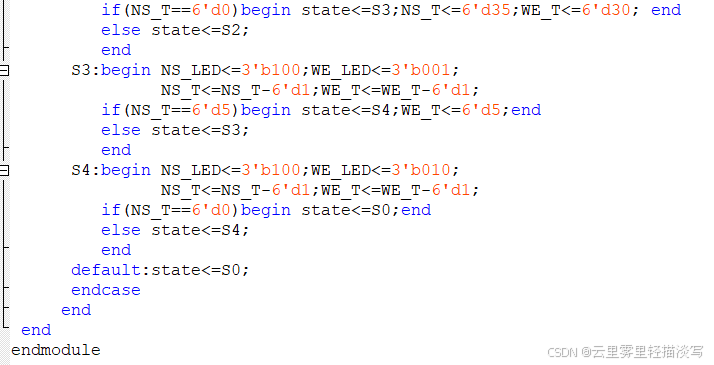

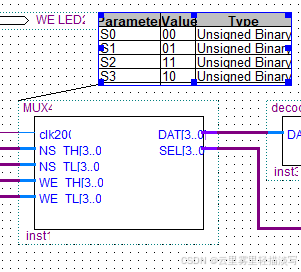

Mux4:module MUX4(clk200,NS_TH,NS_TL,WE_TH,WE_TL,DAT,SEL);

input clk200;

input [3:0]NS_TH,NS_TL,WE_TH,WE_TL;

output reg [3:0] DAT,SEL;

parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10;

reg [1:0]state=S0;

always@(posedge clk200)

begin

case(state)

S0:begin SEL<=4'b1000;DAT<=NS_TH; state<=S1;end

S1:begin SEL<=4'b0100;DAT<=NS_TL; state<=S2;end

S2:begin SEL<=4'b0010;DAT<=WE_TH; state<=S3;end

S3:begin SEL<=4'b0001;DAT<=WE_TL; state<=S0;end

default:begin state<=S0;end

endcase

end

endmodule

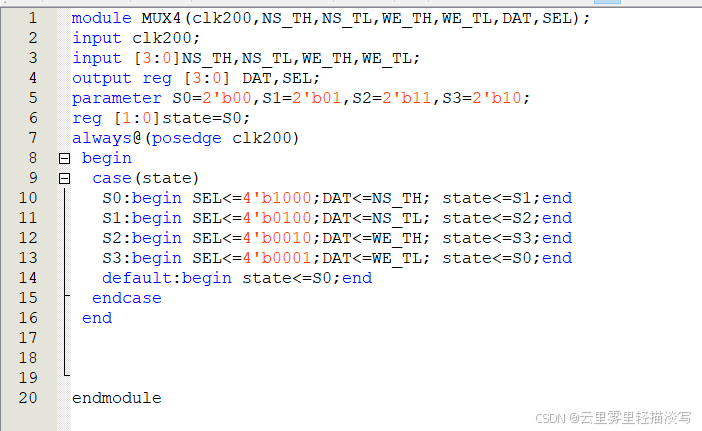

f_div:module f_div(clk50M,clk1,clk200);

input clk50M;

output reg clk1;

output clk200;

reg [25:0]q;

always@(posedge clk50M)

begin

if(q==26'd24999999)

begin q=25'd0;clk1=~clk1;end

else

q=q+26'd1;

end

assign clk200=q[17];

endmodule

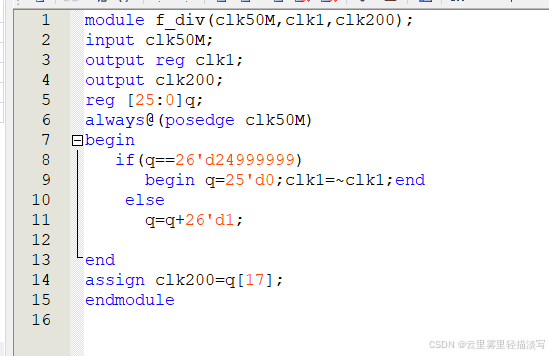

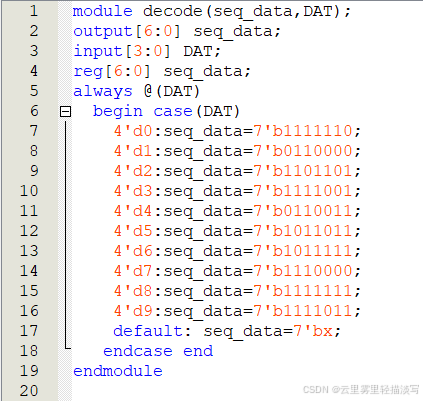

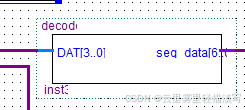

Decode:

module decode(seq_data,DAT);

output[6:0] seq_data;

input[3:0] DAT;

reg[6:0] seq_data;

always @(DAT)

begin case(DAT)

4'd0:seq_data=7'b1111110;

4'd1:seq_data=7'b0110000;

4'd2:seq_data=7'b1101101;

4'd3:seq_data=7'b1111001;

4'd4:seq_data=7'b0110011;

4'd5:seq_data=7'b1011011;

4'd6:seq_data=7'b1011111;

4'd7:seq_data=7'b1110000;

4'd8:seq_data=7'b1111111;

4'd9:seq_data=7'b1111011;

default: seq_data=7'bx;

endcase end

endmodule分别为

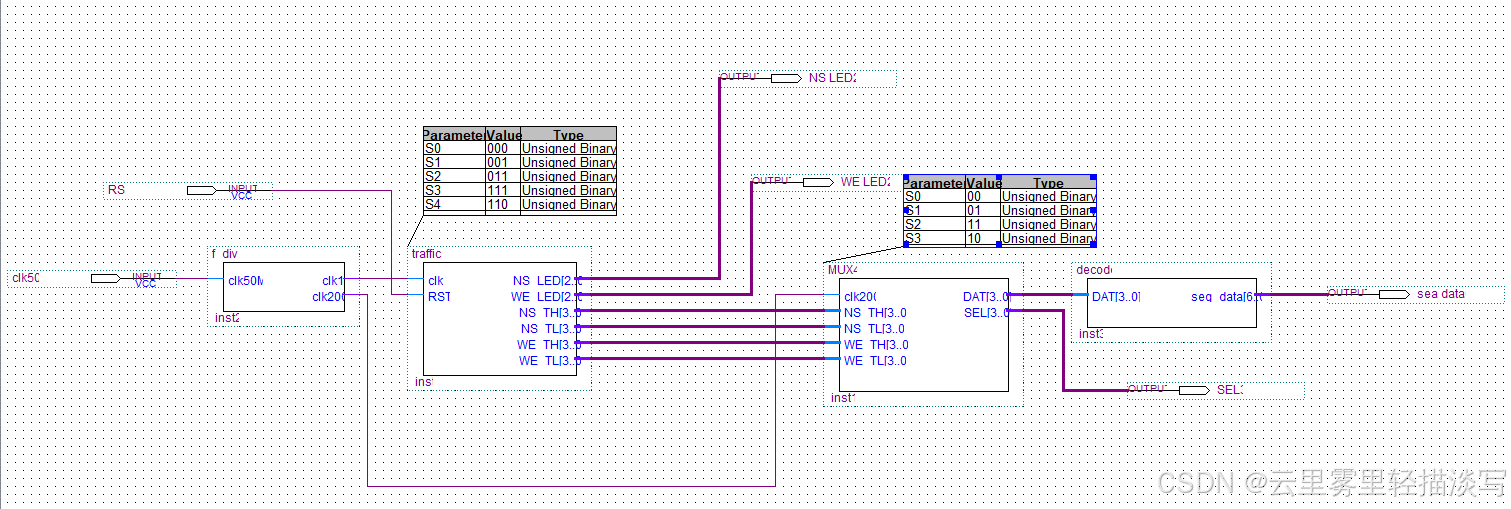

这4分别为个器件

连接完成

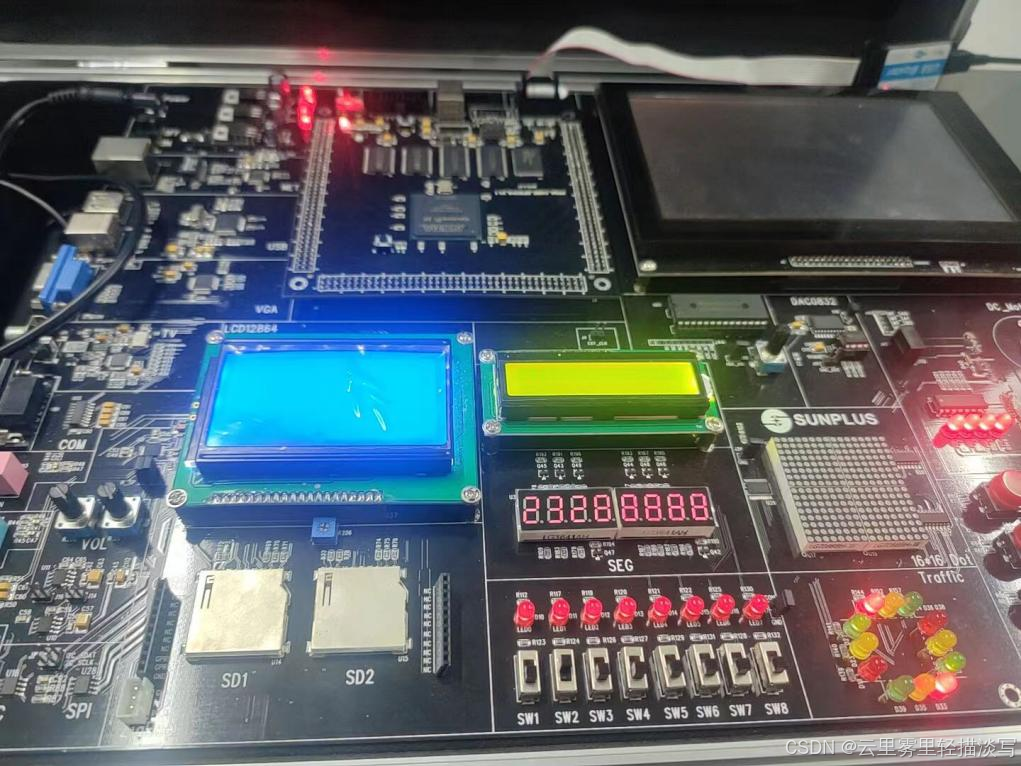

运行完成

心得体会

这次实验我学到到很多再次使用Quaryus软件,加深了巩固,通过实现4个代码实现了连接并接上之后使芯片得以启动,期间失败了多次,通过询问同学完成了这次实验的最终目的,对FPGA的学习有了更深的理解,产生了更加浓厚的兴趣。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?