实验目的:

1. 初步了解GPIO接口与设备

2. 了解计算机系统的基本结构

3. 了解计算机各组成部分的关系

4. 了解并掌握IP核的使用方法

5. 了解SOC系统并用IP核实现简单的SOC系统

实验环境:

1. 计算机(Intel Core i5以上,4GB内存以上)系统

2. NEXYS A7开发板

3. Xilinx VIVADO2017.4

及以上开发工具

实验目标及任务:

CPU测试环境(基本SOC系统)的建立

◼

目标

:熟悉

CPU

、外设接口和基本功能模块、存储器以及总线各个IP

子模块的功能,了解各个

IP

之间的联系和

SOC

系统的基本概念

◼

任务

:通过第三方

IP

和已有

IP

模块建立

CPU

测试环境(

SOC 系统的集成实现)------

参考原理图采用

Verilog

调用子模块的 方式实现,完成由按键消抖、时钟分频、8

通道选择、数码 管驱动、LED

驱动、

VGA

液晶驱动以及存储

ROM

、

RAM

等模块构建的实验平台

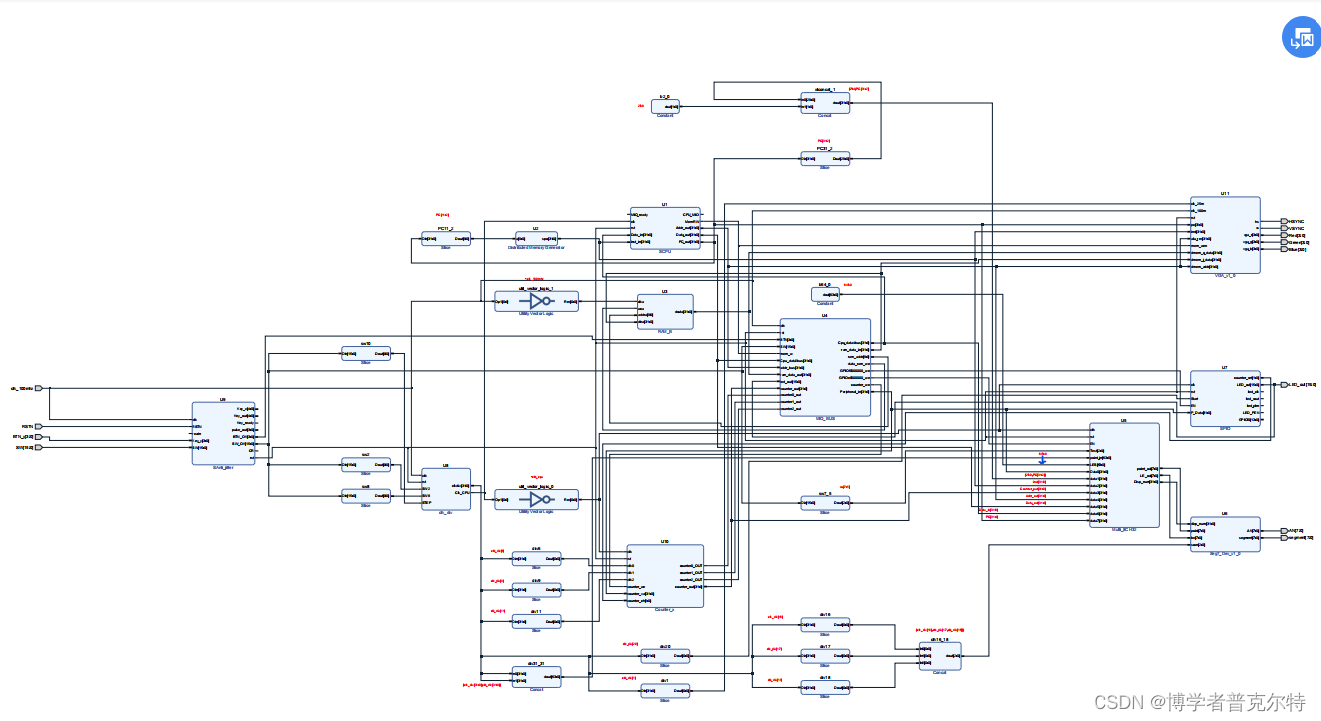

目标结构:

元件实现:

元件实现在IP.zip文件中给出。

顶层文件实现:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/03/27 22:36:46

// Design Name:

// Module Name: CSSTE

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module CSSTE(

input clk_100mhz,

input RSTN,

input [3:0] BTN_y,

input [15:0] SW,

output [3:0] Blue,

output [3:0] Green,

output [3:0] Red,

output HSYNC,

output VSYNC,

output [7:0] AN,

output [7:0] segment,

output [15:0] LED_out

);

wire [31:0]Addr_out;

wire [31:0]Data_in;

wire [31:0]Data_out;

wire MemRW;

wire [31:0]PC_out;

wire Clk_CPU;

wire [31:0]Inst_in;

wire rst;

wire [9:0]ram_addr;

wire [31:0]ram_data_in;

wire [31:0]RAM_B_0_douta;

wire U4_data_ram_we;

wire [3:0]BTN;

wire [15:0]SW_OK;

wire [31:0]counter_out;

wire counter0_out;

wire counter1_out;

wire counter2_out;

wire GPIOf0000000_we;

wire GPIOe0000000_we;

wire counter_we;

wire [31:0]Peripheral_in;

wire [31:0]clk_div;

wire [7:0]point_out;

wire [7:0]LE_out;

wire [31:0]Disp_num;

wire [1:0]counter_set;

SCPU U1

(.Addr_out(Addr_out),

.Data_in(Data_in),

.Data_out(Data_out),

.MemRW(MemRW),

.MIO_ready(1'b0),

.PC_out(PC_out),

.clk(Clk_CPU),

.inst_in(Inst_in),

.rst(rst));

ROM_D U2

(.a(PC_out[11:2]),

.spo(Inst_in));

RAM_B U3

(.addra(ram_addr),

.clka(~clk_100mhz),

.dina(ram_data_in),

.douta(RAM_B_0_douta),

.wea(U4_data_ram_we));

MIO_BUS U4

(.clk(clk_100mhz),

.rst(rst),

.BTN(BTN),

.SW(SW_OK),

.mem_w(MemRW),

.Cpu_data2bus(Data_out),

.addr_bus(Addr_out),

.ram_data_out(RAM_B_0_douta),

.led_out(LED_out),

.counter_out(counter_out),

.counter0_out(counter0_out),

.counter1_out(counter1_out),

.counter2_out(counter2_out),

.Cpu_data4bus(Data_in),

.ram_data_in(ram_data_in),

.ram_addr(ram_addr),

.data_ram_we(U4_data_ram_we),

.GPIOf0000000_we(GPIOf0000000_we),

.GPIOe0000000_we(GPIOe0000000_we),

.counter_we(counter_we),

.Peripheral_in(Peripheral_in));

Multi_8CH32 U5

(.clk(~Clk_CPU),

.rst(rst),

.EN(GPIOe0000000_we),

.Test(SW_OK[7:5]),

.point_in({clk_div[31:0],clk_div[31:0]}),

.LES(64'b0),

.Data0(Peripheral_in),

.data1({2'b0,PC_out[31:2]}),

.data2(Inst_in),

.data3(counter_out),

.data4(Addr_out),

.data5(Data_out),

.data6(Data_in),

.data7(PC_out),

.point_out(point_out),

.LE_out(LE_out),

.Disp_num(Disp_num));

Seg7_Dev_0 U6

(.disp_num(Disp_num[31:0]) ,

.point(point_out[7:0]),

.les(LE_out[7:0]),

.scan({clk_div[18:16]}),

.AN(AN[7:0]),

.segment(segment[7:0])

);

SPIO U7

(.clk(~Clk_CPU),

.rst(rst),

.Start(clk_div[20]),

.EN(GPIOf0000000_we),

.P_Data(Peripheral_in),

.counter_set(counter_set),

.LED_out(LED_out),

.led_clk(led_clk),

.led_sout(led_sout),

.led_clrn(led_clrn),

.LED_PEN(LED_PEN)

);

clk_div U8

(.clk(clk_100mhz),

.rst(rst),

.SW2(SW_OK[2]),

.SW8(SW_OK[8]),

.STEP(SW_OK[10]|BTN[0]),

.clkdiv(clk_div),

.Clk_CPU(Clk_CPU)

);

SAnti_jitter U9

(.clk(clk_100mhz),

.RSTN(RSTN),

.readn(1'b0),

.Key_y(BTN_y),

.SW(SW),

.BTN_OK(BTN),

.SW_OK(SW_OK),

.rst(rst)

);

Counter_x U10

(.clk(~Clk_CPU),

.rst(rst),

.clk0(clk_div[6]),

.clk1(clk_div[9]),

.clk2(clk_div[11]),

.counter_we(counter_we),

.counter_val(Peripheral_in),

.counter_ch(counter_set),

.counter0_OUT(counter0_out),

.counter1_OUT(counter1_out),

.counter2_OUT(counter2_out),

.counter_out(counter_out)

);

VGA U11

(.clk_25m(clk_div[1]),

.clk_100m(clk_100mhz),

.rst(rst),

.pc(PC_out),

.inst(Inst_in),

.alu_res(Addr_out),

.mem_wen(MemRW),

.dmem_o_data(RAM_B_0_douta),

.dmem_i_data(ram_data_in),

.dmem_addr(Addr_out),

.hs(HSYNC),

.vs(VSYNC),

.vga_r(Red),

.vga_g(Green),

.vga_b(Blue)

);

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?