3.3 算术运算部件

需解决的关键问题:

如何以加法器为基础,实现各种类型的算术逻辑运算处理。

解决思路:

复杂运算 -> 四则运算 -> 加法运算

解决方法:

在加法器的基础上,增加移位传送功能,并且输入运算控制条件。

3.3.1加法单元

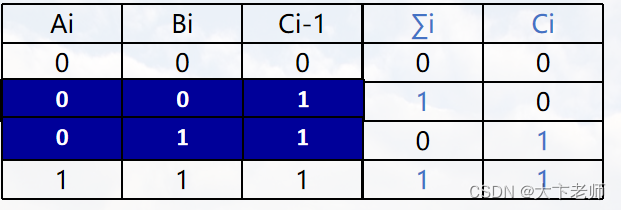

一个基本的加法单元示例

满足有:

∑i=(Ai+Bi+Ci-1) mod 2

Ci=(Ai+Bi+Ci-1) int

即满足真值表如下

扩展得:

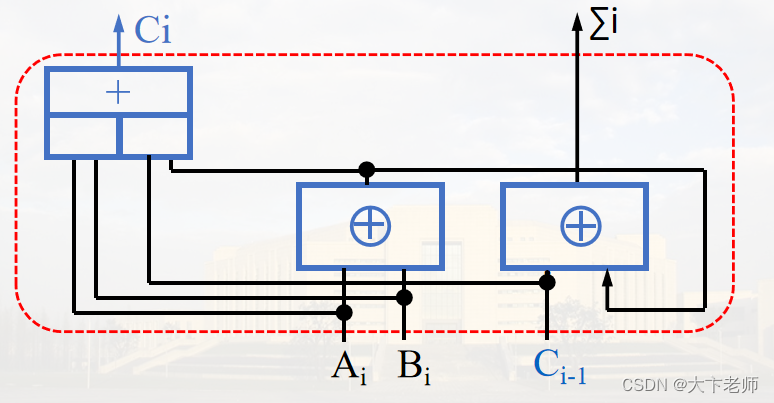

3.3.2全加器

∑i = ( Ai⊕Bi )⊕Ci-1

Ci = AiBi+(Ai⊕Bi)Ci-1

全加器的功能是求和,现在广泛的求和逻辑形态是:用异或逻辑实现半加,用两次半加实现一次全加。

进位的基本逻辑:

Ci = AiBi+(Ai⊕Bi)Ci-1 (令 AiBi = Gi,Ai⊕Bi = Pi )

所以 Ci = Gi + Pi Ci-1 (Gi : 本地进位、绝对进位;Pi:条件进位、传递进位)

由此可以得出两个结论

1.本位的两个输入A1和B1,中有且仅有一个为1时,若低位有进位传来(即 C(i-1)=1) ,则此时Ci=0+1=1,故本位必将产生进位。

2.本位的两个输入A和B1均为1,无论低位是否有进位传来(Ci-1=0或 Ci-1=1) ,此时都会有Ci=1+0=1,故本位也必将产生进位。

3.3.3进位链逻辑

全加器加法单元只能对1位数据求和,如果将2个多位操作数相加,就需要用加法单元构成法器来实现。加法器分为串行加法器和并行加法器两种,串行加法器因速度太慢,已被淘汰。现计算机中,运算器几乎都采用并行加法器,虽然操作数的各位是同时提供给并行加法器的,但存在进位信号的传递问题,(低位运算所产生的进位将会影响高位运算的结果)

1.串行加法器

(1)特点:低位向高位依次传递进位信号。 [例]先看一个8位数串行相加的例子

(2)影响运算速度的主要因素 : 进位信号的传递

(3)进位逻辑 特点:1.进位信号逐位形成 2. 设n位加法器

1)逻辑式

C1 = G1 + P1C0

C2 = G2 + P2C1

.......

Cn = Gn + PnCn-1

2.并行加法器

[特点]各位进位信号同时形成

n位加法器,进位逻辑如下:

1)逻辑关系

C1 = G1 + P1C0

C2 = G2 + P2C1 (代换C1)

= G2 + P2G1 + P2P1C0

..............

Cn = Gn + PnCn-1 (代换Cn-1)

= Gn + PnGn-1 + …+ PnPn-1…P2P1C0

纯并行进位结构在实现时有一个困难,即随输入数据位数的增加,高位的进位形成逻辑中输入的变量将随之增多,电路结构也会越来越复杂,这将受到实用器件扇入系数的限制。因此在数据位数较多的加法器中常采用分级、分组的进位链结构模式。

3、分组:组内并行、组间并行(或者串行)

设16位加法器,4位一组,分为4组

分级(2级)同时进位:组内并行、组间也并行。

速度/结构:介于全串行和全并行之间。

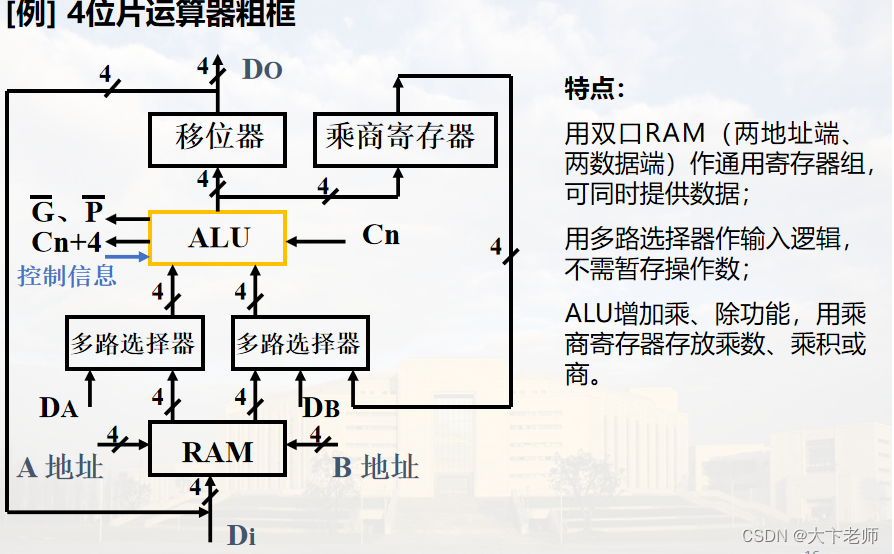

3.3.4运算器组织

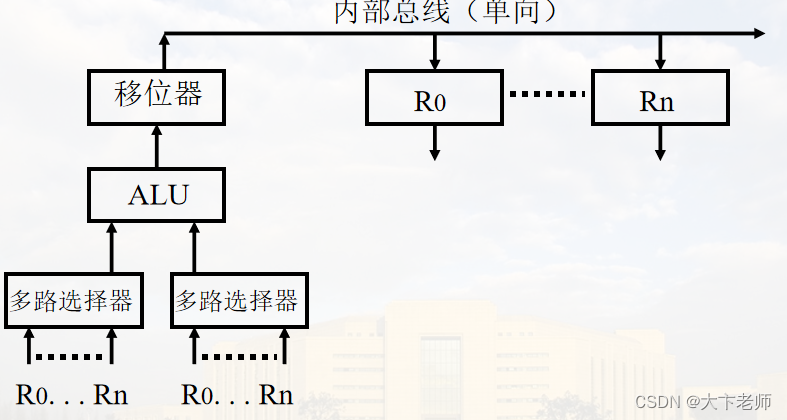

1、带多路选择器的运算器

特点: R各自独立;

可同时向ALU提供两个操作数;

采用单向内总线。

2、带输入锁存器的运算器

特点: 单口RAM不能同时向ALU提供两个操作数;

用锁存器暂存操作数;

采用双向内总线。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?