引言

指令格式设计是计算机系统结构设计的核心环节,它直接决定了指令集的编码效率、硬件实现复杂度以及系统整体性能。指令格式的编码方式需要在代码密度、译码效率、流水线友好性之间实现精妙平衡。本讲结合x86、ARM、RISC-V等典型架构案例,深入解析指令集的三种基本编码方式(可变长度、固定长度、混合编码)的设计哲学与技术实现。

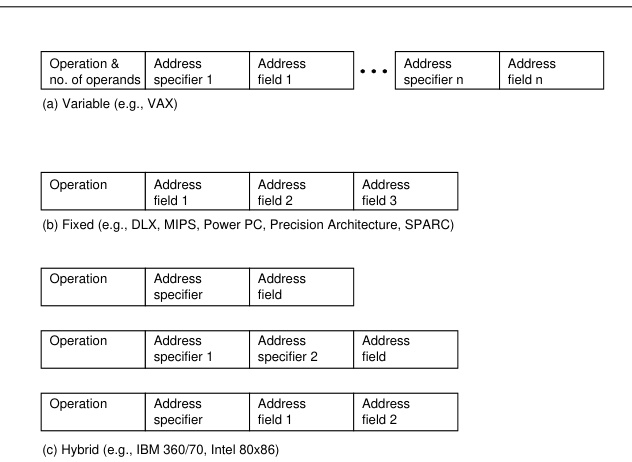

一、可变长度编码(Variable-Length Encoding)

1. 定义与特征

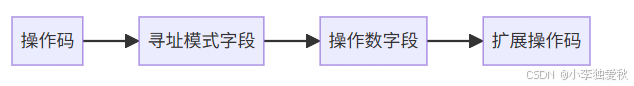

- 核心思想:允许不同指令具有不同长度,支持灵活的操作码与操作数组合

- 编码特点:

- 操作码长度可变(如1-4字节)

- 操作数字段可动态扩展(如8位/16位立即数)

- 支持任意寻址模式与操作类型的组合

2. 典型架构案例

(1)VAX架构

- 指令长度:2-53字节

- 优势:支持复杂指令如

POLY(多项式计算)和QUEUE(队列管理) - 劣势:译码电路复杂度高,流水线效率低(CPI高达4-6)

(2)x86架构(早期设计)

- 指令长度:1-15字节(如

MOV EAX, [EBX+ESI*4+0x100]占用7字节) - 现代优化:通过微操作转换器(Micro-ops)将复杂指令拆解为固定长度微指令流

3. 优缺点对比表

| 优势 | 劣势 |

|---|---|

| 代码密度高(哈夫曼编码优化) | 硬件译码复杂度高 |

| 支持任意寻址模式组合 | 流水线气泡风险大 |

| 适合CISC复杂指令扩展 | 指令预取效率低 |

理论依据:

代码密度∝1平均指令长度代码密度∝平均指令长度1

根据的哈夫曼编码模型,可变编码可比固定编码减少30%代码量。

二、固定长度编码(Fixed-Length Encoding)

1. 设计原则

- 核心特征:所有指令长度统一(如32位或16位)

- 结构规范:

- 操作码字段固定(如RISC-V的7位主操作码)

- 操作数字段对齐(如寄存器编号统一占5位)

- 立即数分段存储(如RISC-V的12位立即数分高位/低位)

2. 典型架构案例

(1)MIPS架构

| 6位操作码 | 5位rs | 5位rt | 5位rd | 5位shamt | 6位funct |

- R-Type指令:统一32位格式,支持寄存器-寄存器操作

- 优势:译码单元硬件实现简单(单周期完成指令解析)

(2)RISC-V基础指令集

- 标准指令长度:32位(RV32I)

- 扩展指令:RV64(64位)、RV128(128位)保持对齐原则

- 性能数据:5级流水线CPI可低至1.2

3. 优缺点对比表

| 优势 | 劣势 |

|---|---|

| 流水线效率高(无气泡风险) | 代码密度低(NOP填充常见) |

| 硬件实现简单 | 立即数范围受限 |

| 超标量发射友好 | 复杂操作需多条指令完成 |

设计权衡:固定长度编码牺牲代码密度换取执行效率,适合RISC架构的流水线优化。

三、混合编码(Hybrid Encoding)

1. 融合设计策略

- 核心思想:在操作码中指定多种指令格式,兼顾灵活性与效率

- 实现方式:

- 主操作码划分格式类型(如ARM的Thumb/ARM模式)

- 扩展操作码定义子格式(如x86的ModR/M字段)

- 压缩指令扩展(如RISC-V的C扩展指令)

2. 典型架构案例

(1)x86-64架构

| Prefix | Opcode | ModR/M | SIB | Displacement | Immediate |

- 多模式支持:

- 短格式:1-3字节(如

ADD EAX, 1) - 长格式:包含REX/VEX前缀(如AVX-512指令)

- 短格式:1-3字节(如

- 性能优化:微操作缓存(uOP Cache)将变长指令转为定长微操作流

(2)ARM Thumb-2指令集

- 混合位宽:16位与32位指令共存

- 16位指令:高密度基础操作(如

ADD R0, R1) - 32位指令:支持复杂操作(如

MLA R0, R1, R2, R3)

- 16位指令:高密度基础操作(如

- 代码密度:比纯32位模式节省25%存储空间

3. 优缺点对比表

| 优势 | 劣势 |

|---|---|

| 平衡代码密度与执行效率 | 译码逻辑复杂度中等 |

| 支持渐进式架构演进 | 需要软硬件协同优化 |

| 适应异构计算需求 | 跨模式切换可能引入延迟 |

创新实践:RISC-V通过可选扩展(M/C/F/D)实现混合编码,基础指令32位,C扩展支持16位压缩。

四、三种编码方式的对比与演进趋势

1. 综合对比分析表

| 维度 | 可变长度 | 固定长度 | 混合编码 |

|---|---|---|---|

| 代码密度 | ★★★★★ | ★★☆ | ★★★★ |

| 译码效率 | ★☆ | ★★★★★ | ★★★☆ |

| 流水线友好 | ★★ | ★★★★★ | ★★★★ |

| 硬件复杂度 | ★★★★★(高) | ★★(低) | ★★★(中) |

| 典型应用 | 传统CISC(x86) | 经典RISC(MIPS) | 现代ISA(ARMv9) |

2. 现代设计趋势

(1)分层译码体系

- 前端译码:快速识别指令格式(如x86的分支预测与预译码)

- 后端微操作:将复杂指令转为固定长度微指令(如Intel的uOP Cache)

(2)域特定扩展

- AI加速指令:NVIDIA的Tensor Core采用混合位宽(16/32/64位混合)

- 安全隔离指令:ARMv9的Realm模式引入专用指令格式

(3)动态编码优化

- 运行时压缩:IBM CodePack技术实现指令流动态压缩

- 自适应位宽:RISC-V的Zca扩展支持按需启用压缩指令

结语:编码方式的设计哲学

指令格式的三种编码方式体现了计算机系统结构中效率与灵活性的永恒博弈。三大设计定律:

- 局部性定律:90%的时间运行10%的指令,需优先优化高频指令格式

- 兼容性定律:新旧编码方式需保持后向兼容(如x86的实模式保护模式共存)

- 能效定律:每新增一种编码格式需评估功耗收益比

未来发展趋势呈现三个方向:

- 量子化编码:量子指令集可能引入叠加态编码模式

- 生物启发编码:借鉴DNA存储的纠错编码机制

- 神经形态编码:脉冲神经网络的事件驱动编码

理解指令格式设计的底层逻辑,是掌握计算机体系结构演进规律的关键。正如RISC-V的模块化设计所揭示的——优秀的编码方案不是取舍,而是创造性的融合。

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?