依然是fgpa开发,verilog语言,xc7a200tfbg676-2芯片,龙芯平台测试

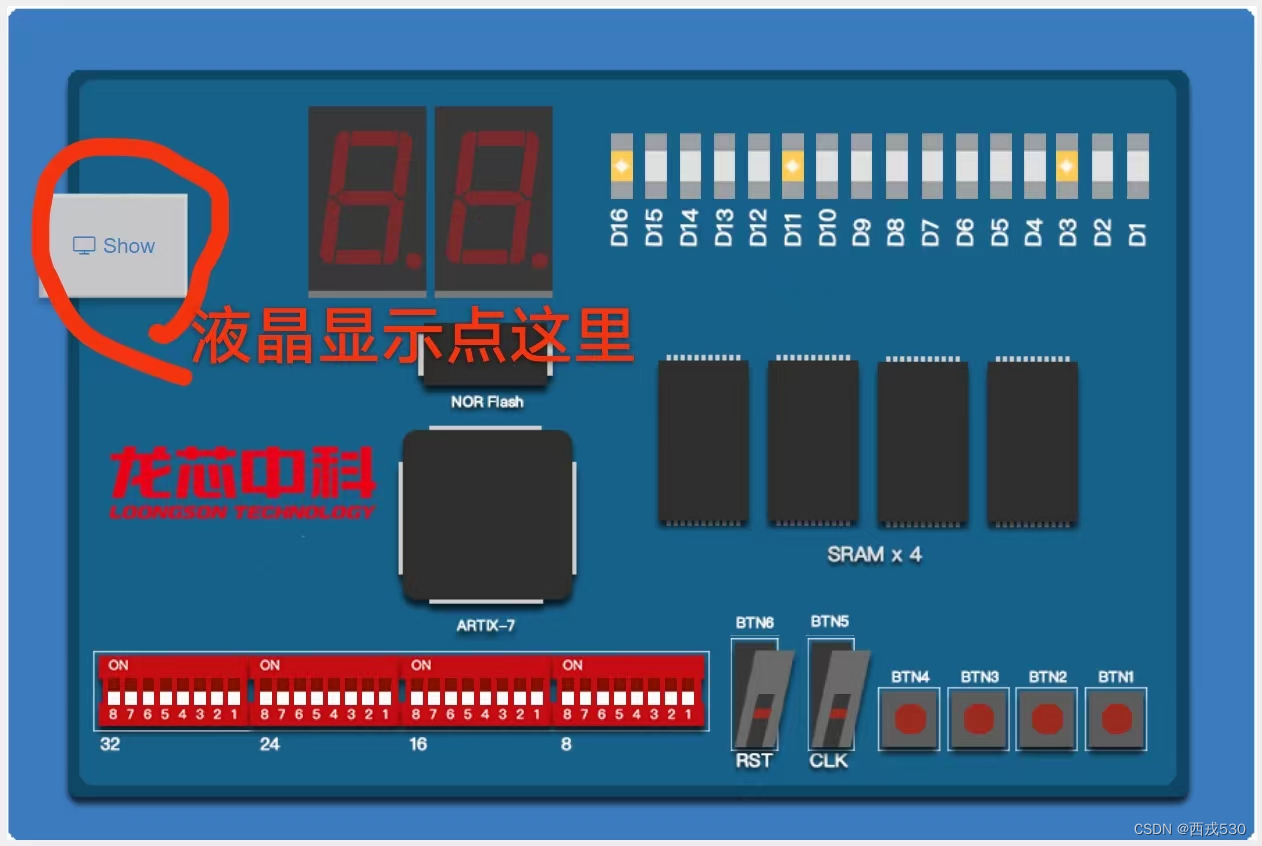

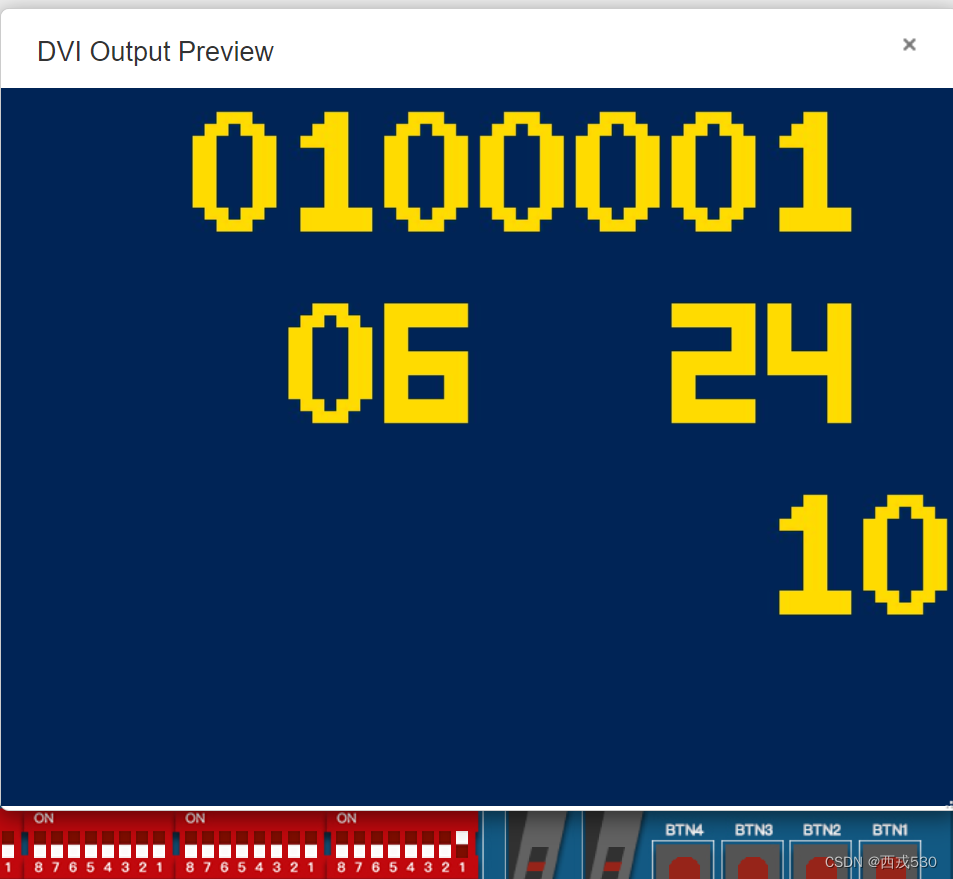

这次项目用平台的液晶显示

基础题:

十字路口由一条主道和支道构成。主道和支道均有红、绿、黄3种信号灯。

通常保持主道绿灯、支道红灯。只有当支道有车时,且主道计时的时间到,才转为主道红灯,支道绿灯。

绿灯转红灯过程中,先由绿灯转为黄灯,3秒钟后再由黄灯转为红灯;同时对方红灯转绿灯。

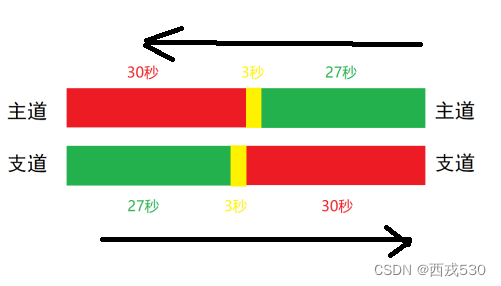

当两个方向同时有车时,红、绿灯应每隔30秒变换一次,应扣除绿灯转红灯过程中有3秒黄灯过渡,绿灯实际只亮27秒;如图1所示。

若仅一个方向有车时,处理方法是:该方向原来为红灯时,另一个方向立即由绿灯变为黄灯,3秒钟后再由黄灯变为红灯,同时本方向由红灯变为绿灯。该方向原为绿灯时,继续保持绿灯。当另一方向有车来时,作两个方向均有车处理。

图1 主道与支道信号灯与时间关系

这个题教材第八章第二节有,可以直接照书抄,我这个是带液晶显示的

DEDE.v

`timescale 1ns / 1ps

module DEDE(

input wire CP, // 时钟信号

input wire RESETn, // 复位信号

input wire AS, // 主道车辆传感器信号,AS=AS1+AS2

input wire BS, // 支道车辆传感器信号,BS=BS1+BS2

//input wire clk_50M,

/*input wire [3:0] countA_shi,

input wire [3:0] countA_ge,

input wire [3:0] countB_shi,

input wire [3:0] countB_ge,

input wire [3:0] countC_shi,

input wire [3:0] countC_ge,

input wire [3:0] countD_shi,

input wire [3:0] countD_ge,

input wire [3:0] countE_shi,

input wire [3:0] countE_ge,

input wire [3:0] countF_shi,

input wire [3:0] countF_ge,

output wire video_hsync,

output wire video_vsync,

output wire video_clk,

output wire video_de,

output wire [2:0] video_red, //红色像素_3使

output wire [2:0] video_green, //绿色像素_3使

output wire [1:0] video_blue, //蓝色像素_2使*/

output wire T27, // 27秒计时到达信号

output wire T3, // 3秒计时到达信号

output wire AK, // 主道由绿转黄信号

output wire BK, // 支道由绿转黄信号

output wire C3, // 3秒计时器控制信号

output wire C27, // 27秒计时器控制信号

output wire AG, // 主道绿灯信号

output wire AY, // 主道黄灯信号

output wire AR, // 主道红灯信号

output wire BG, // 支道绿灯信号

output wire BY, // 支道黄灯信号

output wire BR, // 支道红灯信号

output wire [7:0] QT27, // 27秒计时器输出

output wire [3:0] QT3, // 3秒计时器输出

output wire [1:0] QS,

output wire[3:0] ten,

output wire[3:0] one // 控制信号输出

);

/*wire W1, W2, W3;

wire [3:0] D0, D1;

wire [1:0] QS_lcd;

assign D0 = 4'b0000;

assign W2 = 1;*/

// 实例化 count3 模块

count3 U1(

.CP(CP),

.C3(C3),

.RESETn(RESETn),

.Q(QT3),

.T3(T3)

);

// 实例化 count27 模块

count27 U2(

.CP(CP),

.C27(C27),

.RESETn(RESETn & ~C3),

.Q(QT27),

.T27(T27)

);

// 实例化 control 模块

control U3(

.CP(CP),

.RESETn(RESETn),

.AS(AS),

.BS(BS),

.T3(T3),

.T27(T27),

.C3(C3),

.C27(C27),

.AK(AK),

.BK(BK),

.Q1(QS[1]),

.Q0(QS[0]),

.AG(AG),

.AY(AY),

.AR(AR),

.BG(BG),

.BY(BY),

.BR(BR)

);

// 实例化 clock_1hz 模块

/*clock_1hz u1(

.CLK(CP),

.RSTn(W2),

.T1hz(W1)

);*/

/*lcd_top u3(

.clk_50M(CP),

//.CP(CP),

.RESETn(RESETn),

.countA_shi(D1),

.countA_ge(D1),

.countB_shi(D1),

.countB_ge(D1),

.countC_shi(D1),

.countC_ge(D1),

.countD_shi(D1),

.countD_ge(D1),

.countE_shi(D1),

.countE_ge(D1),

.countF_shi(D1),

.countF_ge(D1),

.AG(AG),

.AY(AY),

.AR(AR),

.BG(BG),

.BY(BY),

.BR(BR),

.video_red(video_red),

.video_green(video_green),

.video_blue(video_blue),

.video_hsync(video_hsync),

.video_vsync(video_vsync),

.video_clk(video_clk),

.video_de(video_de)

);

ascii_rom_async u4(

.addr(addr),

.data(data)

);

bin2bcd u5(

.bin(bin),

.bcd(bcd)

);

clock_divider u6(

.clk(CP),

.rst(RESETn),

.clk_div(clk_div)

);

div_module u7(

.CP(CP),

.clk_locked(clk_locked),

.AG(AG),

.AY(AY),

.AR(AR),

.BG(BG),

.BY(BY),

.BR(BR),

.video_hsync(video_hsync),

.video_vsync(video_vsync),

.video_clk(video_clk),

.video_de(video_de),

.line_0_ascii(line_0_ascii),

.line_1_ascii(line_1_ascii)

);

assign QS_lcd = {QS[1], QS[0]};*/

assign ten=QT27[7:4];

assign one=QT27[3:0];

endmodule

module control(

input wire CP, // 时钟信号

input wire RESETn, // 复位信号

input wire AS, // 主道车辆传感器信号

input wire BS, // 支道车辆传感器信号

input wire T27, // 27秒定时到信号

input wire T3, // 3秒定时到信号

output wire AK, // 主道由绿转黄信号

output wire BK, // 支道由绿转黄信号

output wire C3, // 3秒计时器控制信号

output wire C27, // 27秒计时器控制信号

output wire Q1, // 控制信号输出1

output wire Q0, // 控制信号输出0

output wire AG, // 主道绿灯信号

output wire AY, // 主道黄灯信号

output wire AR, // 主道红灯信号

output wire BG, // 支道绿灯信号

output wire BY, // 支道黄灯信号

output wire BR // 支道红灯信号

);

wire D0, D1, Y0, Y1, Y2, Y3;

assign C3 = Q0; // C3 信号等于 Q0

assign C27 = ~Q0; // C27 信号等于 Q0的反

assign AG = ~Y0; // AG 信号等于 Y0

assign AY = ~Y1; // AY 信号等于 Y1

assign BG = ~Y2; // BG 信号等于 Y2

assign BY = ~Y3; // BY 信号等于 Y3

//assign BR = ~(Y3 & Y2); // BR 信号等于 Y3 和 Y2 的与非

//assign AR = ~(Y0 & Y1); // AR 信号等于 Y0 和 Y1 的与非

assign BR = Y3 & Y2; // BR 信号等于 Y3 和 Y2 的与非

assign AR = Y0 & Y1; // AR 信号等于 Y0 和 Y1 的与非

LS153 U0(

.S1(AS), // 输入信号

.S0(BS), // 输入信号

.G2(1'b0),

.G1(1'b0),

.D10(1'b0),

.D11(1'b1),

.D12(1'b0),

.D13(T27), // 输入信号

.D20(1'b1),

.D21(1'b0),

.D22(1'b1),

.D23(T27), // 输入信号

.Y1(AK), // 输出信号

.Y2(BK) // 输出信号

);

LS153 U1(

.S1(Q1), // 输入信号

.S0(Q0), // 输入信号

.G2(1'b0),

.G1(1'b0),

.D10(AK), // 输入信号

.D11(~T3), // 输入信号

.D12(BK), // 输入信号

.D13(~T3), // 输入信号

.D20(1'b0),

.D21(T3), // 输入信号

.D22(1'b1),

.D23(~T3), // 输入信号

.Y1(D0), // 输出信号

.Y2(D1) // 输出信号

);

LS139 U2(

.G1(1'b0),

.A1(Q0), // 输入信号

.B1(Q1), // 输入信号

.Y13(Y3), // 输出信号

.Y12(Y2), // 输出信号

.Y11(Y1), // 输出信号

.Y10(Y0) // 输出信号

);

ffd FF0(

.CLR(RESETn), // 复位信号

.SET(1'b1),

.CP(CP), // 时钟信号

.D(D0), // 输入数据

.Q(Q0) // 输出寄存器

);

ffd FF1(

.CLR(RESETn), // 复位信号

.SET(1'b1),

.CP(CP), // 时钟信号

.D(D1), // 输入数据

.Q(Q1) // 输出寄存器

);

endmodule

module count3(

input wire CP,

input wire C3,

input wire RESETn,

output wire [3:0] Q,

output wire T3

);

assign T3 = Q[1];

LS160 u0(

.CLK(CP),

.CLRn(RESETn),

.LDn(~T3),

.D(4'b0000),

.ENP(1'b1),

.ENT(C3),

.Q(Q)

);

endmodule

module count27(

input wire CP,

input wire C27,

input wire RESETn,

output wire [7:0] Q,

output wire T10,

output wire T27

);

assign T27 = Q[5] & ~Q[4] & ~Q[3] & Q[2] & Q[1] & ~Q[0];

LS160 u0(

.CLK(CP),

.CLRn(RESETn),

.LDn(~T27),

.D(4'b0000),

.ENP(1'b1),

.ENT(C27),

.RCO(T10),

.Q(Q[3:0])

);

LS160 u1(

.CLK(CP),

.CLRn(RESETn),

.LDn(~T27),

.D(4'b0000),

.ENP(T10),

.ENT(C27),

.Q(Q[7:4])

);

endmodule

module LS160(

input wire CLK,

input wire CLRn,

input wire LDn,

input wire [3:0] D,

input wire ENP,

input wire ENT,

output reg [3:0] Q,

output wire RCO

);

assign RCO = Q[3] & ~Q[2] & ~Q[1] & Q[0] & ENT;

//分频模块

reg [28:0] cnt;

reg clk1hz;

//50MHZ转1HZ

always @(posedge CLK)

begin

if(cnt !=28'd24999999)

cnt<=cnt+1;

else cnt<=28'd0;

end

always @(posedge CLK) begin

if(cnt==28'd0)

clk1hz<=~clk1hz;

end

always @(posedge clk1hz or negedge CLRn)

begin if(~CLRn) Q<=4'b0000;

else if(~LDn) Q<=D;

else begin

case({ENT,ENP})

2'b11:if(Q<4'b1001) Q<=Q+1;

else if(Q==4'b1001) Q<=4'b0000;

default Q<=Q;

endcase

end

end

endmodule

module LS153(

input wire S1,

input wire S0,

input wire G2,

input wire G1,

input wire D10,

input wire D11,

input wire D12,

input wire D13,

input wire D20,

input wire D21,

input wire D22,

input wire D23,

output wire Y1,

output wire Y2

);

assign Y1=( ~G1 & ~S1 &~S0 & D10)|( ~G1 & ~S1 &S0 & D11)|( ~G1 & S1 &~S0 & D12)|( ~G1 & S1 &S0 & D13);

assign Y2=( ~G2 & ~S1 &~S0 & D20)|( ~G2 & ~S1 &S0 & D21)|( ~G2 & S1 &~S0 & D22)|( ~G2 & S1 &S0 & D23);

endmodule

module LS139(

input wire G1,

input wire A1,

input wire B1,

input wire G2,

input wire A2,

input wire B2,

output wire Y13,

output wire Y12,

output wire Y11,

output wire Y10,

output wire Y23,

output wire Y22,

output wire Y21,

output wire Y20

);

assign Y10 = ~(~A1 & ~B1 & ~G1);

assign Y11 = ~(A1 & ~B1 & ~G1);

assign Y12 = ~(~A1 & B1 & ~G1);

assign Y13 = ~(A1 & B1 & ~G1);

assign Y20 = ~(~A2 & ~B2 & ~G2);

assign Y21 = ~(A2 & ~B2 & ~G2);

assign Y22 = ~(~A2 & B2 & ~G2);

assign Y23 = ~(A2 & B2 & ~G2);

endmodule

module ffd(

input wire CLR,

input wire SET,

input wire CP,

input wire D,

output reg Q

);

always @(posedge CP or negedge CLR) begin

if (CLR == 0)

Q <= 1'b0;

else if (SET == 0)

Q <= 1'b1;

else

Q <= D;

end

endmodule

module clock_1hz(

input wire CLK,

input wire RSTn,

output reg T1hz

);

parameter TIME_1Hz=25'd25000000;

reg [24:0] conut;

always @(posedge CLK or negedge RSTn) begin

if(!RSTn) conut<=25'd0;

else if(conut<TIME_1Hz)

conut<=conut+1;

else conut<=25'd0;

end

always @(posedge CLK or negedge RSTn) begin

if(!RSTn) T1hz<=25'd0;

else if(conut==25'd0)

T1hz<=T1hz;

end

endmodule

lcd_top.sv

`default_nettype none `timescale 1ns / 1ps

module lcd_top (

input wire clk_50M, //50MHz 鏃堕挓杈撳叆

input wire reset_btn, //BTN6鎵嬪姩澶嶄綅鎸夐挳寮?鍏筹紝甯︽秷鎶栫數璺紝鎸変笅鏃朵负1

input wire [3:0] countA_shi,

input wire [3:0] countA_ge,

input wire [3:0] countB_shi,

input wire [3:0] countB_ge,

input wire [3:0] countC_shi,

input wire [3:0] countC_ge,

input wire [3:0] countD_shi,

input wire [3:0] countD_ge,

input wire [3:0] countE_shi,

input wire [3:0] countE_ge,

input wire [3:0] countF_shi,

input wire [3:0] countF_ge,

output wire leds,

//鍥惧儚杈撳嚭淇″彿

output wire [2:0] video_red, //绾㈣壊鍍忕礌锛?3浣?

output wire [2:0] video_green, //缁胯壊鍍忕礌锛?3浣?

output wire [1:0] video_blue, //钃濊壊鍍忕礌锛?2浣?

output wire video_hsync, //琛屽悓姝ワ紙姘村钩鍚屾锛変俊鍙?

output wire video_vsync, //鍦哄悓姝ワ紙鍨傜洿鍚屾锛変俊鍙?

output wire video_clk, //鍍忕礌鏃堕挓杈撳嚭

output wire video_de //琛屾暟鎹湁鏁堜俊鍙凤紝鐢ㄤ簬鍖哄垎娑堥殣鍖?

);

// generate pixel clock

logic clk_pix;

logic clk_pix_locked;

clock_divider clock_div_inst (

.clk(clk_50M),

.rst(reset_btn),

.clk_div(clk_pix)

);

wire [15:0] line_2_ascii;

dvi_module dvi_inst (

.clk(clk_pix),

.clk_locked(reset_btn),

.video_red(video_red),

.video_green(video_green),

.video_blue(video_blue),

.video_hsync(video_hsync),

.video_vsync(video_vsync),

.video_clk(video_clk),

.video_de(video_de),

.line_0_ascii(line_0),

.line_1_ascii(line_1),

// .line_2_number( )

.line_2_number(number)

// .line_2_ascii_to_top(line_2_ascii)

);

assign leds =1'b0 ;

//line_2_ascii[15:0];

wire [79:0] line_0; // 涓轰簡鏂逛究璧嬪?硷紝涓?涓猘scii鍗犵敤8bit

wire [79:0] line_1; // 56-bit line buffer, 7 bit per ascii character

// wire [7:0] countA_shi;

// wire [7:0] countA_ge;

// wire [7:0] countB_shi;

// wire [7:0] countB_ge;

// wire [7:0] countC_shi;

// wire [7:0] countC_ge;

// wire [7:0] countD_shi;

// wire [7:0] countD_ge;

// assign countA_shi=ascii;

// assign countA_ge=ascii;

// assign countB_shi=ascii;

// assign countB_ge=ascii;

// assign countC_shi=ascii;

// assign countC_ge=ascii;

// assign countD_shi=ascii;

// assign countD_ge=ascii;

// assign line_0 = {{8{ascii}},countA_shi+30,countA_shi+30,countA_shi+30,countA_shi+30, line_2_ascii};

assign line_0 = {8'h20,countB_shi+8'h30,countA_shi+8'h30,countA_ge+8'h30,countC_shi+8'h30,countC_ge+8'h30,countD_shi+8'h30,countD_ge+8'h30,8'h20};

assign line_1 = {8'h20,countE_shi+8'h30,countE_ge+8'h30,8'h20,8'h20,countF_shi+8'h30,countF_ge+8'h30, 8'h20};

// assign line_1 = 80'h3a_39_38_37_36_35_34_33_32_31_30;

localparam CNT_1S = 27'd50_000_000;

reg [26:0] cnt;

wire cnt_eq_1s;

assign cnt_eq_1s = cnt==(CNT_1S-1);

always @(posedge clk_50M)

begin

if (reset_btn)

begin

cnt <= 27'd0;

end

else if (cnt_eq_1s)

begin

cnt <= 27'd0;

end

else

begin

cnt <= cnt + 1'b1;

end

end

reg [7:0] ascii;

always @(posedge clk_50M)

begin

if (reset_btn)

begin

ascii <= 8'd0;

end

else if (cnt_eq_1s)

begin

if (ascii == 8'd9)

begin

ascii <= 8'd0;

end

else

begin

ascii <= ascii + 1'b1;

end

end

end

reg [4:0] number;

always @(posedge clk_50M)

begin

if (reset_btn)

begin

number <= 5'h0;

end

else if (cnt_eq_1s)

begin

number <= number + 5'b1;

end

end

endmodule

module ascii_rom_async (

input wire [10:0] addr,

output reg [7:0] data

);

always @(*) begin

case (addr)

// code x30 (0)

11'h300: data = 8'b00000000; //

11'h301: data = 8'b00000000; //

11'h302: data = 8'b00111000; // ***

11'h303: data = 8'b01101100; // ** **

11'h304: data = 8'b11000110; //** **

11'h305: data = 8'b11000110; //** **

11'h306: data = 8'b11000110; //** **

11'h307: data = 8'b11000110; //** **

11'h308: data = 8'b11000110; //** **

11'h309: data = 8'b11000110; //** **

11'h30a: data = 8'b01101100; // ** **

11'h30b: data = 8'b00111000; // ***

11'h30c: data = 8'b00000000; //

11'h30d: data = 8'b00000000; //

11'h30e: data = 8'b00000000; //

11'h30f: data = 8'b00000000; //

// code x31 (1)

11'h310: data = 8'b00000000; //

11'h311: data = 8'b00000000; //

11'h312: data = 8'b00011000; // **

11'h313: data = 8'b00111000; // ***

11'h314: data = 8'b01111000; // ****

11'h315: data = 8'b00011000; // **

11'h316: data = 8'b00011000; // **

11'h317: data = 8'b00011000; // **

11'h318: data = 8'b00011000; // **

11'h319: data = 8'b00011000; // **

11'h31a: data = 8'b01111110; // ******

11'h31b: data = 8'b01111110; // ******

11'h31c: data = 8'b00000000; //

11'h31d: data = 8'b00000000; //

11'h31e: data = 8'b00000000; //

11'h31f: data = 8'b00000000; //

// code x32 (2)

11'h320: data = 8'b00000000; //

11'h321: data = 8'b00000000; //

11'h322: data = 8'b11111110; //*******

11'h323: data = 8'b11111110; //*******

11'h324: data = 8'b00000110; // **

11'h325: data = 8'b00000110; // **

11'h326: data = 8'b11111110; //*******

11'h327: data = 8'b11111110; //*******

11'h328: data = 8'b11000000; //**

11'h329: data = 8'b11000000; //**

11'h32a: data = 8'b11111110; //*******

11'h32b: data = 8'b11111110; //*******

11'h32c: data = 8'b00000000; //

11'h32d: data = 8'b00000000; //

11'h32e: data = 8'b00000000; //

11'h32f: data = 8'b00000000; //

// code x33 (3)

11'h330: data = 8'b00000000; //

11'h331: data = 8'b00000000; //

11'h332: data = 8'b11111110; //*******

11'h333: data = 8'b11111110; //*******

11'h334: data = 8'b00000110; // **

11'h335: data = 8'b00000110; // **

11'h336: data = 8'b00111110; // *****

11'h337: data = 8'b00111110; // *****

11'h338: data = 8'b00000110; // **

11'h339: data = 8'b00000110; // **

11'h33a: data = 8'b11111110; //*******

11'h33b: data = 8'b11111110; //*******

11'h33c: data = 8'b00000000; //

11'h33d: data = 8'b00000000; //

11'h33e: data = 8'b00000000; //

11'h33f: data = 8'b00000000; //

// code x34 (4)

11'h340: data = 8'b00000000; //

11'h341: data = 8'b00000000; //

11'h342: data = 8'b11000110; //** **

11'h343: data = 8'b11000110; //** **

11'h344: data = 8'b11000110; //** **

11'h345: data = 8'b11000110; //** **

11'h346: data = 8'b11111110; //*******

11'h347: data = 8'b11111110; //*******

11'h348: data = 8'b00000110; // **

11'h349: data = 8'b00000110; // **

11'h34a: data = 8'b00000110; // **

11'h34b: data = 8'b00000110; // **

11'h34c: data = 8'b00000000; //

11'h34d: data = 8'b00000000; //

11'h34e: data = 8'b00000000; //

11'h34f: data = 8'b00000000; //

// code x35 (5)

11'h350: data = 8'b00000000; //

11'h351: data = 8'b00000000; //

11'h352: data = 8'b11111110; //*******

11'h353: data = 8'b11111110; //*******

11'h354: data = 8'b11000000; //**

11'h355: data = 8'b11000000; //**

11'h356: data = 8'b11111110; //*******

11'h357: data = 8'b11111110; //*******

11'h358: data = 8'b00000110; // **

11'h359: data = 8'b00000110; // **

11'h35a: data = 8'b11111110; //*******

11'h35b: data = 8'b11111110; //*******

11'h35c: data = 8'b00000000; //

11'h35d: data = 8'b00000000; //

11'h35e: data = 8'b00000000; //

11'h35f: data = 8'b00000000; //

// code x36 (6)

11'h360: data = 8'b00000000; //

11'h361: data = 8'b00000000; //

11'h362: data = 8'b11111110; //*******

11'h363: data = 8'b11111110; //*******

11'h364: data = 8'b11000000; //**

11'h365: data = 8'b11000000; //**

11'h366: data = 8'b11111110; //*******

11'h367: data = 8'b11111110; //*******

11'h368: data = 8'b11000110; //** **

11'h369: data = 8'b11000110; //** **

11'h36a: data = 8'b11111110; //*******

11'h36b: data = 8'b11111110; //*******

11'h36c: data = 8'b00000000; //

11'h36d: data = 8'b00000000; //

11'h36e: data = 8'b00000000; //

11'h36f: data = 8'b00000000; //

// code x37 (7)

11'h370: data = 8'b00000000; //

11'h371: data = 8'b00000000; //

11'h372: data = 8'b11111110; //*******

11'h373: data = 8'b11111110; //*******

11'h374: data = 8'b00000110; // **

11'h375: data = 8'b00000110; // **

11'h376: data = 8'b00000110; // **

11'h377: data = 8'b00000110; // **

11'h378: data = 8'b00000110; // **

11'h379: data = 8'b00000110; // **

11'h37a: data = 8'b00000110; // **

11'h37b: data = 8'b00000110; // **

11'h37c: data = 8'b00000000; //

11'h37d: data = 8'b00000000; //

11'h37e: data = 8'b00000000; //

11'h37f: data = 8'b00000000; //

// code x38 (8)

11'h380: data = 8'b00000000; //

11'h381: data = 8'b00000000; //

11'h382: data = 8'b11111110; //*******

11'h383: data = 8'b11111110; //*******

11'h384: data = 8'b11000110; //** **

11'h385: data = 8'b11000110; //** **

11'h386: data = 8'b11111110; //*******

11'h387: data = 8'b11111110; //*******

11'h388: data = 8'b11000110; //** **

11'h389: data = 8'b11000110; //** **

11'h38a: data = 8'b11111110; //*******

11'h38b: data = 8'b11111110; //*******

11'h38c: data = 8'b00000000; //

11'h38d: data = 8'b00000000; //

11'h38e: data = 8'b00000000; //

11'h38f: data = 8'b00000000; //

// code x39 (9)

11'h390: data = 8'b00000000; //

11'h391: data = 8'b00000000; //

11'h392: data = 8'b11111110; //*******

11'h393: data = 8'b11111110; //*******

11'h394: data = 8'b11000110; //** **

11'h395: data = 8'b11000110; //** **

11'h396: data = 8'b11111110; //*******

11'h397: data = 8'b11111110; //*******

11'h398: data = 8'b00000110; // **

11'h399: data = 8'b00000110; // **

11'h39a: data = 8'b11111110; //*******

11'h39b: data = 8'b11111110; //*******

11'h39c: data = 8'b00000000; //

11'h39d: data = 8'b00000000; //

11'h39e: data = 8'b00000000; //

11'h39f: data = 8'b00000000; //

// code x3a (:)

11'h3a0: data = 8'b00000000; //

11'h3a1: data = 8'b00000000; //

11'h3a2: data = 8'b00000000; //

11'h3a3: data = 8'b00000000; //

11'h3a4: data = 8'b00011000; // **

11'h3a5: data = 8'b00011000; // **

11'h3a6: data = 8'b00000000; //

11'h3a7: data = 8'b00000000; //

11'h3a8: data = 8'b00011000; // **

11'h3a9: data = 8'b00011000; // **

11'h3aa: data = 8'b00000000; //

11'h3ab: data = 8'b00000000; //

11'h3ac: data = 8'b00000000; //

11'h3ad: data = 8'b00000000; //

11'h3ae: data = 8'b00000000; //

11'h3af: data = 8'b00000000; //

default: data = 8'b00000000;

endcase

end

endmodule

module bin2bcd(

input wire [4:0] bin,

output wire [7:0] bcd

);

integer i;

// always @(bin) begin

// bcd = 8'b0;

// for (i = 0; i < 5; i = i + 1) begin

// if (bcd[3:0] >= 5) begin

// bcd[3:0] = bcd[3:0] + 3;

// end

// if (bcd[7:4] >= 5) begin

// bcd[7:4] = bcd[7:4] + 3;

// end

// bcd = {bcd[6:0], bin[5-i]};

// end

// end

reg [3:0] ones;

reg [3:0] tens;

always @(bin) begin

ones = 4'b0;

tens = 4'b0;

for (i = 4; i >=0; i = i - 1) begin

if (ones >= 5) begin

ones = ones + 3;

end

if (tens >= 5) begin

tens = tens + 3;

end

tens = {tens[2:0], ones[3]};

ones = {ones[2:0], bin[i]};

end

end

assign bcd = {tens, ones};

endmodule

module clock_divider(

input wire clk,

input wire rst,

output reg clk_div

);

always @(posedge clk) begin

if (rst) begin

clk_div <= 1'b0;

end else begin

clk_div <= ~clk_div;

end

end

endmodule

module dvi_module (

input wire clk,

input wire clk_locked,

//鍥惧儚杈撳嚭淇″彿

output wire [2:0] video_red, //绾㈣壊鍍忕礌锛?3浣?

output wire [2:0] video_green, //缁胯壊鍍忕礌锛?3浣?

output wire [1:0] video_blue, //钃濊壊鍍忕礌锛?2浣?

output wire video_hsync, //琛屽悓姝ワ紙姘村钩鍚屾锛変俊鍙?

output wire video_vsync, //鍦哄悓姝ワ紙鍨傜洿鍚屾锛変俊鍙?

output wire video_clk, //鍍忕礌鏃堕挓杈撳嚭

output wire video_de, //琛屾暟鎹湁鏁堜俊鍙凤紝鐢ㄤ簬鍖哄垎娑堥殣鍖?

input wire [79:0] line_0_ascii, //姣忎釜ascii鐮佸崰8浣?

input wire [79:0] line_1_ascii,

input wire [ 4:0] line_2_number,

output wire [15:0] line_2_ascii_to_top

);

assign line_2_ascii_to_top = line_2_ascii[15:0];

wire [ 7:0] line_2_bcd;

wire [79:0] line_2_ascii;

bin2bcd bcd_inst (

.bin(line_2_number),

.bcd(line_2_bcd)

);

assign line_2_ascii[7:0] = line_2_bcd[3:0] + 8'h30;

assign line_2_ascii[15:8] = line_2_bcd[7:4] + 8'h30;

assign line_2_ascii[79:16] = 64'h0;

// display sync signals and coordinaties

localparam CORDW = 10; // screen coordinate width in bits

logic [CORDW-1:0] sx, sy;

logic hsync, vsync, de;

simple_480p display_inst (

.clk_pix(clk),

.rst_pix(clk_locked), // wait for clock lock

.sx,

.sy,

.hsync,

.vsync,

.de

);

wire [3:0] column_from_left;

wire [3:0] line_from_top;

localparam MAX_COLUMN = 10;

localparam MAX_LINE = 3;

assign column_from_left = sx[9:6]; // 64 bit per column, 640 / 64 = 10 columns (MAX column) 4'b1010

assign line_from_top = sy[9:7]; // 480 / 128 = 3 lines (MAX line) 4'b0011

wire [7:0] ascii;

// wire []

wire [6:0] column_location;

assign column_location = column_from_left << 3;

assign ascii = (line_from_top == 0) ? line_0_ascii[79-column_location -: 8] :

(line_from_top == 1) ? line_1_ascii[79-column_location -: 8] :

(line_from_top == 2) ? line_2_ascii[79-column_location -: 8] :

8'b0;

wire [7:0] ascii_rom_line;

wire [2:0] ascii_column;

wire [3:0] ascii_line;

assign ascii_column = sx[5:3]; // 鏀惧ぇ8鍊嶏紝榛樿鐘舵?佷笅锛?1鍊嶇姸鎬佷笅锛夛紝涓?涓瓧绗︽í鍚戝崰8涓儚绱?

assign ascii_line = sy[6:3]; // 鏀惧ぇ8鍊嶏紝榛樿鐘舵?佷笅锛?1鍊嶇姸鎬佷笅锛夛紝涓?涓瓧绗︾旱鍚戝崰16涓儚绱?

ascii_rom_async ascii_rom_inst (

.addr({ascii[6:0], ascii_line}),

.data(ascii_rom_line)

);

wire draw_ascii;

assign draw_ascii = ascii_rom_line[7-ascii_column];

// paint colour: yellow lines, blue background

logic [3:0] paint_r, paint_g, paint_b;

always_comb begin

paint_r = (draw_ascii) ? 4'hF : 4'h1;

paint_g = (draw_ascii) ? 4'hC : 4'h3;

paint_b = (draw_ascii) ? 4'h0 : 4'h7;

end

// display colour: paint colour but black in blanking interval

logic [3:0] display_r, display_g, display_b;

always_comb begin

display_r = (de) ? paint_r : 4'h0;

display_g = (de) ? paint_g : 4'h0;

display_b = (de) ? paint_b : 4'h0;

end

reg vga_hsync, vga_vsync;

reg [3:0] vga_r, vga_g, vga_b;

// VGA Pmod output

always_ff @(posedge clk) begin

vga_hsync <= hsync;

vga_vsync <= vsync;

vga_r <= display_r;

vga_g <= display_g;

vga_b <= display_b;

end

assign video_clk = clk;

assign video_hsync = hsync;

assign video_vsync = vsync;

assign video_red = display_r[3:1];

assign video_green = display_g[3:1];

assign video_blue = display_b[3:2];

assign video_de = de;

endmodule

module simple_480p (

input wire logic clk_pix, // pixel clock

input wire logic rst_pix, // reset in pixel clock domain

output logic [9:0] sx, // horizontal screen position

output logic [9:0] sy, // vertical screen position

output logic hsync, // horizontal sync

output logic vsync, // vertical sync

output logic de // data enable (low in blanking interval)

);

// horizontal timings

parameter HA_END = 639; // end of active pixels

parameter HS_STA = HA_END + 16; // sync starts after front porch 655

parameter HS_END = HS_STA + 96; // SYNC ENDS

parameter LINE = 799; // last pixel on line (after back porch)

// vertical timings

parameter VA_END = 479; // end of active pixels

parameter VS_STA = VA_END + 10; // sync starts after front porch

parameter VS_END = VS_STA + 2; // sync ends

parameter SCREEN = 524; // last line on screen (after back porch)

always_comb begin

hsync = ~(sx >= HS_STA && sx < HS_END); // invert: negative polarity

vsync = ~(sy >= VS_STA && sy < VS_END); // invert: negative polarity

de = (sx <= HA_END && sy <= VA_END);

end

// CALCULATE HORIZONTAL AND VERTICAL SCREEN POSTITION

always_ff @(posedge clk_pix) begin

if (sx == LINE) begin // last pixel on line ?

sx <= 0;

sy <= (sy == SCREEN) ? 0 : sy + 1; // last line on screen ?

end else begin

sx <= sx + 1;

end

if (rst_pix) begin

sx <= 0;

sy <= 0;

end

end

endmodule

module test_bin2bcd;

reg [4:0] bin;

wire [7:0] bcd;

// Instantiate the module

bin2bcd u_bin2bcd (

.bin(bin),

.bcd(bcd)

);

initial begin

// Test case 1: binary 0

bin = 5'b00000;

#10;

$display("bin: %b, bcd: %b", bin, bcd);

// Test case 2: binary 10

bin = 5'b01010;

#10;

$display("bin: %b, bcd: %b", bin, bcd);

// Test case 3: binary 31

bin = 5'b11111;

#10;

$display("bin: %b, bcd: %b", bin, bcd);

// Add more test cases as needed

end

endmodule

DEDESHOW.v

`timescale 1ns / 1ps

module DEDESHOW(

//娑叉櫠妯″潡杈撳叆杈撳嚭

input wire reset_btn,//澶嶄綅鎸夐挳淇″彿

output wire [2:0] video_red, //绾㈣壊鍍忕礌锛?3浣?

output wire [2:0] video_green, //缁胯壊鍍忕礌锛?3浣?

output wire [1:0] video_blue, //钃濊壊鍍忕礌锛?2浣?

output wire video_hsync, //琛屽悓姝ワ紙姘村钩鍚屾锛変俊鍙?

output wire video_vsync, //鍦哄悓姝ワ紙鍨傜洿鍚屾锛変俊鍙?

output wire video_clk, //鍍忕礌鏃堕挓杈撳嚭

output wire video_de, //琛屾暟鎹湁鏁堜俊鍙凤紝鐢ㄤ簬鍖哄垎娑堥殣鍖?

input wire CP,

input wire RESETn,

input wire AS,

input wire BS,

output wire T27,

output wire T3,

output wire C3,

output wire C27,

output wire AG,

output wire AY,

output wire AR,

output wire BG,

output wire BY,

output wire BR,

output wire AK,

output wire BK,

//output wire [7:0] QT27,

//output wire [3:0] QT3,

output wire [1:0] QS

);

wire [7:0] QT270;

wire [3:0] QT30;

wire AG0,AY0,AR0;

wire BG0,BY0,BR0;

reg [3:0]Ashi;

reg [3:0]Age;

reg [3:0] Bshi;

reg [3:0] Bge;

reg [3:0] Cshi;

reg [3:0] Cge;

reg [3:0] Dshi;

reg [3:0] Dge;

reg [3:0] Eshi;

reg [3:0] Ege;

reg [3:0] Fshi;

reg [3:0] Fge;

wire [3:0] ten;

wire [3:0] one;

DEDE u0(

.CP(CP),

.RESETn(RESETn),

.AS(AS),

.BS(BS),

.T27(T27),

.T3(T3),

.C3(C3),

.C27(C27),

.AG(AG),

.AY(AY),

.AR(AR),

.BG(BG),

.BY(BY),

.BR(BR),

.AK(AK),

.BK(BK),

.QT27(QT270),

.QT3(QT30),

.QS(QS),

.ten(ten),

.one(one)

);

//assign QT27=QT270;

//assign QT3=QT30;

//assign QT270=QT270+1;

//assign QT30=QT30+1;

/*wire [1:0] hun1;

wire [3:0] ten1;

wire [3:0] one1;

EightBit_to_BCD u1(

.bitnary(QT270), //鍘熷叓浣嶄簩杩涘埗鏁?

.hun(hun1), //鐧句綅

.ten(ten1), //鍗佷綅

.one(one1) //涓綅

);*/

always @(QS,ten,one,QT270,QT30,AK,BK)

begin

case(QS)

2'b00:begin

Ashi=ten;Age=one;Bshi=4'b0000;Bge=4'b0000;Cshi=4'b0000;Cge=4'b0000;Dshi=4'b0000;Dge=4'b0000;Eshi=4'b0000;Ege=4'b0000;Fshi=ten;Fge=one;

end

2'b01:begin

Ashi=4'b0000;Age=4'b0000;Bshi=4'b0000;Bge=QT30+1;Cshi=4'b0000;Cge=4'b0000;Dshi=4'b0000;Dge=4'b0000;Eshi=4'b0000;Ege=4'b0000;Fshi=4'b0010;Fge=4'b0111+QT30;

end

2'b10: begin

Ashi=4'b0000;Age=4'b0000;Bshi=4'b0000;Bge=4'b0000;Cshi=ten;Cge=one;Dshi=ten;Dge=one;Eshi=4'b0000;Ege=4'b0000;Fshi=4'b0000;Fge=4'b0000;

end

2'b11:begin

Ashi=4'b0000;Age=4'b0000;Bshi=4'b0000;Bge=4'b0000;Cshi=4'b0010;Cge=4'b0111+QT30;Dshi=4'b0000;Dge=4'b0000;Eshi=4'b0000;Ege=QT30+1;Fshi=4'b0000;Fge=4'b0000;

end

endcase

end

lcd_top u2(

.clk_50M(CP),

.reset_btn(reset_btn),

.countA_shi(Ashi),

.countA_ge(Age),

.countB_shi(Bshi),

.countB_ge(Bge),

.countC_shi(Cshi),

.countC_ge(Cge),

.countD_shi(Dshi),

.countD_ge(Dge),

.countE_shi(Eshi),

.countE_ge(Ege),

.countF_shi(Fshi),

.countF_ge(Fge),

.video_red(video_red),

.video_green(video_green),

.video_blue(video_blue),

.video_hsync(video_hsync),

.video_vsync(video_vsync),

.video_clk(video_clk),

.video_de(video_de));

endmodule

我一般是不发仿真代码的,但这回题比较难就放上来了

我用的Vivado仿真:

`timescale 1ns / 1ps

module DEDESHOW_tb(

);

reg CP;

reg RESETn;

reg AS;

reg BS;

wire T27;

wire T3;

wire C3;

wire C27;

wire AG ;

wire AY;

wire AR;

wire BG;

wire BY;

wire BR;

wire AK;

wire BK;

//wire [7:0] QT27;

//wire [3:0] QT3;

wire [1:0] QS;

reg reset_btn;

wire [2:0] video_red;

wire [2:0] video_green;

wire [1:0] video_blue;

wire video_hsync;

wire video_vsync;

wire video_clk;

wire video_de;

DEDESHOW t1(

.CP(CP),

.RESETn(RESETn),

.AS(AS),

.BS(BS),

.T27(T27),

. T3(T3),

. C3(C3),

. C27(C27),

. AG(AG),

. AY(AY),

. AR(AR),

. BG(BG),

. BY(BY),

. BR(BR),

. AK(AK),

. BK(BK),

//.QT27(QT27),

//.QT3(QT3),

.QS(QS),

.reset_btn(reset_btn),

.video_red(video_red),

.video_green(video_green),

.video_blue(video_blue),

.video_hsync(video_hsync),

.video_vsync(video_hsync),

.video_clk(video_clk),

.video_de(video_clk)

);

initial begin

RESETn=1'b0;

reset_btn=1'b0;

AS=1'b1;//涓婚亾鏈夎溅

BS=1'b0;//鏀亾娌¤溅

CP=1'b0;

end

initial begin

#10 RESETn=1'b1;reset_btn=1'b0; AS=1'b1;BS=1'b0;

#240 RESETn=1'b1;reset_btn=1'b0; AS=1'b0;BS=1'b0;

#20 RESETn=1'b1;reset_btn=1'b0; AS=1'b0;BS=1'b1;

#240 RESETn=1'b1;reset_btn=1'b0; AS=1'b0;BS=1'b0;

#240 RESETn=1'b1;reset_btn=1'b0; AS=1'b1;BS=1'b0;

#30 RESETn=1'b1;reset_btn=1'b0; AS=1'b1;BS=1'b1;

#500 RESETn=1'b1; reset_btn=1'b0;AS=1'b1;BS=1'b0;

#60 $stop;

end

always #5 CP=~CP;

endmodule

引脚:

#Clock

set_property -dict {PACKAGE_PIN K21 IOSTANDARD LVCMOS33} [get_ports CP] ;#50MHz main clock in

set_property -dict {PACKAGE_PIN H21 IOSTANDARD LVCMOS33} [get_ports clk_11M0592] ;#11.0592MHz clock for UART

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_11M0592_IBUF]

create_clock -period 20.000 -name clk_50M -waveform {0.000 10.000} [get_ports clk_50M]

create_clock -period 90.422 -name clk_11M0592 -waveform {0.000 45.211} [get_ports clk_11M0592]

#Touch Button

set_property -dict {PACKAGE_PIN T2 IOSTANDARD LVCMOS33} [get_ports reset_btn] ;#BTN1

set_property -dict {PACKAGE_PIN M1 IOSTANDARD LVCMOS33} [get_ports touch_btn[1]] ;#BTN2

set_property -dict {PACKAGE_PIN P3 IOSTANDARD LVCMOS33} [get_ports touch_btn[2]] ;#BTN3

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports touch_btn[3]] ;#BTN4

set_property -dict {PACKAGE_PIN U1 IOSTANDARD LVCMOS33} [get_ports clock_btn] ;#BTN5

set_property -dict {PACKAGE_PIN U5 IOSTANDARD LVCMOS33} [get_ports reset_btn] ;#BTN6

#required if touch button used as manual clock source

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clock_btn_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets reset_btn_IBUF]

#CPLD GPIO 12-16

#set_property -dict {PACKAGE_PIN J14 IOSTANDARD LVCMOS33} [get_ports {uart_wrn}]

#set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports {uart_rdn}]

#set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports {uart_tbre}]

#set_property -dict {PACKAGE_PIN K15 IOSTANDARD LVCMOS33} [get_ports {uart_tsre}]

#set_property -dict {PACKAGE_PIN L15 IOSTANDARD LVCMOS33} [get_ports {uart_dataready}]

#Ext serial

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H18} [get_ports txd] ;#GPIO5

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J20} [get_ports rxd] ;#GPIO6

#Digital Video

set_property -dict {PACKAGE_PIN H22 IOSTANDARD LVCMOS33} [get_ports video_clk]

set_property -dict {PACKAGE_PIN E26 IOSTANDARD LVCMOS33} [get_ports {video_red[2]}]

set_property -dict {PACKAGE_PIN F24 IOSTANDARD LVCMOS33} [get_ports {video_red[1]}]

set_property -dict {PACKAGE_PIN K23 IOSTANDARD LVCMOS33} [get_ports {video_red[0]}]

set_property -dict {PACKAGE_PIN F23 IOSTANDARD LVCMOS33} [get_ports {video_green[2]}]

set_property -dict {PACKAGE_PIN E23 IOSTANDARD LVCMOS33} [get_ports {video_green[1]}]

set_property -dict {PACKAGE_PIN K22 IOSTANDARD LVCMOS33} [get_ports {video_green[0]}]

set_property -dict {PACKAGE_PIN D25 IOSTANDARD LVCMOS33} [get_ports {video_blue[1]}]

set_property -dict {PACKAGE_PIN E25 IOSTANDARD LVCMOS33} [get_ports {video_blue[0]}]

set_property -dict {PACKAGE_PIN J24 IOSTANDARD LVCMOS33} [get_ports video_hsync]

set_property -dict {PACKAGE_PIN H24 IOSTANDARD LVCMOS33} [get_ports video_vsync]

set_property -dict {PACKAGE_PIN G24 IOSTANDARD LVCMOS33} [get_ports video_de]

#LEDS

set_property -dict {PACKAGE_PIN B24 IOSTANDARD LVCMOS33} [get_ports {T27}]

set_property -dict {PACKAGE_PIN E21 IOSTANDARD LVCMOS33} [get_ports {T3}]

set_property -dict {PACKAGE_PIN A24 IOSTANDARD LVCMOS33} [get_ports {C27}]

set_property -dict {PACKAGE_PIN D23 IOSTANDARD LVCMOS33} [get_ports {C3}]

set_property -dict {PACKAGE_PIN C22 IOSTANDARD LVCMOS33} [get_ports {AG}]

set_property -dict {PACKAGE_PIN C21 IOSTANDARD LVCMOS33} [get_ports {AY}]

set_property -dict {PACKAGE_PIN E20 IOSTANDARD LVCMOS33} [get_ports {AR}]

set_property -dict {PACKAGE_PIN B22 IOSTANDARD LVCMOS33} [get_ports {BG}]

set_property -dict {PACKAGE_PIN C23 IOSTANDARD LVCMOS33} [get_ports {BY}]

set_property -dict {PACKAGE_PIN A23 IOSTANDARD LVCMOS33} [get_ports {BR}]

set_property -dict {PACKAGE_PIN D21 IOSTANDARD LVCMOS33} [get_ports {AK}]

set_property -dict {PACKAGE_PIN A18 IOSTANDARD LVCMOS33} [get_ports {BK}]

set_property -dict {PACKAGE_PIN D20 IOSTANDARD LVCMOS33} [get_ports {QS[0]}]

set_property -dict {PACKAGE_PIN A22 IOSTANDARD LVCMOS33} [get_ports {QS[1]}]

set_property -dict {PACKAGE_PIN A20 IOSTANDARD LVCMOS33} [get_ports {leds[14]}]

set_property -dict {PACKAGE_PIN B20 IOSTANDARD LVCMOS33} [get_ports {leds[15]}]

#DPY0

set_property -dict {PACKAGE_PIN B19 IOSTANDARD LVCMOS33} [get_ports {dpy0[0]}]

set_property -dict {PACKAGE_PIN D19 IOSTANDARD LVCMOS33} [get_ports {dpy0[1]}]

set_property -dict {PACKAGE_PIN B21 IOSTANDARD LVCMOS33} [get_ports {dpy0[2]}]

set_property -dict {PACKAGE_PIN A19 IOSTANDARD LVCMOS33} [get_ports {dpy0[3]}]

set_property -dict {PACKAGE_PIN E18 IOSTANDARD LVCMOS33} [get_ports {dpy0[4]}]

set_property -dict {PACKAGE_PIN C19 IOSTANDARD LVCMOS33} [get_ports {dpy0[5]}]

set_property -dict {PACKAGE_PIN B17 IOSTANDARD LVCMOS33} [get_ports {dpy0[6]}]

set_property -dict {PACKAGE_PIN C17 IOSTANDARD LVCMOS33} [get_ports {dpy0[7]}]

#DPY1

set_property -dict {PACKAGE_PIN A17 IOSTANDARD LVCMOS33} [get_ports {dpy1[0]}]

set_property -dict {PACKAGE_PIN D16 IOSTANDARD LVCMOS33} [get_ports {dpy1[1]}]

set_property -dict {PACKAGE_PIN E17 IOSTANDARD LVCMOS33} [get_ports {dpy1[2]}]

set_property -dict {PACKAGE_PIN F17 IOSTANDARD LVCMOS33} [get_ports {dpy1[3]}]

set_property -dict {PACKAGE_PIN E16 IOSTANDARD LVCMOS33} [get_ports {dpy1[4]}]

set_property -dict {PACKAGE_PIN G16 IOSTANDARD LVCMOS33} [get_ports {dpy1[5]}]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports {dpy1[6]}]

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {dpy1[7]}]

#DIP_SW

set_property -dict {PACKAGE_PIN T3 IOSTANDARD LVCMOS33} [get_ports {RESETn}]

set_property -dict {PACKAGE_PIN J3 IOSTANDARD LVCMOS33} [get_ports {AS}]

set_property -dict {PACKAGE_PIN M2 IOSTANDARD LVCMOS33} [get_ports {BS}]

set_property -dict {PACKAGE_PIN P1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[3]}]

set_property -dict {PACKAGE_PIN P4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[4]}]

set_property -dict {PACKAGE_PIN L5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[5]}]

set_property -dict {PACKAGE_PIN L3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[6]}]

set_property -dict {PACKAGE_PIN N6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[7]}]

set_property -dict {PACKAGE_PIN M6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[8]}]

set_property -dict {PACKAGE_PIN N7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[9]}]

set_property -dict {PACKAGE_PIN M7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[10]}]

set_property -dict {PACKAGE_PIN L7 IOSTANDARD LVCMOS33} [get_ports {dip_sw[11]}]

set_property -dict {PACKAGE_PIN M5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[12]}]

set_property -dict {PACKAGE_PIN K3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[13]}]

set_property -dict {PACKAGE_PIN J1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[14]}]

set_property -dict {PACKAGE_PIN L2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[15]}]

set_property -dict {PACKAGE_PIN K2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[16]}]

set_property -dict {PACKAGE_PIN K1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[17]}]

set_property -dict {PACKAGE_PIN N3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[18]}]

set_property -dict {PACKAGE_PIN L4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[19]}]

set_property -dict {PACKAGE_PIN M4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[20]}]

set_property -dict {PACKAGE_PIN N2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[21]}]

set_property -dict {PACKAGE_PIN P6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[22]}]

set_property -dict {PACKAGE_PIN N1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[23]}]

set_property -dict {PACKAGE_PIN P5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[24]}]

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports {dip_sw[25]}]

set_property -dict {PACKAGE_PIN T4 IOSTANDARD LVCMOS33} [get_ports {dip_sw[26]}]

set_property -dict {PACKAGE_PIN R1 IOSTANDARD LVCMOS33} [get_ports {dip_sw[27]}]

set_property -dict {PACKAGE_PIN R5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[28]}]

set_property -dict {PACKAGE_PIN T5 IOSTANDARD LVCMOS33} [get_ports {dip_sw[29]}]

set_property -dict {PACKAGE_PIN R6 IOSTANDARD LVCMOS33} [get_ports {dip_sw[30]}]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports {dip_sw[31]}]

set_property -dict {PACKAGE_PIN C2 IOSTANDARD LVCMOS33} [get_ports {flash_a[0]}]

set_property -dict {PACKAGE_PIN H9 IOSTANDARD LVCMOS33} [get_ports {flash_a[1]}]

set_property -dict {PACKAGE_PIN H8 IOSTANDARD LVCMOS33} [get_ports {flash_a[2]}]

set_property -dict {PACKAGE_PIN G9 IOSTANDARD LVCMOS33} [get_ports {flash_a[3]}]

set_property -dict {PACKAGE_PIN H7 IOSTANDARD LVCMOS33} [get_ports {flash_a[4]}]

set_property -dict {PACKAGE_PIN F8 IOSTANDARD LVCMOS33} [get_ports {flash_a[5]}]

set_property -dict {PACKAGE_PIN G8 IOSTANDARD LVCMOS33} [get_ports {flash_a[6]}]

set_property -dict {PACKAGE_PIN K7 IOSTANDARD LVCMOS33} [get_ports {flash_a[7]}]

set_property -dict {PACKAGE_PIN G7 IOSTANDARD LVCMOS33} [get_ports {flash_a[8]}]

set_property -dict {PACKAGE_PIN F7 IOSTANDARD LVCMOS33} [get_ports {flash_a[9]}]

set_property -dict {PACKAGE_PIN E6 IOSTANDARD LVCMOS33} [get_ports {flash_a[10]}]

set_property -dict {PACKAGE_PIN D6 IOSTANDARD LVCMOS33} [get_ports {flash_a[11]}]

set_property -dict {PACKAGE_PIN F5 IOSTANDARD LVCMOS33} [get_ports {flash_a[12]}]

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports {flash_a[13]}]

set_property -dict {PACKAGE_PIN G5 IOSTANDARD LVCMOS33} [get_ports {flash_a[14]}]

set_property -dict {PACKAGE_PIN F4 IOSTANDARD LVCMOS33} [get_ports {flash_a[15]}]

set_property -dict {PACKAGE_PIN H6 IOSTANDARD LVCMOS33} [get_ports {flash_a[16]}]

set_property -dict {PACKAGE_PIN G4 IOSTANDARD LVCMOS33} [get_ports {flash_a[17]}]

set_property -dict {PACKAGE_PIN J6 IOSTANDARD LVCMOS33} [get_ports {flash_a[18]}]

set_property -dict {PACKAGE_PIN H4 IOSTANDARD LVCMOS33} [get_ports {flash_a[19]}]

set_property -dict {PACKAGE_PIN J5 IOSTANDARD LVCMOS33} [get_ports {flash_a[20]}]

set_property -dict {PACKAGE_PIN J4 IOSTANDARD LVCMOS33} [get_ports {flash_a[21]}]

set_property -dict {PACKAGE_PIN K6 IOSTANDARD LVCMOS33} [get_ports {flash_a[22]}]

set_property -dict {PACKAGE_PIN D4 IOSTANDARD LVCMOS33} [get_ports {flash_d[0]}]

set_property -dict {PACKAGE_PIN C1 IOSTANDARD LVCMOS33} [get_ports {flash_d[1]}]

set_property -dict {PACKAGE_PIN D1 IOSTANDARD LVCMOS33} [get_ports {flash_d[2]}]

set_property -dict {PACKAGE_PIN E1 IOSTANDARD LVCMOS33} [get_ports {flash_d[3]}]

set_property -dict {PACKAGE_PIN G1 IOSTANDARD LVCMOS33} [get_ports {flash_d[4]}]

set_property -dict {PACKAGE_PIN A2 IOSTANDARD LVCMOS33} [get_ports {flash_d[5]}]

set_property -dict {PACKAGE_PIN C3 IOSTANDARD LVCMOS33} [get_ports {flash_d[6]}]

set_property -dict {PACKAGE_PIN B4 IOSTANDARD LVCMOS33} [get_ports {flash_d[7]}]

set_property -dict {PACKAGE_PIN D3 IOSTANDARD LVCMOS33} [get_ports {flash_d[8]}]

set_property -dict {PACKAGE_PIN E2 IOSTANDARD LVCMOS33} [get_ports {flash_d[9]}]

set_property -dict {PACKAGE_PIN F3 IOSTANDARD LVCMOS33} [get_ports {flash_d[10]}]

set_property -dict {PACKAGE_PIN F2 IOSTANDARD LVCMOS33} [get_ports {flash_d[11]}]

set_property -dict {PACKAGE_PIN G2 IOSTANDARD LVCMOS33} [get_ports {flash_d[12]}]

set_property -dict {PACKAGE_PIN B2 IOSTANDARD LVCMOS33} [get_ports {flash_d[13]}]

set_property -dict {PACKAGE_PIN A3 IOSTANDARD LVCMOS33} [get_ports {flash_d[14]}]

set_property -dict {PACKAGE_PIN A4 IOSTANDARD LVCMOS33} [get_ports {flash_d[15]}]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD LVCMOS33} [get_ports flash_byte_n]

set_property -dict {PACKAGE_PIN E5 IOSTANDARD LVCMOS33} [get_ports flash_ce_n ]

set_property -dict {PACKAGE_PIN A5 IOSTANDARD LVCMOS33} [get_ports flash_oe_n ]

set_property -dict {PACKAGE_PIN G6 IOSTANDARD LVCMOS33} [get_ports flash_rp_n ]

set_property -dict {PACKAGE_PIN D5 IOSTANDARD LVCMOS33} [get_ports flash_vpen ]

set_property -dict {PACKAGE_PIN B5 IOSTANDARD LVCMOS33} [get_ports flash_we_n ]

set_property -dict {PACKAGE_PIN T19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[0]}]

set_property -dict {PACKAGE_PIN V18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[1]}]

set_property -dict {PACKAGE_PIN T18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[2]}]

set_property -dict {PACKAGE_PIN V17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[3]}]

set_property -dict {PACKAGE_PIN U17 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[4]}]

set_property -dict {PACKAGE_PIN R20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[5]}]

set_property -dict {PACKAGE_PIN R23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[6]}]

set_property -dict {PACKAGE_PIN T23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[7]}]

set_property -dict {PACKAGE_PIN U22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AB24 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AA23 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[11]}]

set_property -dict {PACKAGE_PIN Y21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[12]}]

set_property -dict {PACKAGE_PIN Y20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AA22 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[14]}]

set_property -dict {PACKAGE_PIN W19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[15]}]

set_property -dict {PACKAGE_PIN W21 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[16]}]

set_property -dict {PACKAGE_PIN W20 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[17]}]

set_property -dict {PACKAGE_PIN W18 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[18]}]

set_property -dict {PACKAGE_PIN V19 IOSTANDARD LVCMOS33} [get_ports {base_ram_addr[19]}]

set_property -dict {PACKAGE_PIN L22 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN L20 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN K25 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN L23 IOSTANDARD LVCMOS33} [get_ports {base_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN L24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[0]}]

set_property -dict {PACKAGE_PIN L25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[1]}]

set_property -dict {PACKAGE_PIN M26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[2]}]

set_property -dict {PACKAGE_PIN M25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[3]}]

set_property -dict {PACKAGE_PIN N26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[4]}]

set_property -dict {PACKAGE_PIN P24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[5]}]

set_property -dict {PACKAGE_PIN P26 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[6]}]

set_property -dict {PACKAGE_PIN P25 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[7]}]

set_property -dict {PACKAGE_PIN AA24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[8]}]

set_property -dict {PACKAGE_PIN Y23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[9]}]

set_property -dict {PACKAGE_PIN V21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[10]}]

set_property -dict {PACKAGE_PIN W24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[11]}]

set_property -dict {PACKAGE_PIN W23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[12]}]

set_property -dict {PACKAGE_PIN V22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[13]}]

set_property -dict {PACKAGE_PIN V23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[14]}]

set_property -dict {PACKAGE_PIN U21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[15]}]

set_property -dict {PACKAGE_PIN P21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[16]}]

set_property -dict {PACKAGE_PIN M21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[17]}]

set_property -dict {PACKAGE_PIN P23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[18]}]

set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[19]}]

set_property -dict {PACKAGE_PIN N19 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[20]}]

set_property -dict {PACKAGE_PIN M20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[21]}]

set_property -dict {PACKAGE_PIN N24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[22]}]

set_property -dict {PACKAGE_PIN N21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[23]}]

set_property -dict {PACKAGE_PIN T22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[24]}]

set_property -dict {PACKAGE_PIN R22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[25]}]

set_property -dict {PACKAGE_PIN R21 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[26]}]

set_property -dict {PACKAGE_PIN P20 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[27]}]

set_property -dict {PACKAGE_PIN N22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[28]}]

set_property -dict {PACKAGE_PIN N23 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[29]}]

set_property -dict {PACKAGE_PIN M24 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[30]}]

set_property -dict {PACKAGE_PIN M22 IOSTANDARD LVCMOS33} [get_ports {base_ram_data[31]}]

set_property -dict {PACKAGE_PIN U19 IOSTANDARD LVCMOS33} [get_ports base_ram_ce_n]

set_property -dict {PACKAGE_PIN T20 IOSTANDARD LVCMOS33} [get_ports base_ram_oe_n]

set_property -dict {PACKAGE_PIN U20 IOSTANDARD LVCMOS33} [get_ports base_ram_we_n]

set_property -dict {PACKAGE_PIN AF25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[0]}]

set_property -dict {PACKAGE_PIN AE25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[1]}]

set_property -dict {PACKAGE_PIN AE26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[2]}]

set_property -dict {PACKAGE_PIN AD25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[3]}]

set_property -dict {PACKAGE_PIN AD26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[4]}]

set_property -dict {PACKAGE_PIN AC22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[5]}]

set_property -dict {PACKAGE_PIN Y17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[6]}]

set_property -dict {PACKAGE_PIN AA18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[7]}]

set_property -dict {PACKAGE_PIN AA17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[8]}]

set_property -dict {PACKAGE_PIN Y25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[9]}]

set_property -dict {PACKAGE_PIN AA25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[10]}]

set_property -dict {PACKAGE_PIN AB26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[11]}]

set_property -dict {PACKAGE_PIN AB25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[12]}]

set_property -dict {PACKAGE_PIN AC26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[13]}]

set_property -dict {PACKAGE_PIN AC24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[14]}]

set_property -dict {PACKAGE_PIN AF17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[15]}]

set_property -dict {PACKAGE_PIN AE17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[16]}]

set_property -dict {PACKAGE_PIN AF18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[17]}]

set_property -dict {PACKAGE_PIN AE18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[18]}]

set_property -dict {PACKAGE_PIN AF19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_addr[19]}]

set_property -dict {PACKAGE_PIN R25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[1]}]

set_property -dict {PACKAGE_PIN R26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[0]}]

set_property -dict {PACKAGE_PIN AB22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[3]}]

set_property -dict {PACKAGE_PIN AD24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_be_n[2]}]

set_property -dict {PACKAGE_PIN AF24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[0]}]

set_property -dict {PACKAGE_PIN AE23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[1]}]

set_property -dict {PACKAGE_PIN AF23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[2]}]

set_property -dict {PACKAGE_PIN AE22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[3]}]

set_property -dict {PACKAGE_PIN AF22 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[4]}]

set_property -dict {PACKAGE_PIN AE21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[5]}]

set_property -dict {PACKAGE_PIN AE20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[6]}]

set_property -dict {PACKAGE_PIN AF20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[7]}]

set_property -dict {PACKAGE_PIN Y26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[8]}]

set_property -dict {PACKAGE_PIN W25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[9]}]

set_property -dict {PACKAGE_PIN W26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[10]}]

set_property -dict {PACKAGE_PIN V24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[11]}]

set_property -dict {PACKAGE_PIN V26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[12]}]

set_property -dict {PACKAGE_PIN U25 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[13]}]

set_property -dict {PACKAGE_PIN U26 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[14]}]

set_property -dict {PACKAGE_PIN U24 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[15]}]

set_property -dict {PACKAGE_PIN AB16 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[16]}]

set_property -dict {PACKAGE_PIN AC19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[17]}]

set_property -dict {PACKAGE_PIN AB17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[18]}]

set_property -dict {PACKAGE_PIN AC18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[19]}]

set_property -dict {PACKAGE_PIN AD18 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[20]}]

set_property -dict {PACKAGE_PIN AC16 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[21]}]

set_property -dict {PACKAGE_PIN Y15 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[22]}]

set_property -dict {PACKAGE_PIN AA15 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[23]}]

set_property -dict {PACKAGE_PIN AD17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[24]}]

set_property -dict {PACKAGE_PIN AC17 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[25]}]

set_property -dict {PACKAGE_PIN AD20 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[26]}]

set_property -dict {PACKAGE_PIN AB21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[27]}]

set_property -dict {PACKAGE_PIN AD21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[28]}]

set_property -dict {PACKAGE_PIN AC21 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[29]}]

set_property -dict {PACKAGE_PIN AA19 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[30]}]

set_property -dict {PACKAGE_PIN AC23 IOSTANDARD LVCMOS33} [get_ports {ext_ram_data[31]}]

set_property -dict {PACKAGE_PIN AD23 IOSTANDARD LVCMOS33} [get_ports ext_ram_ce_n]

set_property -dict {PACKAGE_PIN AB19 IOSTANDARD LVCMOS33} [get_ports ext_ram_oe_n]

set_property -dict {PACKAGE_PIN AD19 IOSTANDARD LVCMOS33} [get_ports ext_ram_we_n]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

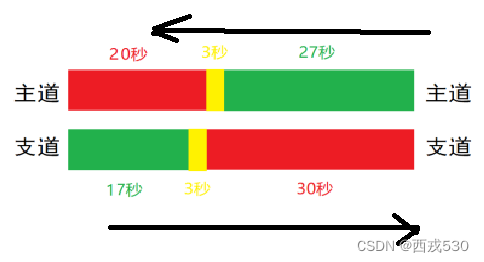

扩展题1:

当两个方向同时有车时,主道红、绿灯每隔30秒变换一次,支道每隔20秒变换一次。

图2主道与支道信号灯时间不相等状态图

- 图2采用置最大时间、减计时;例如置27后每隔1秒减1。

DEN.v

`timescale 1ns / 1ps

module DEN(

input wire CLK,

input wire RSTn,

input wire AS,

input wire BS,

output wire [1:0] state,

output wire [5:0] led,

output wire [5:0] A_time,

output wire [5:0] B_time,

//output wire AK, // 主道由绿转黄信号

// output wire BK, // 支道由绿转黄信号

output wire [3:0] ten2,

output wire [3:0] one2,

output wire [3:0] ten1,

output wire [3:0] one1,

output wire AG, // 主道绿灯信号

output wire AY, // 主道黄灯信号

output wire AR, // 主道红灯信号

output wire BG, // 支道绿灯信号

output wire BY, // 支道黄灯信号

output wire BR // 支道红灯信号

);

parameter TIME_LED_Y=6'd3;

parameter TIME_LED_AG=6'd27;

parameter TIME_LED_BG=6'd17;

wire T3,T17,T27;

wire C3,C17,C27;

wire [5:0] SD3,SD17,SD27;

wire LD3n,LD17n,LD27n;

assign BR = led[5];

assign BG = led[4];

assign BY = led[3];

assign AR = led[2];

assign AG = led[1];

assign AY = led[0];

assign ten2[1:0] = SD27[5:4];

assign one2 = SD27[3:0];

assign ten1[1:0] = SD17[5:4];

assign one1 = SD17[3:0];

assign ten2[3:2] =2'b00;

assign ten1[3:2] =2'b00;

control UC(

.CLK(CLK),

.RSTn(RSTn),

.AS(AS),

.BS(BS),

.T3(T3),

.T17(T17),

.T27(T27),

.SD3(SD3),

.SD17(SD17),

.SD27(SD27),

.C3(C3),

.C17(C17),

.C27(C27),

.LD3n(LD3n),

.LD17n(LD17n),

.LD27n(LD27n),

.state(state),

.A_time(A_time),

.B_time(B_time),

.led(led)

);

count_sub UD3(

.CLK(CLK),

.LDn(LD3n),

.E(C3),

.PD(TIME_LED_Y -1'b1),

.QT(SD3),

.RCO(T3)

);

count_sub UD17(

.CLK(CLK),

.LDn(LD17n),

.E(C17),

.PD(TIME_LED_BG -1'b1),

.QT(SD17),

.RCO(T17)

);

count_sub UD27(

.CLK(CLK),

.LDn(LD27n),

.E(C27),

.PD(TIME_LED_AG -1'b1),

.QT(SD27),

.RCO(T27)

);

endmodule

module control(CLK,RSTn,AS,BS,T3,T17,T27,SD3,SD17,SD27,C3,C17,C27,LD3n,LD17n,LD27n,state,led,A_time,B_time);

input CLK;

input RSTn;

input AS;

input BS;

input T3;

input T17;

input T27;

input [5:0] SD3;

input [5:0] SD17;

input [5:0] SD27;

output C3;

output C17;

output C27;

output LD3n;

output LD17n;

output LD27n;

output [1:0] state;

output [5:0] led;

output [5:0] A_time;

output [5:0] B_time;

parameter timeLEDY=6'd3;//黄灯发光时间

parameter [1:0] S0=2'b00, S1=2'b01,S2=2'b10,S3=2'b11;

reg [1:0] cur_State,next_State;

reg [5:0] control_led,control_A_time,control_B_time;

reg control_C3,control_C17,control_C27;

reg control_LD3n,control_LD17n,control_LD27n;

wire AK,BK;

assign AK=BS&T27|BS&~AS;

assign BK=~BS|AS&T17;

assign state=cur_State;

assign led=control_led;

assign A_time=control_A_time;

assign B_time=control_B_time;

assign C3=control_C3;

assign C17=control_C17;

assign C27=control_C27;

assign LD3n=control_LD3n;

assign LD17n=control_LD17n;

assign LD27n=control_LD27n;

//分频模块

reg [28:0] cnt;

reg clk1hz;

//50MHZ转1HZ

always @(posedge CLK)

begin

if(cnt !=28'd24999999)

cnt<=cnt+1;

else cnt<=28'd0;

end

always @(posedge CLK) begin

if(cnt==28'd0)

clk1hz<=~clk1hz;

end

//状态机组合逻辑

always @(*) begin

case (cur_State)

S0: if(AK) next_State<=S1;

else next_State<=S0;

S1: if(T3) next_State<=S2;

else next_State<=S1;

S2: if(BK) next_State<=S3;

else next_State<=S2;

S3: if(T3) next_State<=S0;

else next_State<=S3;

endcase

end

//状态机的状态寄存器

always @(posedge clk1hz or negedge RSTn) begin

if(!RSTn) cur_State<=S0;

else cur_State<=next_State;

end

//状态机输出的组合逻辑

always @(*) begin

if(!RSTn) begin

control_led<=6'b100100;

control_LD27n<=1'b0;

control_C27<=1'b1;

control_C17<=1'b0;

control_C3<=1'b0;

end

else begin

case (state)

S0: begin

control_C27<=1'b1;

control_LD27n<=1'b1;

control_C17<=1'b0;

control_C3<=1'b0;

control_LD3n<=1'b0;

control_A_time<=SD27;

control_B_time<=SD27+timeLEDY;//B红灯的时间比A绿灯时间长3s

control_led<=6'b100010;

end

S1: begin

control_C27<=1'b0;

control_C17<=1'b0;

control_LD17n<=1'b0;

control_C3<=1'b1;

control_LD3n<=1'b1;

control_A_time<=SD3;

control_B_time<=SD3;

control_led<=6'b100001;

end

S2: begin

control_C27<=1'b0;

control_C17<=1'b1;

control_LD17n<=1'b1;

control_C3<=1'b0;

control_LD3n<=1'b0;

control_A_time<=SD17+timeLEDY;

control_B_time<=SD17;

control_led<=6'b010100;

end

S3: begin

control_C27<=1'b0;

control_LD27n<=1'b0;

control_C17<=1'b0;

control_C3<=1'b1;

control_LD3n<=1'b1;

control_A_time<=SD3;

control_B_time<=SD3;

control_led<=6'b001100;

end

default: begin

control_LD27n<=1'b0;

control_C27<=1'b0;

control_C17<=1'b0;

control_C3<=1'b0;

control_led<=6'b100100;

end

endcase

end

end

endmodule

module count_sub(CLK,LDn,E,PD,QT,RCO);

input CLK;

input LDn;

input E;

input [5:0] PD;

output wire [5:0] QT;

output wire RCO;

reg [5:0] SQ;

assign RCO=~SQ[5]&~SQ[4]&~SQ[3]&~SQ[2]&~SQ[1]&~SQ[0];

assign QT=SQ;

//分频模块

reg [28:0] cnt;

reg clk1hz;

//50MHZ转1HZ

always @(posedge CLK)

begin

if(cnt !=28'd24999999)

cnt<=cnt+1;

else cnt<=28'd0;

end

always @(posedge CLK) begin

if(cnt==28'd0)

clk1hz<=~clk1hz;

end

always @(posedge clk1hz or negedge LDn) begin

//always @( posedge CLK) begin

if(!LDn)

SQ<=PD;

else begin

if(E) begin

if(SQ==0)

SQ<=PD;

else

SQ<=SQ-1;

end

end

end

endmodule

module EightBit_to_BCD(

input [7:0] bitnary,

output reg [1:0] hun,

output reg [1:0] hun,

output reg [3:0] one

);

integer i;

wire a=2'b00;

wire b=4'b0000;

reg [17:0] t;

always @(bitnary) begin

hun=a;

ten=b;

one=b;

t={hun,ten,one,bitnary};

for(i=0;i<8;i=i+1)

begin

if(t[11:8]>=5)

t[11:8]=t[11:8]+3;

if(t[15:12]>=5)

t[15:12]=t[15:12]+3;

t=t<<1;

end

hun=t[17:16];

ten=t[15:12];

one=t[11:8];

end

endmodule

lcd_top.sv

`default_nettype none `timescale 1ns / 1ps

module lcd_top (

input wire clk_50M, //50MHz 鏃堕挓杈撳叆

input wire reset_btn, //BTN6鎵嬪姩澶嶄綅鎸夐挳寮?鍏筹紝甯︽秷鎶栫數璺紝鎸変笅鏃朵负1

input wire [3:0] countA_shi,

input wire [3:0] countA_ge,

input wire [3:0] countB_shi,

input wire [3:0] countB_ge,

input wire [3:0] countC_shi,

input wire [3:0] countC_ge,

input wire [3:0] countD_shi,

input wire [3:0] countD_ge,

input wire [3:0] countE_shi,

input wire [3:0] countE_ge,

input wire [3:0] countF_shi,

input wire [3:0] countF_ge,

output wire leds,

//鍥惧儚杈撳嚭淇″彿

output wire [2:0] video_red, //绾㈣壊鍍忕礌锛?3浣?

output wire [2:0] video_green, //缁胯壊鍍忕礌锛?3浣?

output wire [1:0] video_blue, //钃濊壊鍍忕礌锛?2浣?

output wire video_hsync, //琛屽悓姝ワ紙姘村钩鍚屾锛変俊鍙?

output wire video_vsync, //鍦哄悓姝ワ紙鍨傜洿鍚屾锛変俊鍙?

output wire video_clk, //鍍忕礌鏃堕挓杈撳嚭

output wire video_de //琛屾暟鎹湁鏁堜俊鍙凤紝鐢ㄤ簬鍖哄垎娑堥殣鍖?

);

// generate pixel clock

logic clk_pix;

logic clk_pix_locked;

clock_divider clock_div_inst (

.clk(clk_50M),

.rst(reset_btn),

.clk_div(clk_pix)

);

wire [15:0] line_2_ascii;

dvi_module dvi_inst (

.clk(clk_pix),

.clk_locked(reset_btn),

.video_red(video_red),

.video_green(video_green),

.video_blue(video_blue),

.video_hsync(video_hsync),

.video_vsync(video_vsync),

.video_clk(video_clk),

.video_de(video_de),

.line_0_ascii(line_0),

.line_1_ascii(line_1),

// .line_2_number( )

.line_2_number(number)

// .line_2_ascii_to_top(line_2_ascii)

);

assign leds =1'b0 ;

//line_2_ascii[15:0];

wire [79:0] line_0; // 涓轰簡鏂逛究璧嬪?硷紝涓?涓猘scii鍗犵敤8bit

wire [79:0] line_1; // 56-bit line buffer, 7 bit per ascii character

// wire [7:0] countA_shi;

// wire [7:0] countA_ge;

// wire [7:0] countB_shi;

// wire [7:0] countB_ge;

// wire [7:0] countC_shi;

// wire [7:0] countC_ge;

// wire [7:0] countD_shi;

// wire [7:0] countD_ge;

// assign countA_shi=ascii;

// assign countA_ge=ascii;

// assign countB_shi=ascii;

// assign countB_ge=ascii;

// assign countC_shi=ascii;

// assign countC_ge=ascii;

// assign countD_shi=ascii;

// assign countD_ge=ascii;

// assign line_0 = {{8{ascii}},countA_shi+30,countA_shi+30,countA_shi+30,countA_shi+30, line_2_ascii};

assign line_0 = {8'h20,countB_shi+8'h30,countA_shi+8'h30,countA_ge+8'h30,countC_shi+8'h30,countC_ge+8'h30,countD_shi+8'h30,countD_ge+8'h30,8'h20};

assign line_1 = {8'h20,countE_shi+8'h30,countE_ge+8'h30,8'h20,8'h20,countF_shi+8'h30,countF_ge+8'h30, 8'h20};

// assign line_1 = 80'h3a_39_38_37_36_35_34_33_32_31_30;

localparam CNT_1S = 27'd50_000_000;

reg [26:0] cnt;

wire cnt_eq_1s;

assign cnt_eq_1s = cnt==(CNT_1S-1);

always @(posedge clk_50M)

begin

if (reset_btn)

begin

cnt <= 27'd0;

end

else if (cnt_eq_1s)

begin

cnt <= 27'd0;

end

else

begin

cnt <= cnt + 1'b1;

end

end

reg [7:0] ascii;

always @(posedge clk_50M)

begin

if (reset_btn)

begin

ascii <= 8'd0;

end

else if (cnt_eq_1s)

begin

if (ascii == 8'd9)

begin

ascii <= 8'd0;

end

else

begin

ascii <= ascii + 1'b1;

end

end

end

reg [4:0] number;

always @(posedge clk_50M)

begin

if (reset_btn)

begin

number <= 5'h0;

end

else if (cnt_eq_1s)

begin

number <= number + 5'b1;

end

end

endmodule

module ascii_rom_async (

input wire [10:0] addr,

output reg [7:0] data

);

always @(*) begin

case (addr)

// code x30 (0)

11'h300: data = 8'b00000000; //

11'h301: data = 8'b00000000; //

11'h302: data = 8'b00111000; // ***

11'h303: data = 8'b01101100; // ** **

11'h304: data = 8'b11000110; //** **

11'h305: data = 8'b11000110; //** **

11'h306: data = 8'b11000110; //** **

11'h307: data = 8'b11000110; //** **

11'h308: data = 8'b11000110; //** **

11'h309: data = 8'b11000110; //** **

11'h30a: data = 8'b01101100; // ** **

11'h30b: data = 8'b00111000; // ***

11'h30c: data = 8'b00000000; //

11'h30d: data = 8'b00000000; //

11'h30e: data = 8'b00000000; //

11'h30f: data = 8'b00000000; //

// code x31 (1)

11'h310: data = 8'b00000000; //

11'h311: data = 8'b00000000; //

11'h312: data = 8'b00011000; // **

11'h313: data = 8'b00111000; // ***

11'h314: data = 8'b01111000; // ****

11'h315: data = 8'b00011000; // **

11'h316: data = 8'b00011000; // **

11'h317: data = 8'b00011000; // **

11'h318: data = 8'b00011000; // **

11'h319: data = 8'b00011000; // **

11'h31a: data = 8'b01111110; // ******

11'h31b: data = 8'b01111110; // ******

11'h31c: data = 8'b00000000; //

11'h31d: data = 8'b00000000; //

11'h31e: data = 8'b00000000; //

11'h31f: data = 8'b00000000; //

// code x32 (2)

11'h320: data = 8'b00000000; //

11'h321: data = 8'b00000000; //

11'h322: data = 8'b11111110; //*******

11'h323: data = 8'b11111110; //*******

11'h324: data = 8'b00000110; // **

11'h325: data = 8'b00000110; // **

11'h326: data = 8'b11111110; //*******

11'h327: data = 8'b11111110; //*******

11'h328: data = 8'b11000000; //**

11'h329: data = 8'b11000000; //**

11'h32a: data = 8'b11111110; //*******

11'h32b: data = 8'b11111110; //*******

11'h32c: data = 8'b00000000; //

11'h32d: data = 8'b00000000; //

11'h32e: data = 8'b00000000; //

11'h32f: data = 8'b00000000; //

// code x33 (3)

11'h330: data = 8'b00000000; //

11'h331: data = 8'b00000000; //

11'h332: data = 8'b11111110; //*******

11'h333: data = 8'b11111110; //*******

11'h334: data = 8'b00000110; // **

11'h335: data = 8'b00000110; // **

11'h336: data = 8'b00111110; // *****

11'h337: data = 8'b00111110; // *****

11'h338: data = 8'b00000110; // **

11'h339: data = 8'b00000110; // **

11'h33a: data = 8'b11111110; //*******

11'h33b: data = 8'b11111110; //*******

11'h33c: data = 8'b00000000; //

11'h33d: data = 8'b00000000; //

11'h33e: data = 8'b00000000; //

11'h33f: data = 8'b00000000; //

// code x34 (4)

11'h340: data = 8'b00000000; //

11'h341: data = 8'b00000000; //

11'h342: data = 8'b11000110; //** **

11'h343: data = 8'b11000110; //** **

11'h344: data = 8'b11000110; //** **

11'h345: data = 8'b11000110; //** **

11'h346: data = 8'b11111110; //*******

11'h347: data = 8'b11111110; //*******

11'h348: data = 8'b00000110; // **

11'h349: data = 8'b00000110; // **

11'h34a: data = 8'b00000110; // **

11'h34b: data = 8'b00000110; // **

11'h34c: data = 8'b00000000; //

11'h34d: data = 8'b00000000; //

11'h34e: data = 8'b00000000; //

11'h34f: data = 8'b00000000; //

// code x35 (5)

11'h350: data = 8'b00000000; //

11'h351: data = 8'b00000000; //

11'h352: data = 8'b11111110; //*******

11'h353: data = 8'b11111110; //*******

11'h354: data = 8'b11000000; //**

11'h355: data = 8'b11000000; //**

11'h356: data = 8'b11111110; //*******

11'h357: data = 8'b11111110; //*******

11'h358: data = 8'b00000110; // **

11'h359: data = 8'b00000110; // **

11'h35a: data = 8'b11111110; //*******

11'h35b: data = 8'b11111110; //*******

11'h35c: data = 8'b00000000; //

11'h35d: data = 8'b00000000; //

11'h35e: data = 8'b00000000; //

11'h35f: data = 8'b00000000; //

// code x36 (6)

11'h360: data = 8'b00000000; //

11'h361: data = 8'b00000000; //

11'h362: data = 8'b11111110; //*******

11'h363: data = 8'b11111110; //*******

11'h364: data = 8'b11000000; //**

11'h365: data = 8'b11000000; //**

11'h366: data = 8'b11111110; //*******

11'h367: data = 8'b11111110; //*******

11'h368: data = 8'b11000110; //** **

11'h369: data = 8'b11000110; //** **

11'h36a: data = 8'b11111110; //*******

11'h36b: data = 8'b11111110; //*******

11'h36c: data = 8'b00000000; //

11'h36d: data = 8'b00000000; //

11'h36e: data = 8'b00000000; //

11'h36f: data = 8'b00000000; //

// code x37 (7)

11'h370: data = 8'b00000000; //

11'h371: data = 8'b00000000; //

11'h372: data = 8'b11111110; //*******

11'h373: data = 8'b11111110; //*******

11'h374: data = 8'b00000110; // **

11'h375: data = 8'b00000110; // **

11'h376: data = 8'b00000110; // **

11'h377: data = 8'b00000110; // **

11'h378: data = 8'b00000110; // **

11'h379: data = 8'b00000110; // **

11'h37a: data = 8'b00000110; // **

11'h37b: data = 8'b00000110; // **

11'h37c: data = 8'b00000000; //

11'h37d: data = 8'b00000000; //

11'h37e: data = 8'b00000000; //

11'h37f: data = 8'b00000000; //

// code x38 (8)

11'h380: data = 8'b00000000; //

11'h381: data = 8'b00000000; //

11'h382: data = 8'b11111110; //*******

11'h383: data = 8'b11111110; //*******

11'h384: data = 8'b11000110; //** **

11'h385: data = 8'b11000110; //** **

11'h386: data = 8'b11111110; //*******

11'h387: data = 8'b11111110; //*******

11'h388: data = 8'b11000110; //** **

11'h389: data = 8'b11000110; //** **

11'h38a: data = 8'b11111110; //*******

11'h38b: data = 8'b11111110; //*******

11'h38c: data = 8'b00000000; //

11'h38d: data = 8'b00000000; //

11'h38e: data = 8'b00000000; //

11'h38f: data = 8'b00000000; //

// code x39 (9)

11'h390: data = 8'b00000000; //

11'h391: data = 8'b00000000; //

11'h392: data = 8'b11111110; //*******

11'h393: data = 8'b11111110; //*******

11'h394: data = 8'b11000110; //** **

11'h395: data = 8'b11000110; //** **

11'h396: data = 8'b11111110; //*******

11'h397: data = 8'b11111110; //*******

11'h398: data = 8'b00000110; // **

11'h399: data = 8'b00000110; // **

11'h39a: data = 8'b11111110; //*******

11'h39b: data = 8'b11111110; //*******

11'h39c: data = 8'b00000000; //

11'h39d: data = 8'b00000000; //

11'h39e: data = 8'b00000000; //

11'h39f: data = 8'b00000000; //

// code x3a (:)

11'h3a0: data = 8'b00000000; //

11'h3a1: data = 8'b00000000; //

11'h3a2: data = 8'b00000000; //

11'h3a3: data = 8'b00000000; //

11'h3a4: data = 8'b00011000; // **

11'h3a5: data = 8'b00011000; // **

11'h3a6: data = 8'b00000000; //

11'h3a7: data = 8'b00000000; //

11'h3a8: data = 8'b00011000; // **

11'h3a9: data = 8'b00011000; // **

11'h3aa: data = 8'b00000000; //

11'h3ab: data = 8'b00000000; //

11'h3ac: data = 8'b00000000; //

11'h3ad: data = 8'b00000000; //

11'h3ae: data = 8'b00000000; //

11'h3af: data = 8'b00000000; //

default: data = 8'b00000000;

endcase

end

endmodule

module bin2bcd(

input wire [4:0] bin,

output wire [7:0] bcd

);

integer i;

// always @(bin) begin

// bcd = 8'b0;

// for (i = 0; i < 5; i = i + 1) begin

// if (bcd[3:0] >= 5) begin

// bcd[3:0] = bcd[3:0] + 3;

// end

// if (bcd[7:4] >= 5) begin

// bcd[7:4] = bcd[7:4] + 3;

// end

// bcd = {bcd[6:0], bin[5-i]};

// end

// end

reg [3:0] ones;

reg [3:0] tens;

always @(bin) begin

ones = 4'b0;

tens = 4'b0;

for (i = 4; i >=0; i = i - 1) begin

if (ones >= 5) begin

ones = ones + 3;

end

if (tens >= 5) begin

tens = tens + 3;

end

tens = {tens[2:0], ones[3]};

ones = {ones[2:0], bin[i]};

end

end

assign bcd = {tens, ones};

endmodule

module clock_divider(

input wire clk,

input wire rst,

output reg clk_div

);

always @(posedge clk) begin

if (rst) begin

clk_div <= 1'b0;

end else begin

clk_div <= ~clk_div;

end

end

endmodule

module dvi_module (

input wire clk,

input wire clk_locked,

//鍥惧儚杈撳嚭淇″彿

output wire [2:0] video_red, //绾㈣壊鍍忕礌锛?3浣?

output wire [2:0] video_green, //缁胯壊鍍忕礌锛?3浣?

output wire [1:0] video_blue, //钃濊壊鍍忕礌锛?2浣?

output wire video_hsync, //琛屽悓姝ワ紙姘村钩鍚屾锛変俊鍙?

output wire video_vsync, //鍦哄悓姝ワ紙鍨傜洿鍚屾锛変俊鍙?

output wire video_clk, //鍍忕礌鏃堕挓杈撳嚭

output wire video_de, //琛屾暟鎹湁鏁堜俊鍙凤紝鐢ㄤ簬鍖哄垎娑堥殣鍖?

input wire [79:0] line_0_ascii, //姣忎釜ascii鐮佸崰8浣?

input wire [79:0] line_1_ascii,

input wire [ 4:0] line_2_number,

output wire [15:0] line_2_ascii_to_top

);

assign line_2_ascii_to_top = line_2_ascii[15:0];

wire [ 7:0] line_2_bcd;

wire [79:0] line_2_ascii;

bin2bcd bcd_inst (

.bin(line_2_number),

.bcd(line_2_bcd)

);

assign line_2_ascii[7:0] = line_2_bcd[3:0] + 8'h30;

assign line_2_ascii[15:8] = line_2_bcd[7:4] + 8'h30;

assign line_2_ascii[79:16] = 64'h0;

// display sync signals and coordinaties

localparam CORDW = 10; // screen coordinate width in bits

logic [CORDW-1:0] sx, sy;

logic hsync, vsync, de;

simple_480p display_inst (

.clk_pix(clk),

.rst_pix(clk_locked), // wait for clock lock

.sx,

.sy,

.hsync,

.vsync,

.de

);

wire [3:0] column_from_left;

wire [3:0] line_from_top;

localparam MAX_COLUMN = 10;

localparam MAX_LINE = 3;

assign column_from_left = sx[9:6]; // 64 bit per column, 640 / 64 = 10 columns (MAX column) 4'b1010

assign line_from_top = sy[9:7]; // 480 / 128 = 3 lines (MAX line) 4'b0011

wire [7:0] ascii;

// wire []

wire [6:0] column_location;

assign column_location = column_from_left << 3;

assign ascii = (line_from_top == 0) ? line_0_ascii[79-column_location -: 8] :

(line_from_top == 1) ? line_1_ascii[79-column_location -: 8] :

(line_from_top == 2) ? line_2_ascii[79-column_location -: 8] :

8'b0;

wire [7:0] ascii_rom_line;

wire [2:0] ascii_column;

wire [3:0] ascii_line;

assign ascii_column = sx[5:3]; // 鏀惧ぇ8鍊嶏紝榛樿鐘舵?佷笅锛?1鍊嶇姸鎬佷笅锛夛紝涓?涓瓧绗︽í鍚戝崰8涓儚绱?