题目描述:

设计带有异步复位的可加减控制的50进制加减计数器

50进制加减计数器源代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count_50 is

port(clk,rd,updown:in std_logic;

q:out std_logic_vector(5 downto 0));

end count_50;

architecture count of count_50 is

signal y:std_logic_vector(5 downto 0);

begin

process (clk,rd)

begin

if rd = '0'

then y <= "000000";

else

if (clk'event and clk = '0')then

if(updown = '1')then

if y = "110001" then

y <= "000000";

else

y <= y+1;

end if;

else

if y = "000000" then

y <= "110001";

else

y <= y-1;

end if;

end if;

end if;

end if;

end process;

q <= y;

end count;

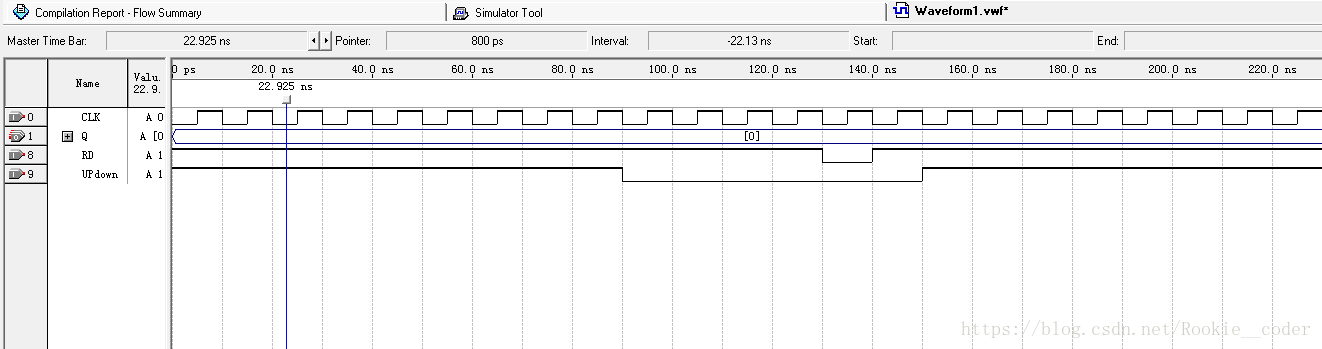

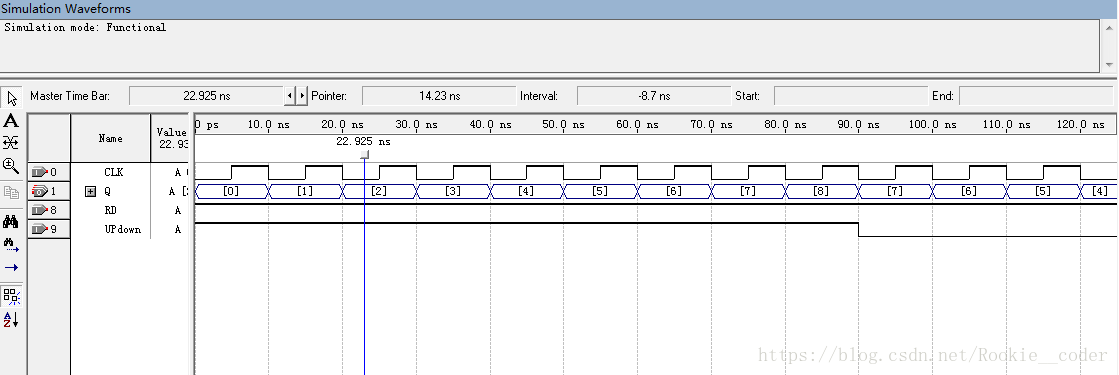

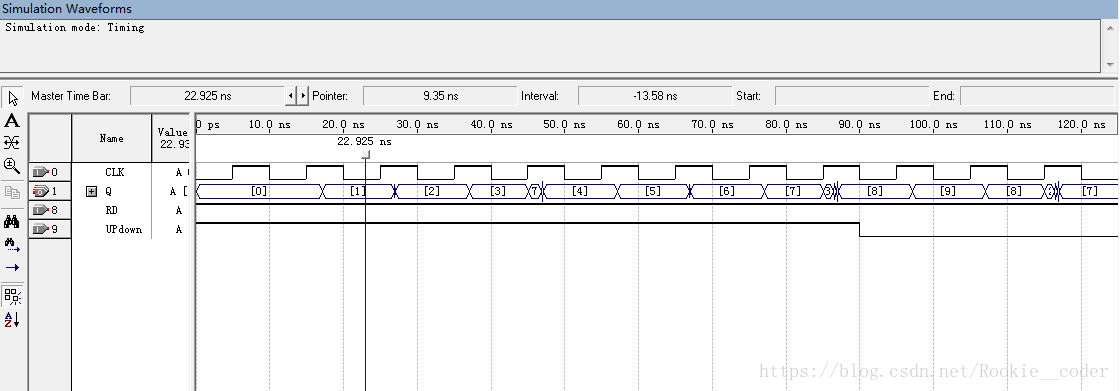

波形图如下:

8671

8671

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?