1 逻辑图

芯片设计离不开时序分析。

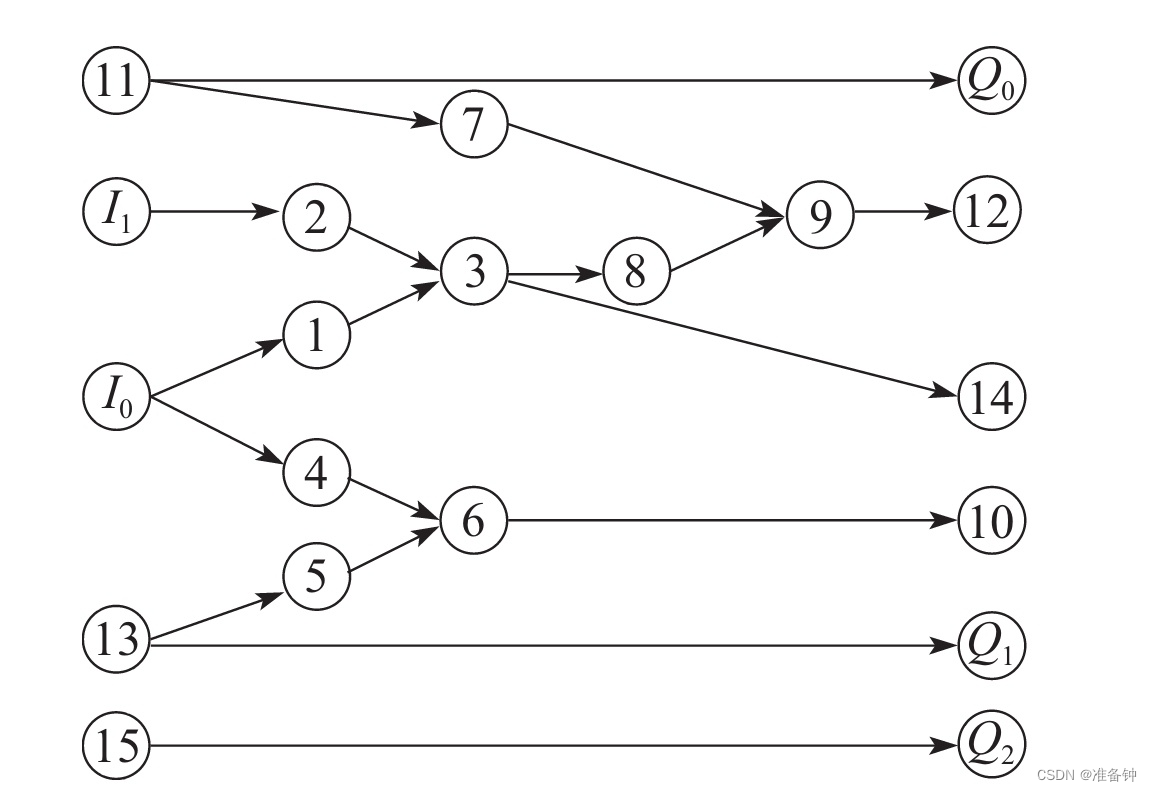

时序分析的对象是如下图这种电路图。

这种电路图被称为逻辑图。

为了分析方便,用编号在图中标出各个节点。

这样就能方便地指出不同的时序路线。

时序分析针对的是一段段时序路线。

因此,首先需要定位出起始点和终点。

什么样的节点可以作为起点和终点呢?

2 起点和终点

起点通常有三种。

第一种:芯片的数据输入端口。

第二种:时序单元的数据输出端口。

第三种:存储器的数据输出端口。

类似地,终点也有三种。

第一种:芯片的数据输出端口。

第二种:时序单元的数据输入端口。

第三种:存储器的数据输入端口。

3 时序图

用节点和箭头来表示刚才逻辑图的时序路径,就得到了下图。

在这个例子中,转换后的时序图具有5个起点,分别是I0、I1、11、13和15;同时也有6个终点,即Q0、Q1、Q2、10、12和14。

这样的图,就是时序图。

有了时序图,就可以进行时序分析了。

4 时序约束

时序图代表了数据传输的方向。

不过图中有的箭头可能在芯片工作中不会发生,而且数据从起点到终点需要满足一定的时间要求。

这就涉及到了时序约束,也就是SDC(Synopsis Design Constraint)。

还有,两个节点之间的延时如何计算?

这些问题,我们后面一一解答。

7871

7871

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?