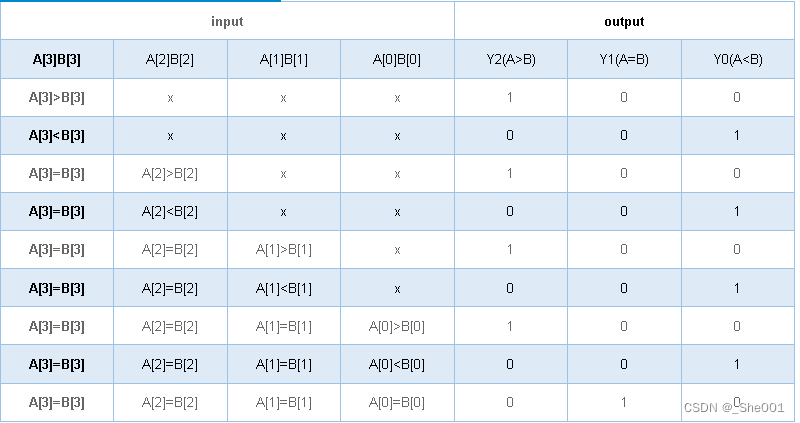

1.VL11 4位数值比较器电路

1.题目:

某4位数值比较器的功能表如下。请用Verilog语言采用门级描述方式,实现此4位数值比较器。

2.解题代码:

`timescale 1ns/1ns

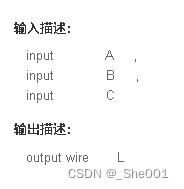

module comparator_4(

input [3:0] A ,

input [3:0] B ,

output wire Y2 , //A>B

output wire Y1 , //A=B

output wire Y0 //A<B

);

wire W2[0:3];

wire W1[0:3];

wire W0[0:3];

genvar i;

for(i=0;i<4;i=i+1)

begin

three_compare U1(

.A (A[i]),

.B (B[i]),

.Y2 (W2[i]),

.Y1 (W1[i]),

.Y0 (W0[i])

);

end

assign Y2 = W2[3] | ((W1[3])&&(W2[2])) | ((W1[3]) && (W1[2]) && (W2[1])) | ((W1[3]) && (W1[2]) && (W1[1]) && (W2[0]));

assign Y0 = W0[3] | ((W1[3])&&(W0[2])) | ((W1[3]) && (W1[2]) && (W0[1])) | ((W1[3]) && (W1[2]) && (W1[1]) && (W0[0]));

assign Y1 = W1[3] & W1[2] & W1[1] &W1[0];

endmodule

//定义另外一个模块 判断三个数的关系

module three_compare(

input A, //输入值 1 或者 0

input B, //输入值 1 或者 0

output Y2, //假如Y2=1 , 这两个数大于

output Y1, //假如Y1=1 ,这两个数等于

output Y0 //假如Y0=1 , 这两个数小于

);

assign Y2 = A & (!B); //持续赋值 Y2 大于的标志

assign Y0 = (!A) & B; //持续赋值 Y0 小于的标志

assign Y1 = !(Y2 | Y0); //持续赋值 , 除非Y2 Y0 都不等于1 那时候Y1 =1

endmodule

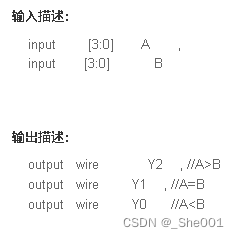

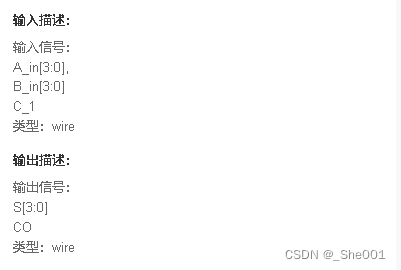

2.VL12 4bit超前进位加法器电路

1.题目:

2.解题代码:

`timescale 1ns/1ns

module lca_4(

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

wire[3:0] G;

wire[3:0] P;

wire[3:0] C;

genvar i;

generate

for(i=0;i<4;i=i+1)

begin

add_half U1(

.A (A_in[i]),

.B (B_in[i]),

.C (G[i]),

.D (P[i])

);

assign S[i] = (i>0) ? P[i]^C[i-1] : P[i]^C_1;

assign C[i] = (i>0) ? G[i] | P[i] & C[i-1] : G[i] + P[i] & C_1;

//assign C[i] = (i == 0) ? (G[i] | (P[i] & C_1)) : (G[i] | (P[i] & C[i-1]));

//assign S[i] = (i == 0) ? (P[i] ^ C_1) : (P[i] ^ C[i-1]);

end

endgenerate

assign CO = C[3];

endmodule

module add_half(

input A,

input B,

output C,

output D

);

assign C = A & B;

assign D = A ^ B;

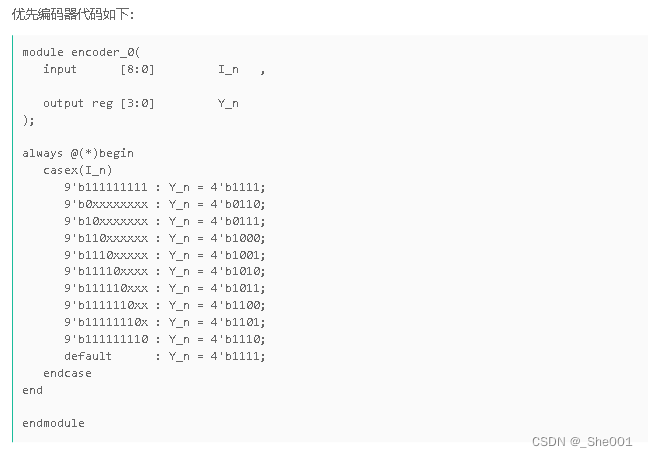

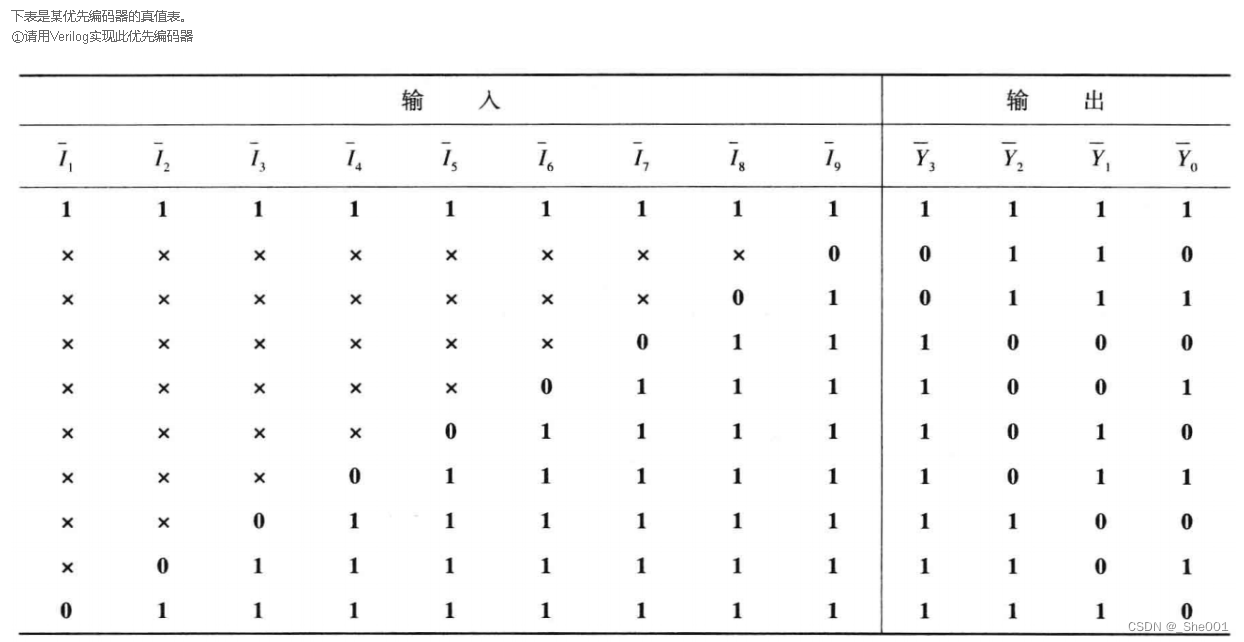

endmodule3.VL13 优先编码器电路①

1.题目:

2.解题代码

`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always@(*)

begin

casex (I_n)

9'b1_1111_1111 : Y_n= 4'b1111;

9'b0_????_???? : Y_n= 4'b0110;

9'b1_0???_???? : Y_n= 4'b0111;

9'b1_10??_???? : Y_n= 4'b1000;

9'b1_110?_???? : Y_n= 4'b1001;

9'b1_1110_???? : Y_n= 4'b1010;

9'b1_1111_0??? : Y_n= 4'b1011;

9'b1_1111_10?? : Y_n= 4'b1100;

9'b1_1111_110? : Y_n= 4'b1101;

9'b1_1111_1110 : Y_n= 4'b1110;

default: Y_n=4'b0000;

endcase

end

endmodule

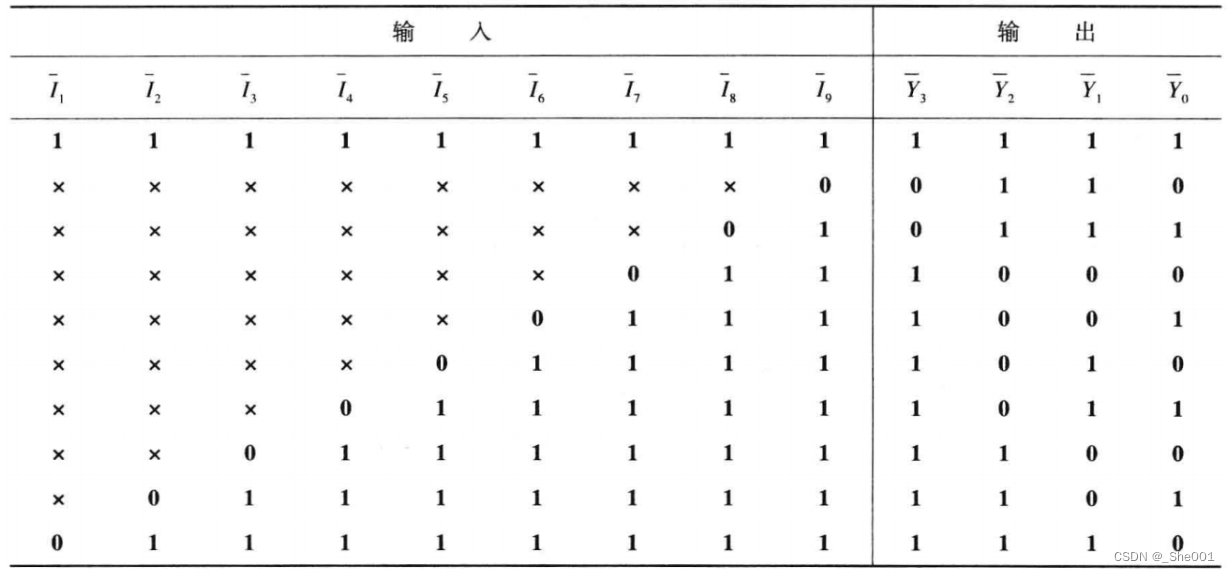

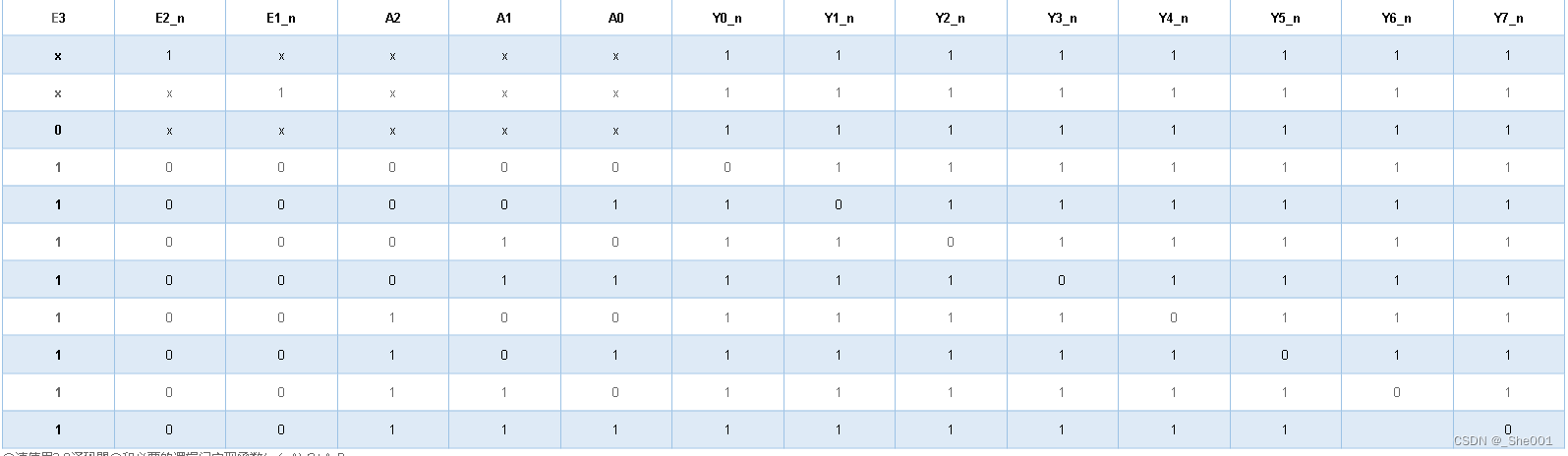

4.VL14 用优先编码器①实现键盘编码电路

1.题目:

请使用优先编码器①实现键盘编码电路,可添加并例化题目中已给出的优先编码器代码。

10个按键分别对应十进制数0-9,按键9的优先级别最高;按键悬空时,按键输出高电平,按键按下时,按键输出低电平;键盘编码电路的输出是8421BCD码。

要求:键盘编码电路要有工作状态标志,以区分没有按键按下和按键0按下两种情况。

优先编码器真值表如下图:

2.解题代码:

`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always @(*)begin

casex(I_n)

9'b111111111 : Y_n = 4'b1111;

9'b0xxxxxxxx : Y_n = 4'b0110;

9'b10xxxxxxx : Y_n = 4'b0111;

9'b110xxxxxx : Y_n = 4'b1000;

9'b1110xxxxx : Y_n = 4'b1001;

9'b11110xxxx : Y_n = 4'b1010;

9'b111110xxx : Y_n = 4'b1011;

9'b1111110xx : Y_n = 4'b1100;

9'b11111110x : Y_n = 4'b1101;

9'b111111110 : Y_n = 4'b1110;

default : Y_n = 4'b1111;

endcase

end

endmodule

module key_encoder(

input [9:0] S_n ,

output wire[3:0] L ,

output wire GS

);

wire[3:0] l_temp;

encoder_0 U1(

.I_n (S_n[9:1]),

.Y_n (l_temp)

);

assign L = ~l_temp;

assign GS = ~(S_n[0] & l_temp[3] & l_temp[2] & l_temp[1] & l_temp[0]);

endmodule5.VL15 优先编码器Ⅰ

1.题目:

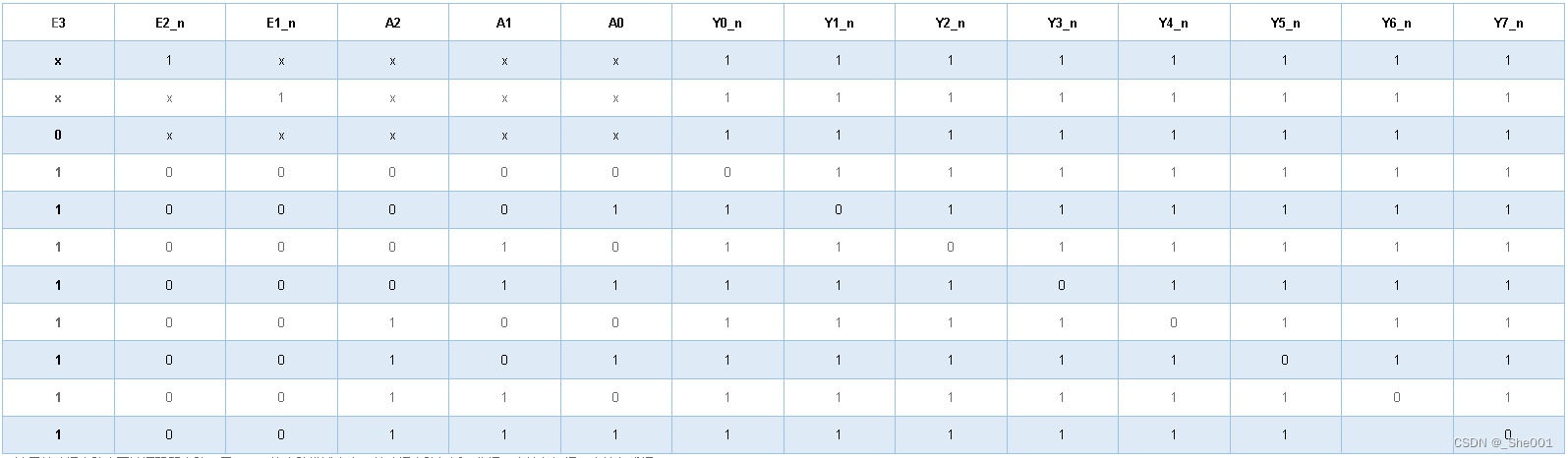

下表是8线-3线优先编码器Ⅰ的功能表。

①请根据该功能表,用Verilog实现该优先编码器Ⅰ。

2.解题代码

`timescale 1ns/1ns

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

reg [2:0] Y_r;

reg GS_r, EO_r;

always@(*) begin

casez({EI, I})

9'b0_????_????: {Y_r, GS_r, EO_r} = 5'b000_0_0;

9'b1_0000_0000: {Y_r, GS_r, EO_r} = 5'b000_0_1;

9'b1_1???_????: {Y_r, GS_r, EO_r} = 5'b111_1_0;

9'b1_01??_????: {Y_r, GS_r, EO_r} = 5'b110_1_0;

9'b1_001?_????: {Y_r, GS_r, EO_r} = 5'b101_1_0;

9'b1_0001_????: {Y_r, GS_r, EO_r} = 5'b100_1_0;

9'b1_0000_1???: {Y_r, GS_r, EO_r} = 5'b011_1_0;

9'b1_0000_01??: {Y_r, GS_r, EO_r} = 5'b010_1_0;

9'b1_0000_001?: {Y_r, GS_r, EO_r} = 5'b001_1_0;

9'b1_0000_0001: {Y_r, GS_r, EO_r} = 5'b000_1_0;

default: {Y_r, GS_r, EO_r} = 5'b000_0_0;

endcase

end

assign Y = Y_r;

assign GS = GS_r;

assign EO = EO_r;

endmodule

6.VL16 使用8线-3线优先编码器工实现16线-4线优先编码器

1.题目 :

请使用2片该优先编码器Ⅰ及必要的逻辑电路实现16线-4线优先编码器。优先编码器Ⅰ的真值表和代码已给出。

可将优先编码器Ⅰ的代码添加到本题答案中,并例化。

2.解题思路:

2.1首先把16位的数据数据输入分为 2 个8 位的数据输入。当有一个 83线编码器工作时,另外一个不工作。 控制这个的数据位为E1 (高电平启动83编码器 ), 当一个83编码器运行之后的EO 输出为 0 . 所以我们可以使用 E1(使能输入) EO(使能输出)来控制两个编码器的运行。

2.2EI EO 思路举例说明:

EI(最开始的输入) -> 编码器1 -> EO1 -> 编码器2 EI -> EO (最后的EO) 2.3然后是 15 位 到 8位 的83编码器 的输出,可以这样比喻, 当15位 到 8位的 83编码器使用 它的输出的3 位的数据直接 + 2'b1000 就行。 (自己想一想)

编码器1 (15-8位) 输出的3 位数据 B1

16-4 编码器输出 L[3:0];

wire[3:0] B1 ; //assign持续赋值 wire

B1 = 83编码器的输出 + 2'b1000/2'b0000;

= 83编码器的输出 + GS1 (是否使用 ,使用 1, 没有使用0)

B1[3] = GS1;

L[3] = B1[3] = GS1;

L[3] = GS1;

2.4 最后的16-4 编码器的输出结果是 两个编码器相 或。

3.解题遇到的问题

3.1 问题: main.v:53:error:B1['sd3]在encoder_164中不是有效的l值。 main.v:31::B1['sd3]在这里被声明为wire。 main.v:55:错误:B1['sd3]在encoder_164中不是有效的l值。 main.v:31::B1['sd3]在这里被声明为wire。

错误原因:数据类型定义错误 或者 赋值类型错误

解决方法: 在always 过程块中被赋值的变量必须是 reg (寄存器型),用 assign 连续赋值的对象 必须定义成 wire(线型);

4.解题代码

`timescale 1ns/1ns

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);

assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];

assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

//assign GS = EI&(| I);

endmodule

module encoder_164(

input [15:0] A ,

input EI ,

output wire [3:0] L ,

output wire GS ,

output wire EO

);

wire[2:0] A1;

wire[2:0] B1;

wire Gs1,Gs2;

wire EO1;

encoder_83 U1(

.EI (EO1),

.I (A[7:0]),

.Y (A1[2:0]),

.GS (Gs1),

.EO (EO)

);

encoder_83 S2(

.EI (EI),

.I (A[15:8]),

.Y (B1[2:0]),

.GS (Gs2),

.EO (EO1)

);

assign L[3] = Gs2;

assign L[2] = A1[2] | B1[2];

assign L[1] = A1[1] | B1[1];

assign L[0] = A1[0] | B1[0];

assign GS = Gs1 | Gs2;

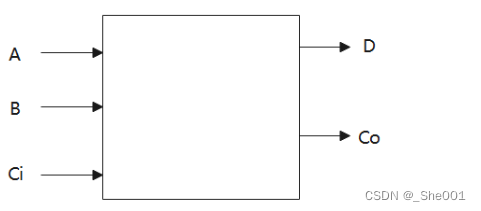

endmodule7.VL17 用3-8译码器实现全减器

1.题目:

请使用3-8译码器和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。

3-8译码器代码如下,可将参考代码添加并例化到本题答案中。

module decoder_38(

input E ,

input A0 ,

input A1 ,

input A2 ,

output reg Y0n ,

output reg Y1n ,

output reg Y2n ,

output reg Y3n ,

output reg Y4n ,

output reg Y5n ,

output reg Y6n ,

output reg Y7n

);

always @(*)begin

if(!E)begin

Y0n = 1'b1;

Y1n = 1'b1;

Y2n = 1'b1;

Y3n = 1'b1;

Y4n = 1'b1;

Y5n = 1'b1;

Y6n = 1'b1;

Y7n = 1'b1;

end

else begin

case({A2,A1,A0})

3'b000 : begin

Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b001 : begin

Y0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b010 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b011 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b100 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b101 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;

end

3'b110 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;

end

3'b111 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;

end

default: begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

endcase

end

end

endmodule2.解题代码

`timescale 1ns/1ns

module decoder_38(

input E ,

input A0 ,

input A1 ,

input A2 ,

output reg Y0n ,

output reg Y1n ,

output reg Y2n ,

output reg Y3n ,

output reg Y4n ,

output reg Y5n ,

output reg Y6n ,

output reg Y7n

);

always @(*)begin

if(!E)begin

Y0n = 1'b1;

Y1n = 1'b1;

Y2n = 1'b1;

Y3n = 1'b1;

Y4n = 1'b1;

Y5n = 1'b1;

Y6n = 1'b1;

Y7n = 1'b1;

end

else begin

case({A2,A1,A0})

3'b000 : begin

Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b001 : begin

Y0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b010 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b011 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b100 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b101 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;

end

3'b110 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;

end

3'b111 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;

end

default: begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

endcase

end

end

endmodule

module decoder1(

input A ,

input B ,

input Ci ,

output wire D ,

output wire Co

);

wire Y0n,Y1n,Y2n,Y3n,Y4n,Y5n,Y6n,Y7n;

decoder_38 decoder_1(

.E(1) ,

.A0(Ci) ,

.A1(A) ,

.A2(B) ,

.Y0n(Y0n) ,

.Y1n(Y1n) ,

.Y2n(Y2n) ,

.Y3n(Y3n) ,

.Y4n(Y4n) ,

.Y5n(Y5n) ,

.Y6n(Y6n) ,

.Y7n(Y7n)

);

assign D = ~(Y1n&Y2n&Y4n&Y7n);

assign Co = ~(Y1n&Y4n&Y5n&Y7n);

endmodule

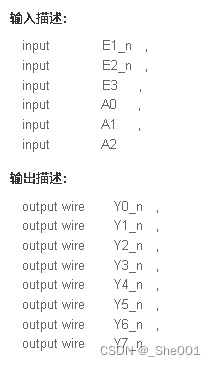

8.VL18 实现3-8译码器①

1.题目:

下表是74HC138译码器的功能表.

请用基础门电路实现该译码器电路,用Verilog将电路描述出来。基础门电路包括:非门、多输入与门、多输入或门。

2.解题代码

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire [7:0] Y;

wire EN;

//首先是公式 就是真值表转 公式 因为 38 译码器的输出 是低电平,没事我们两边加上一个 ~ 就和之前的列出公式差不多了, 只要列出 输出为0 的。

//列出输出的公式

//使用或门 第一个为输出的值 第二第三为 相或的参数

//第一个为使能输出, 标准的正常的使能为 E3=1 ,E2_n =0 , E1_n =0;

and(EN,E3 , ~E2_n, ~E1_n);

// 输出 0 的真值表的公式

and(Y[0],EN,~A0,~A1,~A2);

and(Y[1],EN,A0,~A1,~A2);

and (Y[2] , EN , ~A0,A1,~A2);

and (Y[3] , EN , A0,A1,~A2);

and (Y[4] , EN , ~A0,~A1,A2);

and (Y[5] , EN , A0,~A1,A2);

and (Y[6] , EN , ~A0,A1,A2);

and (Y[7] , EN , A0,A1,A2);

//非门 ,因为两边加了一个非门

not (Y0_n , Y[0]);

not (Y1_n , Y[1]);

not (Y2_n , Y[2]);

not (Y3_n , Y[3]);

not (Y4_n , Y[4]);

not (Y5_n , Y[5]);

not (Y6_n , Y[6]);

not (Y7_n , Y[7]);

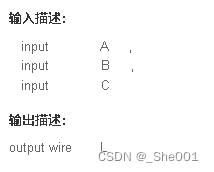

endmodule9.VL19 使用3-8译码器①实现逻辑函数

1.题目:

下表是74HC138译码器的功能表

②请使用3-8译码器①和必要的逻辑门实现函数L=(~A)·C+A·B

可在本题答案中添加并例化3-8译码器①代码,3-8译码器①代码如下:

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

2.解题代码

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire Y0_n ;

wire Y1_n ;

wire Y2_n ;

wire Y3_n ;

wire Y4_n ;

wire Y5_n ;

wire Y6_n ;

wire Y7_n ;

decoder_38 U0(

.E1_n (1'b0),

.E2_n (1'b0),

.E3 (1'b1),

.A0 (C),

.A1 (B),

.A2 (A),

.Y0_n (Y0_n),

.Y1_n (Y1_n),

.Y2_n (Y2_n),

.Y3_n (Y3_n),

.Y4_n (Y4_n),

.Y5_n (Y5_n),

.Y6_n (Y6_n),

.Y7_n (Y7_n)

);

assign L = ~(Y1_n & Y3_n & Y6_n & Y7_n);

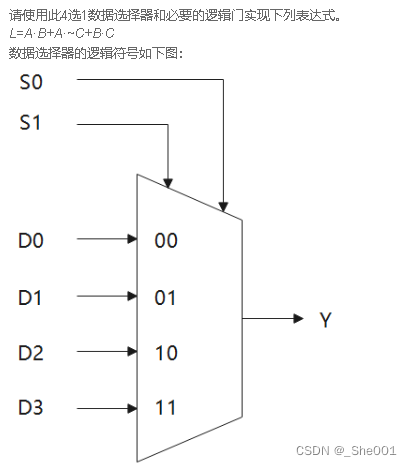

endmodule10.VL20 数据选择器实现逻辑电路

1.题目:

数据选择器代码如下,可在本题答案中添加并例化此数据选择器。

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

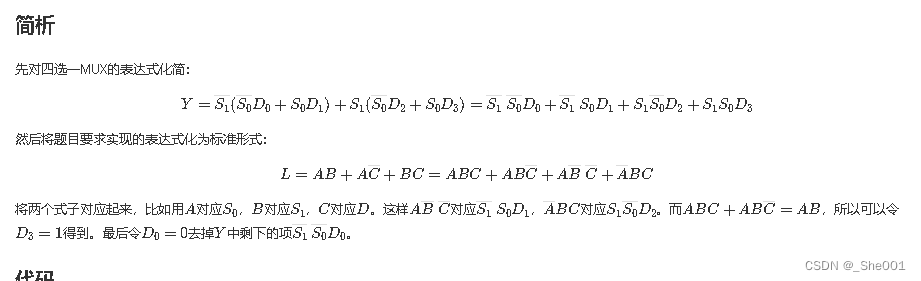

2.解题思路:

D1 = ~D2

D1 = C

D2 = ~C

3.解题代码

`timescale 1ns/1ns

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

module sel_exp(

input A ,

input B ,

input C ,

output wire L

);

data_sel c1(

.S0(A),

.S1(B),

.D0(0),

.D1(~C),

.D2(C),

.D3(1),

.Y(L) );

endmodule

489

489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?