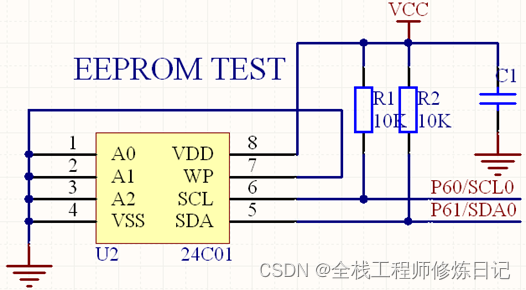

一.原理图

24C01的硬件连接图如下:

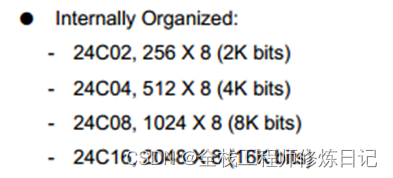

二.24C0x系列芯片规格

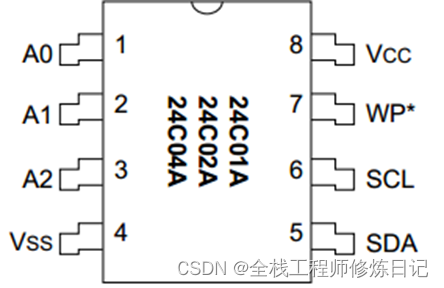

三.24C0x芯片结构

下面简述EEPROM内部存储结构。

3.1 内部存储结构

根据24C02芯片的Datasheet描述,其内部存储结构应该如下图所示。

其它容量的EEPROM内部结构依此类推。

3.2 地址

3.2.1 器件地址

EEPROM的封装图如下:

这个地方值得注意:引脚A0、A1和A2只用来定义器件地址,不能用来选择内部ROM单元地址。故此,无论外部引脚如何连接,都不影响内部ROM地址的选择。

3.2.2 存储单元地址

不同容量的EEPROM,其地址位数不同,具体的地址构成为:

| 序号 | 型号 | 地址位数 |

|---|---|---|

| 1 | 24C02 | 8 |

| 2 | 24C04 | 9 |

| 3 | 24C08 | 10 |

| 4 | 24C16 | 11 |

存储单元地址发送方法如下图所示。图中第一个字节包含的存储单元地址位可理解为页地址位。

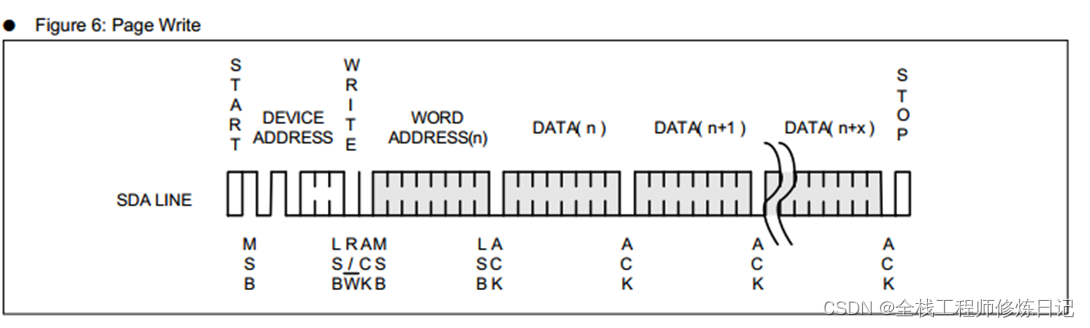

四.页写

页写时序如下图:

写到页边界时,要继续写下一页或其它页,必须产生一个停止信号,然后再产生一个开始信号,接着由主机传送目标页的地址,以开始在目标页的写操作。

页边界的停止信号不能缺少,否则会出错。

365

365

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?