一、简单应用

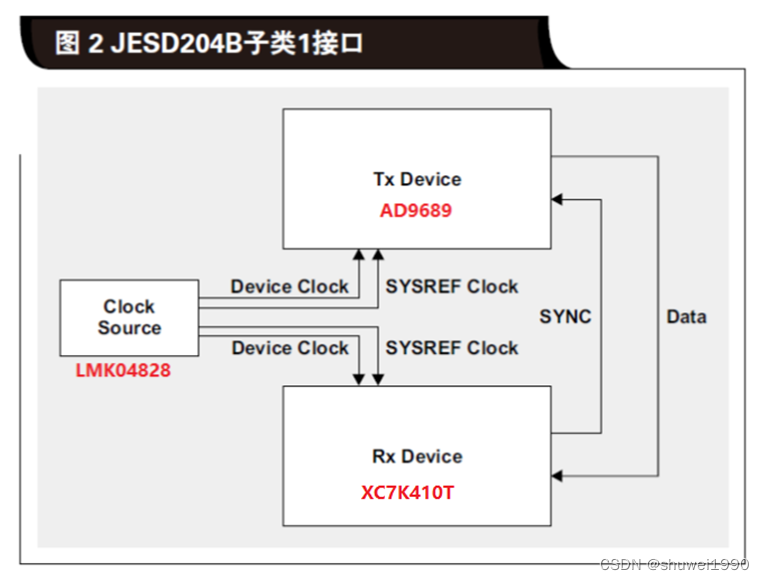

原来的项目只用了一块ADC芯片,8条Lane,硬件配置如下:

- 时钟芯片:LMK04828

- ADC芯片:AD9689

- FPGA芯片:XC7K410T-FFG900-2

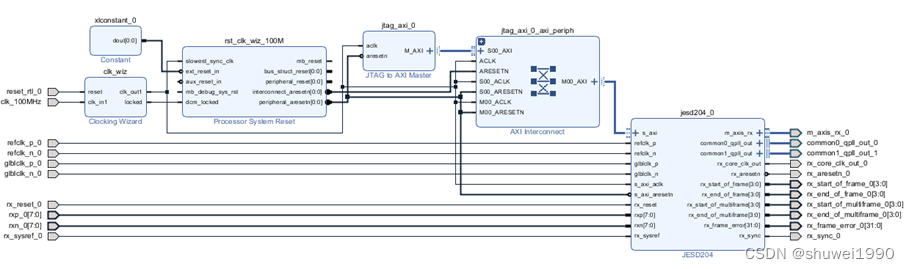

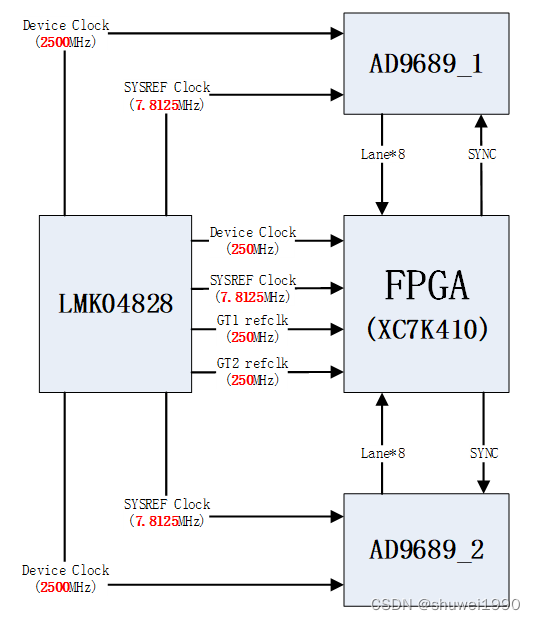

我使用了Block Design调用JESD204B IP:下图中的上面一部分是调用了JTAG to AXI Master用于调试,其实也可以不要,那就只需要调用JESD204B IP,非常简单。

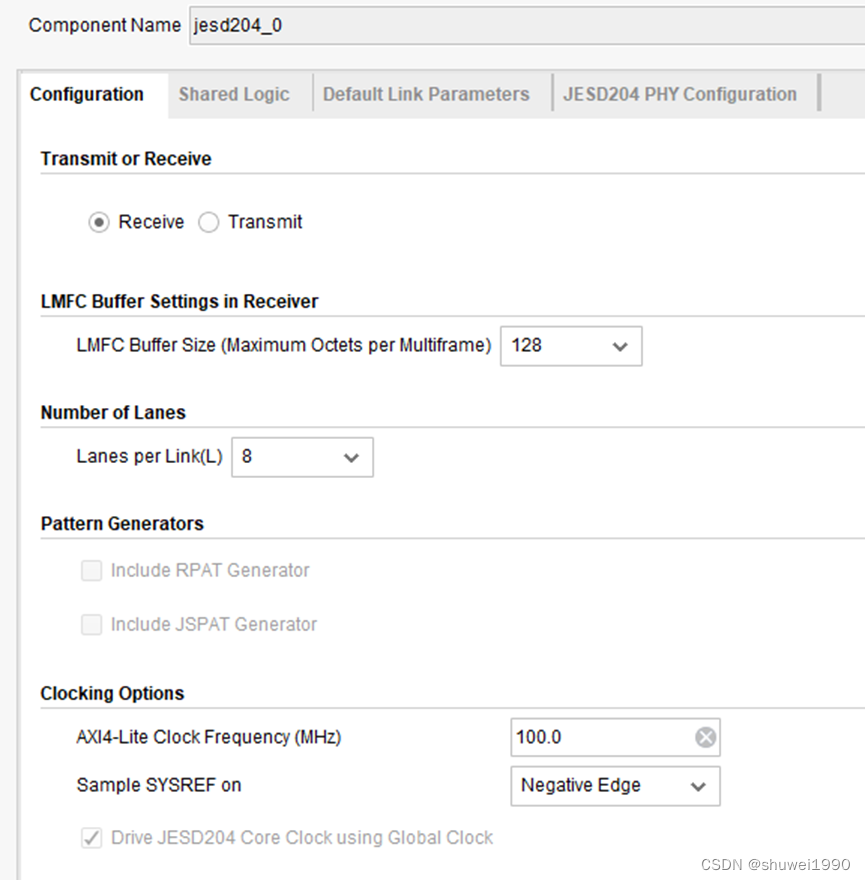

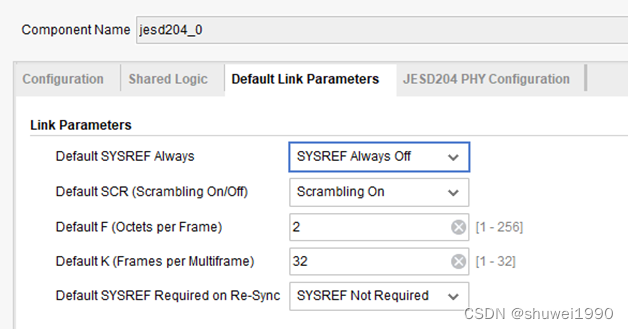

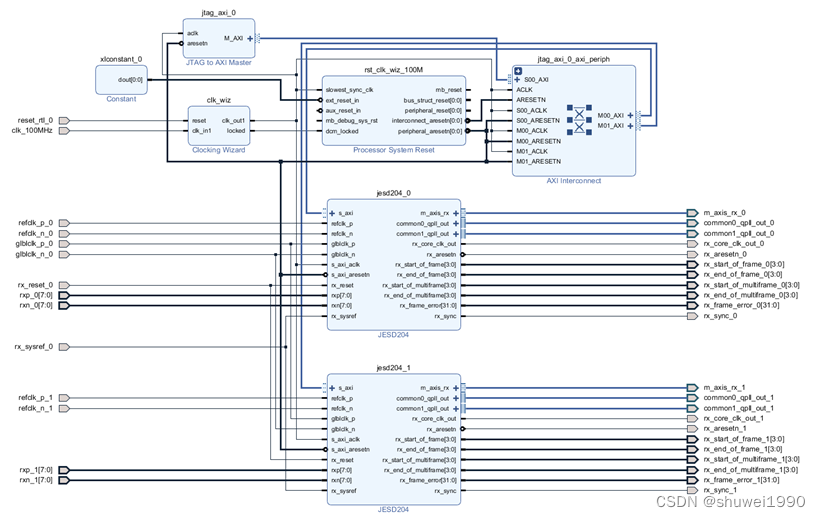

JESD204B IP的配置选项比较少,很简单,如下面几张图所示。

二、高阶应用

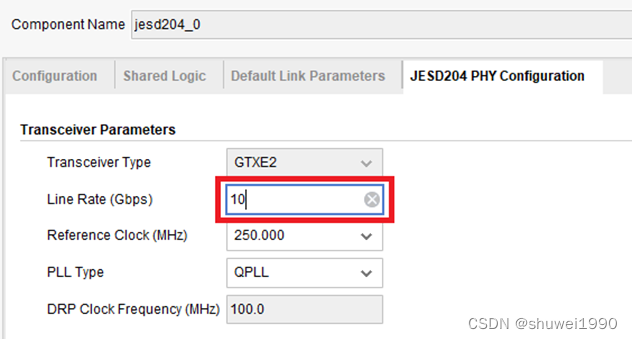

现在的项目要用到两块ADC芯片,各8条Lane,硬件配置跟以前一样。结构图如下所示:

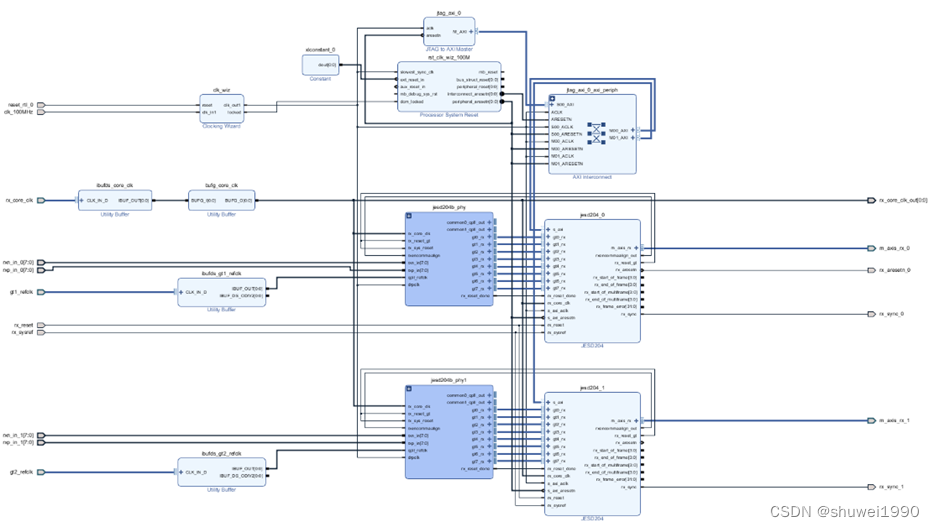

对于FPGA来说,GT参考时钟有两组,但Device和SYSREF时钟是共用的。基于以前的设计,很自然的想法就是在Block Design里直接调用两个JESD204B IP,如下图所示:

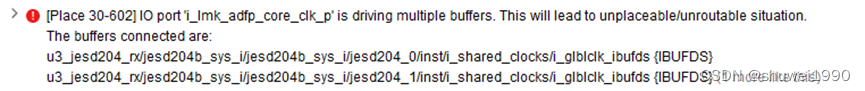

点击Validate Design,并没有报错。综合也没有报错,但实现报错了。

点击Validate Design,并没有报错。综合也没有报错,但实现报错了。

报错原因是:硬件设计上共用了Device Clock(图中的glblclk),而这个时钟进来后驱动了两个IBUFDS,因而报错。

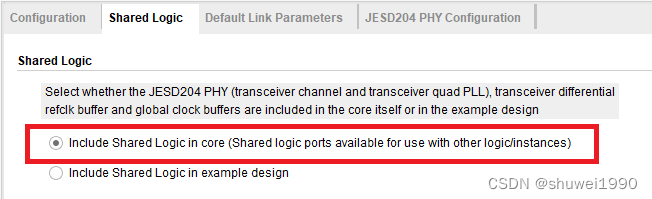

既然一组Device Clock不能直接连到两个JESD204B IP的glblclk,那么就不能直接照搬原来的设计了。必须改变下JESD204B IP的设置,在Shared Logic里勾选in example design,只有这样才能共用输入时钟。

在Shared Logic里勾选in example design,随之而来的麻烦就是还需要另外调用JESD204B PHY IP,然后还需要连一堆的线。修改后的Block Design如下图,综合和实现也都没有报错。

文章讲述了在FPGA项目中使用JESD204B接口与ADC芯片连接时的时钟配置问题。初始设计仅涉及一块ADC,而新项目增加至两块,导致DeviceClock共用引发错误。解决方案是通过在SharedLogic中启用inexampledesign,并引入JESD204BPHYIP来正确处理共享时钟,从而避免实现阶段的错误。

文章讲述了在FPGA项目中使用JESD204B接口与ADC芯片连接时的时钟配置问题。初始设计仅涉及一块ADC,而新项目增加至两块,导致DeviceClock共用引发错误。解决方案是通过在SharedLogic中启用inexampledesign,并引入JESD204BPHYIP来正确处理共享时钟,从而避免实现阶段的错误。

841

841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?