目录

一、介绍下项目历史情况

先说下我们的硬件配置:

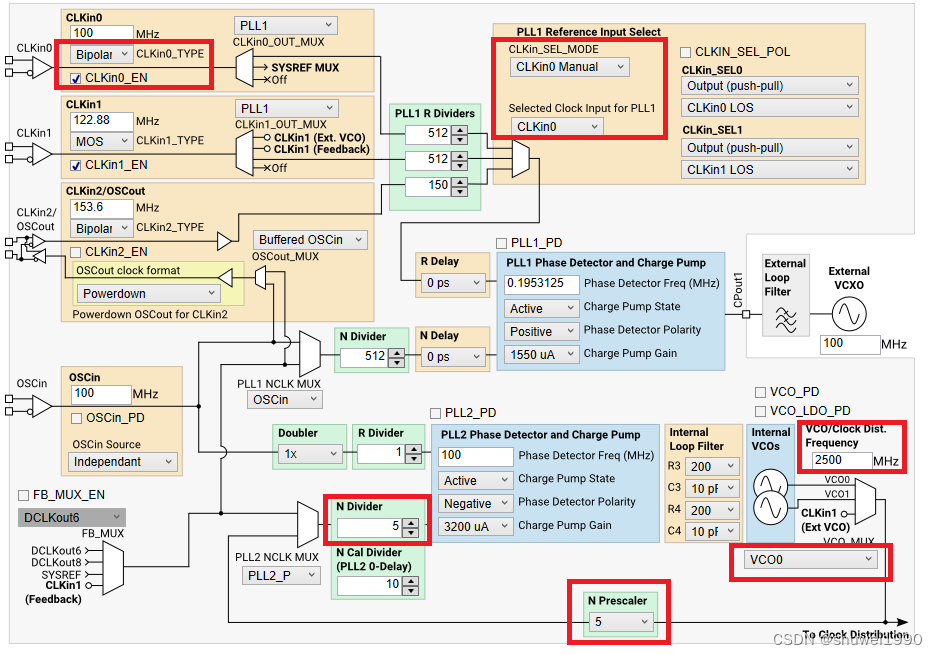

- 时钟芯片:LMK04828

- ADC芯片:AD9689

- FPGA芯片:XC7K410T-FFG900-2

如上图所示,使用JESD204B的子类1接口模式。原来的需求是单通道14bit,采样率为2.4Gsps。相关参数设置如下:

| 序号 | 项目 | 代号 | 参数 | 说明 |

| 1 | ADC与FPGA连接的SERDES通道数 | L | 8 | 用了8条lane |

| 2 | ADC转换器个数 | M | 1 | 只用了单通道 |

| 3 | ADC每帧包含8位字节数 | F | 2 | 每帧包含16bit |

| 4 | ADC每个多帧包含的连续帧数 | K | 32 | 每个多帧包含32帧 |

| 5 | ADC采样位数 | N | 14 | 项目要求分辨率为14bit |

| 6 | JESD204B字大小(4个半字节) | N` | 16 | 扩展到16bit |

二、为什么要用fs×4模式?

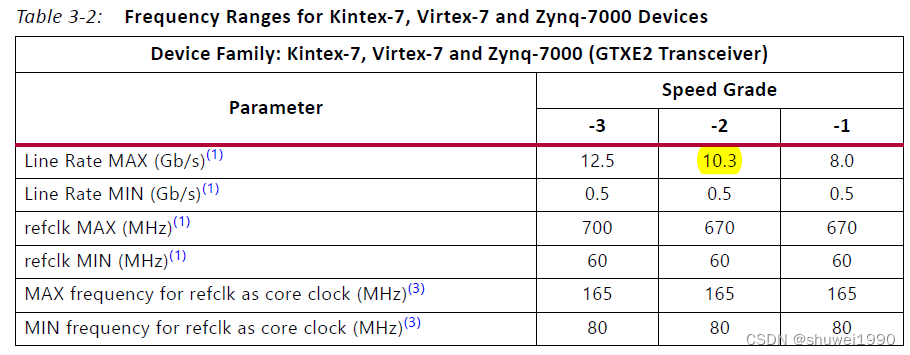

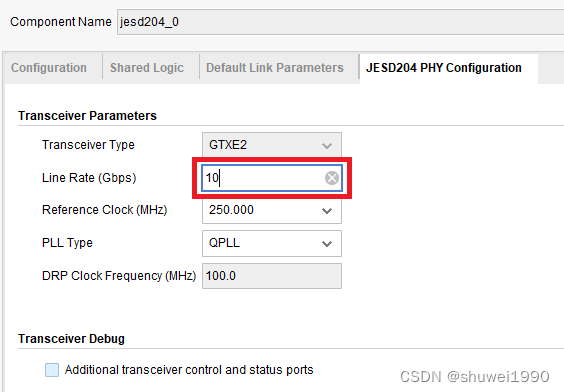

在原来需求的基础上,要将单通道改成双通道。那么线速率就会变为原来的2倍,也就是12Gbps。但是我们这款FPGA芯片最高只支持10.3Gbps,如下图PG066中所述,那从单通道直接改为双通道就不行了。

不过AD9689提供了fs×4模式,芯片手册中有如下描述:fS × 4 mode adds a separate packing mode to a JESD204B transmitter/receiver to set the serial lane rate at four times the sample rate (fS).

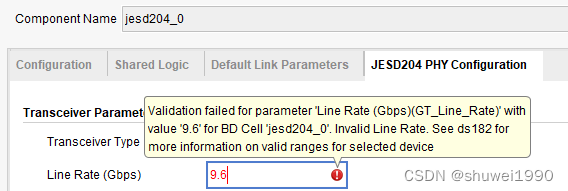

如果采样率还是2.4Gsps,那么线速率就是2.4G*4=9.6Gbps<10.3 Gbps,FPGA应该能支持了。不过有一点需要注意:fs×4模式只支持12bit,而原来是14bit,ADC的分辨率降低了。

三、为什么要将采样率改成2.5Gsps?

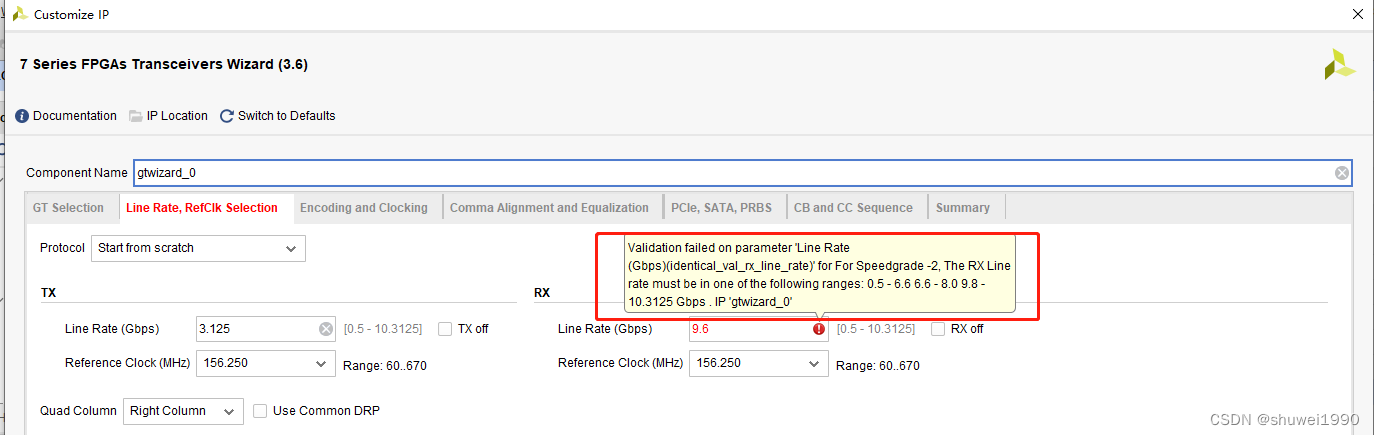

虽然9.6Gbps的线速率确实没有超过最大线速率的要求,但是很不幸,这款FPGA芯片实在是太“傲娇”了,还是不支持,如下图所示:

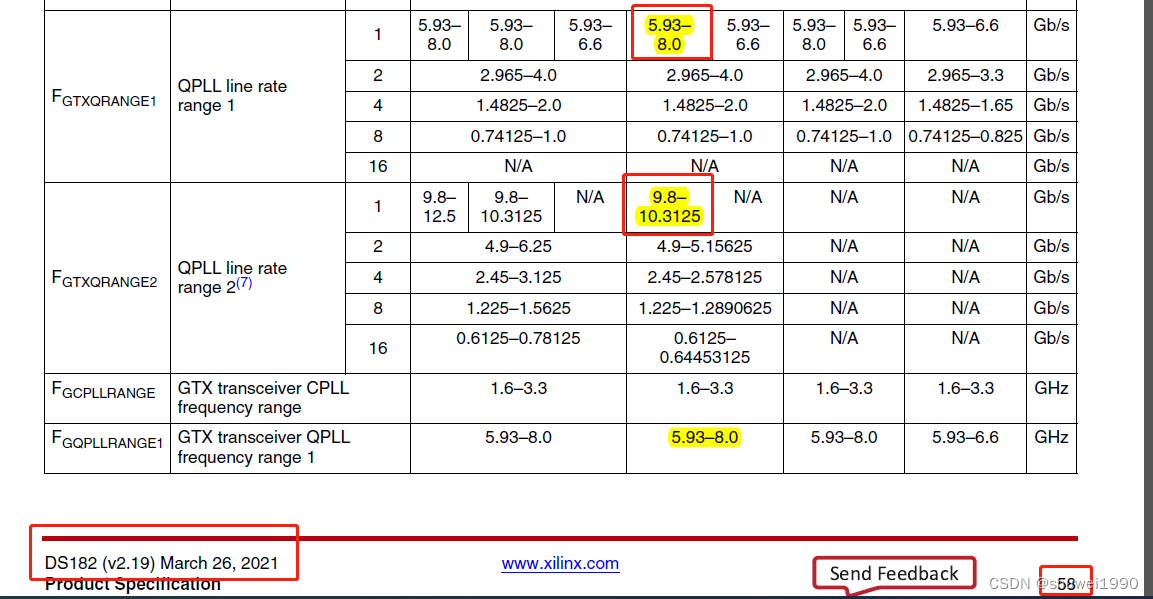

查看DS182,要找很久,才能找到如下描述:

其实,JESD204 IP的底层调用的还是transceiver,所以我们可以直接打开transceiver IP,如下图所示。这里的提示就很清楚了,只支持0.5-8.0和9.8-10.3125之间的线速率。

既然9.6Gbps还是不支持,就近的选择就是10Gbps了,那么对应的采样率就是2.5Gsps。

四、时钟芯片参数如何设置?

时钟芯片选择clkin0输入,两级PLL结构。VCO0是2500M,DCLKOUT0是250M,SYSREF分频比320频率7.8125MHz。

五、AD芯片参数如何设置?

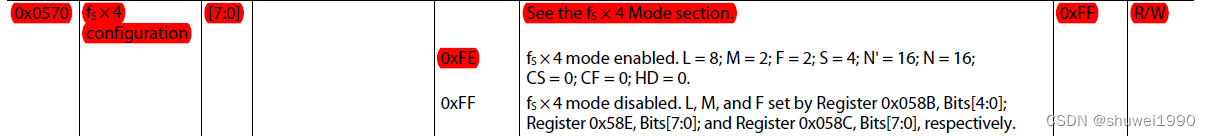

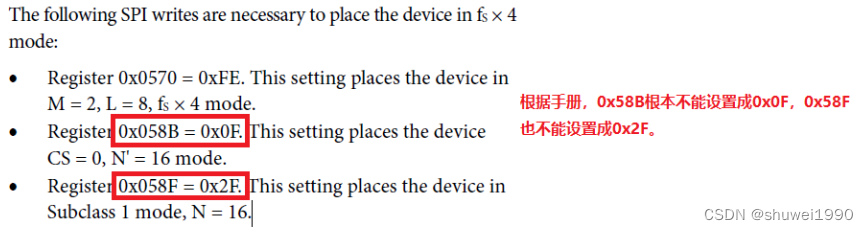

AD9689配置较为简单,主要是要将0x570配置为0xFE,即使能fs×4模式;

LMF这几个参数按要求进行配置,不配置也可以,因为使能fs×4模式之后会自动配置这些参数。

另外,手册上存在一些描述性错误,如下图所示,按以下配置即可0x58B=0x87, 0x58F=0x0F。

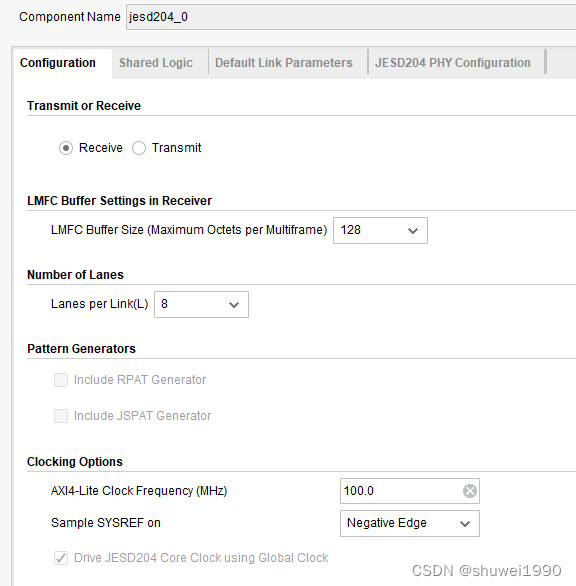

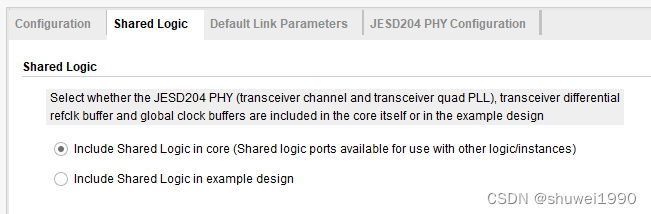

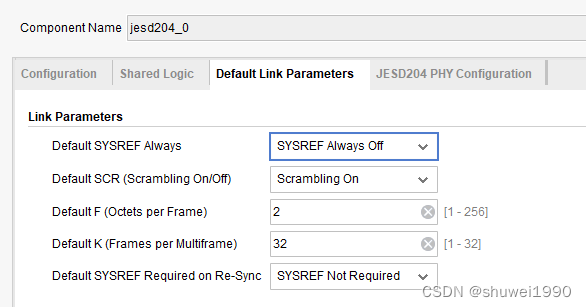

六、FPGA工程里JESD204 IP如何设置?

Vivado里JESD204B IP的配置选项比较少,很简单。

七、传输层如何解包?

这部分比较麻烦,记录几个要点:

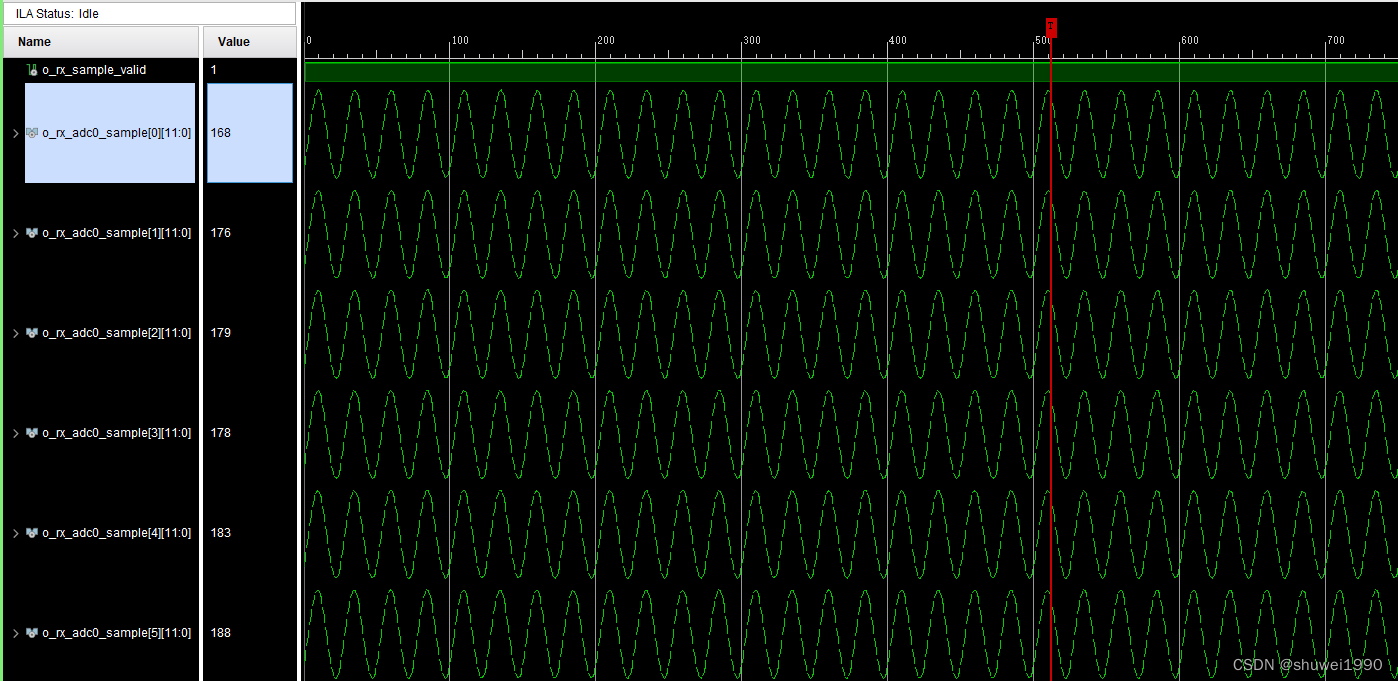

- 每64bit发送5个采样点,每个采样点12bit,最后4bit补0;

- ADC0使用Lane0-3,ADC1使用Lane4-7;

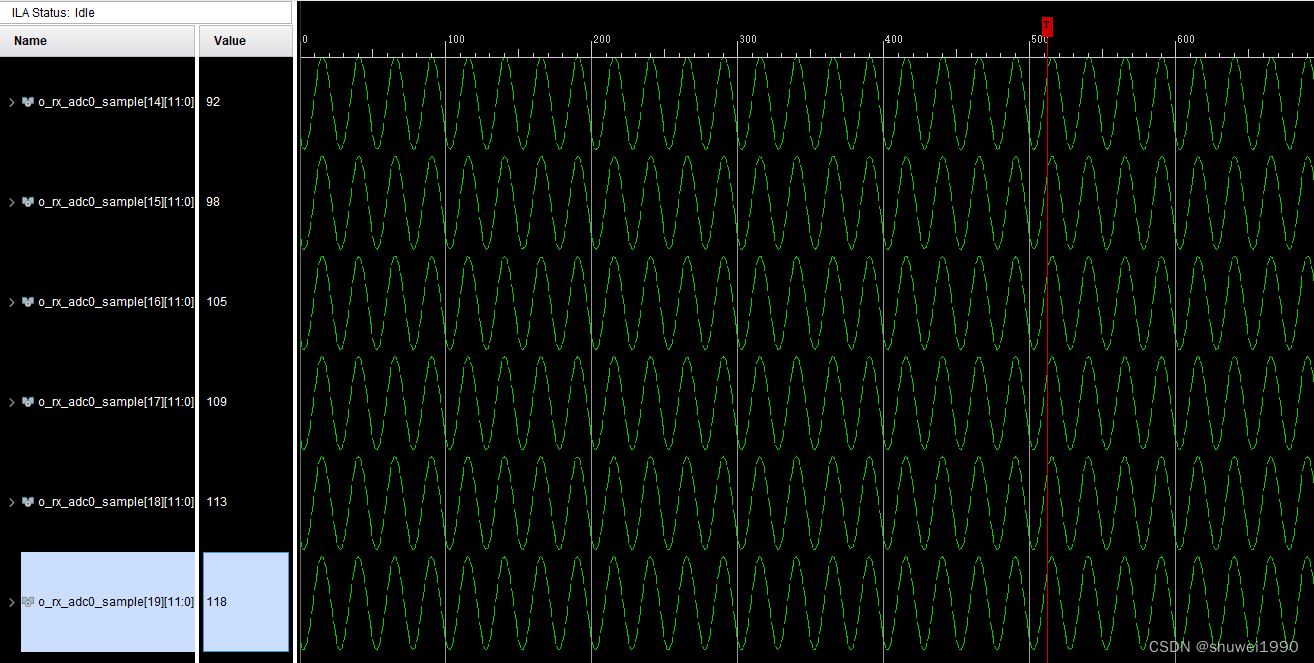

- 原来256bit解析出16个采样点,现在需要解析出20个采样点;

- 解析格式如下,这里只列出了ADC0的解析数据格式:

| adc0_data 0_0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 15 | 14 | 13 | 12 |

| adc0_data 0_1 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 31 | 30 | 29 | 28 |

| adc0_data 1_0 | 11 | 10 | 9 | 8 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

| adc0_data 1_1 | 27 | 26 | 25 | 24 | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 |

| adc0_data 2_0 | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 71 | 70 | 69 | 68 |

| adc0_data 2_1 | 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 87 | 86 | 85 | 84 |

| adc0_data 3_0 | 67 | 66 | 65 | 64 | 79 | 78 | 77 | 76 | 75 | 74 | 73 | 72 |

| adc0_data 3_1 | 83 | 82 | 81 | 80 | 95 | 94 | 93 | 92 | 91 | 90 | 89 | 88 |

| adc0_data 4_0 | 103 | 102 | 101 | 100 | 99 | 98 | 97 | 96 | 111 | 110 | 109 | 108 |

| adc0_data 4_1 | 119 | 118 | 117 | 116 | 115 | 114 | 113 | 112 | 127 | 126 | 125 | 124 |

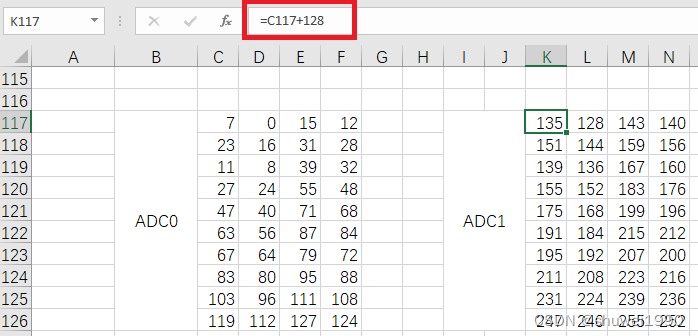

- ADC1的解析数据格式只要在ADC0的解析数据格式里加上128bit即可,可以在excel表格里操作好,然后再复制粘贴到Verilog代码里:

测试结果如下图所示:

八、测试中遇到的问题

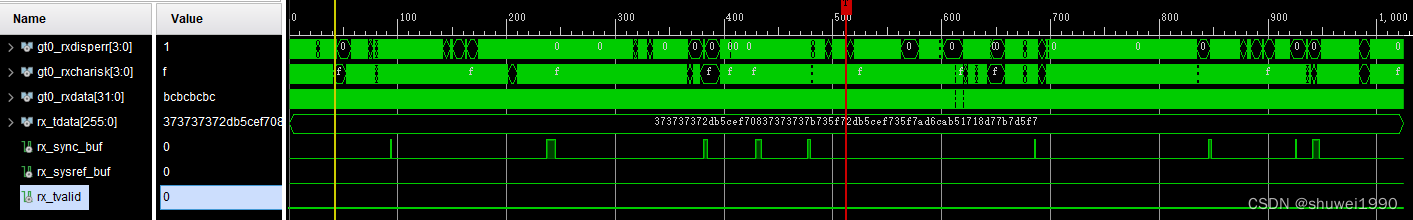

用JTAG抓取波形,查看sync信号会间隔性地被拉低,如下图:

- 读取AD9689芯片的0x56F寄存器,显示PLL已锁定;

- 将FPGA芯片改为-3等级,然后直接将单通道改为双通道跑12Gbps,测试发现可以正常工作,说明硬件能够支持跑10Gbps;

- 再次检查参数配置,确认没有问题;

- 给JESD204的复位增加VIO控制,复位后发现可以正常工作,说明在AD芯片配置完成后,还需要给FPGA JESD204复位一次;

在时钟芯片和ADC芯片配置完成后,需要将JESD204 IP再次复位,以保证建链成功!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?