衬底噪声的影响

注入衬底的噪声电流使衬底电势产生波动,产生流入到地线接触或者是通过N阱流入到电源线接触的噪声电流。衬底噪声电流通过晶体管扩散区的反偏结电容或者是背栅效应耦合到MOS晶体管,噪声电流也可能耦合到无源器件上。由于模拟电路器件所在的衬底或者是N阱被偏置到模拟Gnd或者Vdd上,因此,衬底噪声抖动会通过衬底接触或者是N阱接触被这些所谓的干净电源网络吸收。注入的衬底噪声会引起系统信号的失真或电路功能的失败。

1)衬底噪声对器件级影响

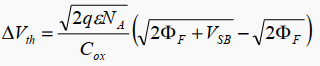

对于CMOS器件,背栅效应是主要的衬底噪声接收机制。MOS晶体管的阈值电压随着源-背栅电压(VSB)变化而变化,变化量是VSB的函数:

其中,△Vth为阈值电压的变化量,ε为Si的介电常数,Cox为单位面积的氧化层电容,ФF 为费米势,2ФF为MOS管沟道形成反型层时所需的表面势大小。衬底噪声传播到MOS晶体管的背栅,使得衬底电势发生变化,从而影响晶体管的阈值电压。阈值电压的波动可能会导致器件脱离正常的工作状态,从而导致整个电路的功能受到损失。

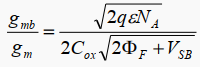

衬底噪声引起的衬底电势变化还会使MOS管漏端电流发生变化,这种影响可以通过器件的一个小信号线性模型参数gmb来说明。当 MOS晶体管的栅端和源端短接在一起时,有公式:

其中,gm表示器件小信号跨导,它把MOS晶体管的漏端电流与VSB联系起来。对于典型工艺,gmb/gm的值一般为0.1~0.3,因此,寄生的体-漏增益比栅-漏增益大约低14-20dB。

体效应使得 MOS 晶体管极易受到衬底噪声的影响。 一些器件工作在较高频率时(一般在 MHz 以上),一般以容性方式拾取衬底噪声,而体效应在低频时尤为显著。

2)衬底噪声对电路级影响

衬底噪声对电路级的影响取决于多方面因素,如电路类型、拓扑结构版图布局、电源网络偏置和封装类型等。衬底噪声可导致运放性能的衰减,引起输出波形失真,相位发生移动; 衬底噪声通过低频低调制电压时非理想的地线和高频高调制电压时片上电感使压控振荡器的振荡频率发生变化;衬底噪声对低噪声放大器的影响主要有两种机制:调制输入信号和由失配引起的到差分输出端的直接耦合。

3)衬底噪声对系统级的影响

对于系统级而言,衬底耦合噪声是限制如PLL、数字模拟转化器模块、射频接收模块等敏感电路与DSP、RAM等大规模数字模块集成在一起的主要因素。对于动态范围比较高的系统,更容易受到衬底耦合噪声的影响。因此,要降低衬底噪声的影响,就要在设计上下很大的功夫。

4)衬底噪声对数字电路的影响

数字模块在状态转换过程中向衬底注入的噪声电流不仅对敏感的模拟/射频电路产生影响,数字模块本身也不能幸免。逻辑门电路在开关瞬间产生衬底噪声然后通过离子碰撞和电容耦合的方式进入衬底,然后被有源器件通过电容耦合和体效应拾取。

衬底耦合噪声可以从多个方面影响数字电路,从而导致数字电路的失败。衬底耦合噪声导致数字电路中数据通路的延时可能会增加,从而可能会超过预定的时钟周期,这种现象称为延时效应;逻辑门的噪声容限必须足够高以确保门的任意节点的噪声不会改变门以及其后级逻辑电路状态,而衬底耦合噪声可能会使逻辑电路的噪声容限降低,从而导致数字电路逻辑功能的失败;此外,衬底耦合噪声还会导致数字电路产生额外的毛刺功耗。

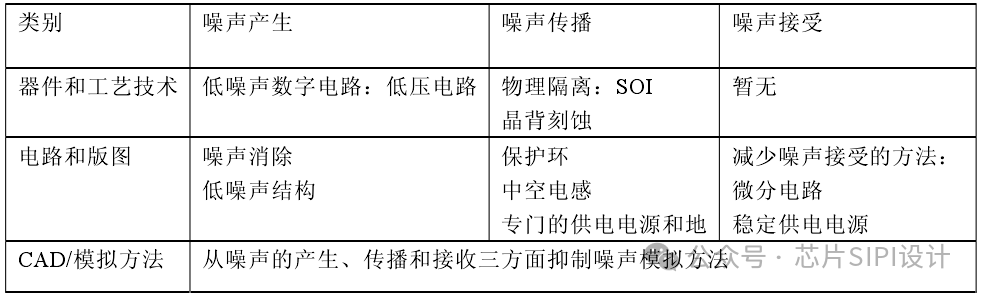

3 衬底耦合噪声的抑制

对于衬底耦合噪声的抑制, 与它的耦合是相对应的,也是从三个方面入手: (1)减小噪声源的噪声注入; (2)改变衬底噪声的传播路径; (3)提高噪声敏感电路对噪声的抗干扰能力,因此减少噪声源和噪声接受端之间衬底噪声耦合的技术基本上可分为三类:

a) 减小噪声源的噪声产生量。

b) 抑制从源端到接收端的噪声传播。

c) 提高芯片中噪声接收端或噪声敏感部分对于噪声的抗干扰能力。

1)削弱噪声源

衬底耦合噪声主要由数字电路和高频射频电路产生。在数模混合信号系统中,80%的衬底噪声由数字标准单元在状态发生转变时产生,并主要由电源线/地线网络进行耦合。因此, 为了减小衬底噪声的产生,可以从这两个方面着手。

当数字电路状态发生转变时,电源网络提供的电流不能保持不变,就会导致数字开关噪声的产生。因此,如果电源电流保持恒定,衬底噪声电流就会削弱很多。当电路状态发生转换时,由于恒流源偏置的作用,电源网络上的电流维持不变。但是,当存在大的电容与电流源器件并联时,电源网络上仍然存在电流波动。

对于电源网络噪声除了用以上描述的低噪声逻辑结构来减小之外,还可以使用以下三种方式:(1)模拟/射频电路和数字电路使用分开的电源网络,这样可以减小敏感电路部分和数字部分共同的阻抗;(2)使用多个模拟模块和数字模块地线管脚,或者使用低寄生电感的封装;(3)使用片上去耦电容,提高相对较高的时间常数来阻止振荡,在低频时,它们能有效地降低电源线耦合噪声,但是去耦电容所占用的芯片面积较大,一般情况下要相对于芯片面积进行折衷。

2)改变衬底耦合噪声传播路径

衬底噪声造成的衬底电势的波动引发通过衬底向附近地线接触流动的电流(N阱中向电源线接触流动)。如果到达敏感区域的噪声大大减弱,那么噪声对敏感电路的干扰能够有效的降低,因此,改变衬底噪声的传播路径就是根据这一原理来减弱噪声的影响,具体有两种实施手段。

第一种方式是引导噪声电流到地。在数模混合电路设计过程中,应该在噪声源和噪声敏感电路周围提供足够多衬底地线接触;由于PMOS晶体管作在 N阱中,因此应该提供足够的 N 阱接触。因此,噪声电流在达到敏感电路之前就被地线接触吸收,同时它们还能提供低阻抗的地线网络。

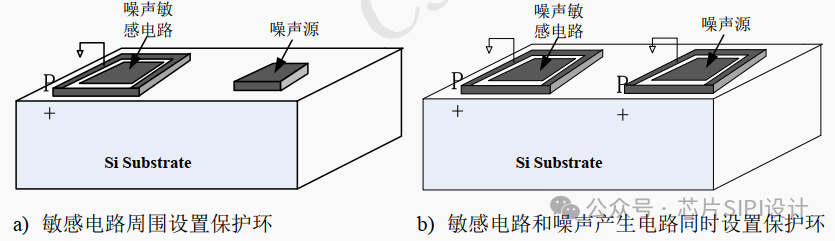

第二种方式是采用隔离结构将噪声源和噪声敏感电路隔离开。由于轻掺杂衬底本身就有隔离噪声的作用,因此,最简单的隔离方法就是改变噪声源和噪声敏感电路的物理布局来达到降低噪声的效果。典型的隔离结构有保护环、深沟道、 SOI 型衬底、深 N 阱等。保护环可以采用单环结构,只包围在敏感电路或者是衬底噪声产生电路周围,也可以是双环结构,同时包围在敏感电路和衬底噪声产生电路周围,如下图。

3)提高噪声敏感电路的免疫能力

减小衬底耦合噪声对模拟电路的影响也可以从模拟电路本身出发。提高模拟电路对衬底噪声的抗干扰能力主要有两种方式,一是采用全差分电路,衬底噪声通过衬底和电源网络以共模信号的形式到达差分电路的输出端,由于差分结构能够很好的抑制共模噪声,因此它能有效的降低衬底噪声对电路的影响。在使用差分结构时需要注意的是,差分电路与噪声源不能靠的太近,以免不对衬的噪声耦合到差分输入中,使电路的性能降低的更多。 二是采用窄带信号电路,与宽带电路相比,窄带电路能更好的抑制衬底噪声,尤其是数字电路工作频率在敏感电路带宽之内时,影响更加严重。如果可能,在电路设计中,输入信号幅度应尽可能的高,这样可以提高信噪比。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?