当今高速输入/输出(I/O)总线的数据速率不断提高,使得保持传输通道信号质量变得更具挑战性,在过去的十年中,为了满足现代网络应用和大容量存储对更多I/O带宽不断增长的需求,电气互连的数据速率经历了急剧增长——从1Gbps到25Gbps甚至更高。

SerDes是一种高速串行数据链路,用于IC中串行化并行数据并以更快的速度传输数据。在芯片之间提供可扩展的点对点串行连接,同时在软件层保持与传统PCI的兼容性,虽然这对设计人员来说是个利好,但它也带来了许多挑战,这使得信号完整性分析和符合性测试对确保高信号质量至关重要。

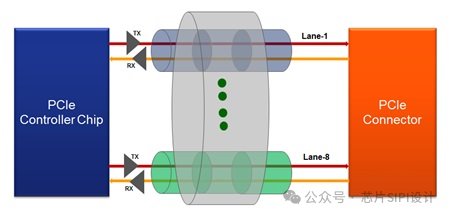

第三代PCIe标准PCI Express Gen3(以下简称PCIe Gen3)规定了高速差分I/O互连,运行速度为8.0 Gbps。它被广泛应用于计算机和服务器。下图显示了典型的PCIe Gen3链路,一般来说,通道要么短而直接,驱动器和接收器之间只有几英寸的互连,要么长而复杂。PCIe 3.0通道可以由1到32个通道组成,多种宽度(x1、x4、x8、x12、x16和x32,其中x表示通道)的连接器由PCIe标准定义。

这里的挑战是使用高速8Gbps串行链路的PCIe可能会受到大量SI现象的影响,这些现象可能包括串扰、阻抗不连续导致反射导致抖动、符号间干扰(ISI)以及由于传输线不平衡导致的模式转换——所有这些都可能导致大型系统中EMI的风险增大。

为了更好的解决这一挑战,需要对PCIe接口进行充分的通道仿真来识别,进行仿真以确保满足接口规范,包括眼图特性,并且误码率(BER)小于指定的最大值。

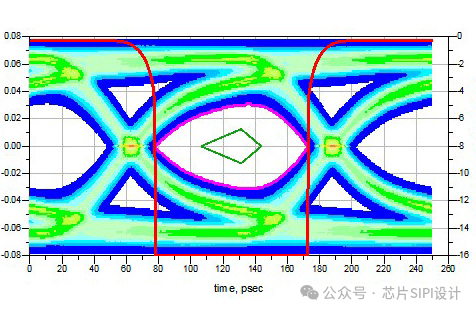

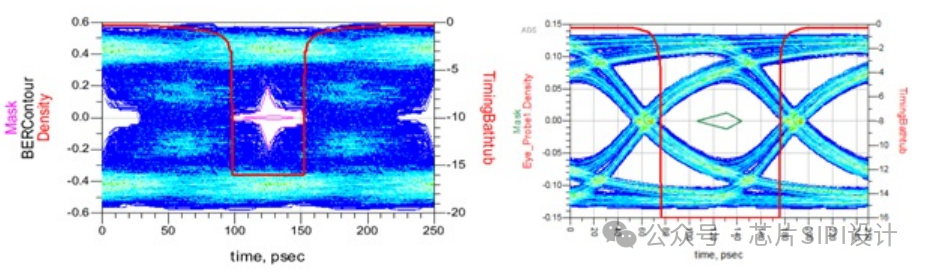

通常,利用IBIS-AMI发送端和接收端模型进行时域瞬态仿真,可以结合有损信道参数生成接收端的眼图,然后根据PCIe 3.0要求将结果与接收到的眼图模板进行比较,如果仿真眼图的振幅和抖动在睁眼规范内,则优于规范通常达到10^12-10^17的误码率,该仿真用于SI分析和符合性测试,以优化PCIe Gen3通道性能以达到PCI-SIG规范。

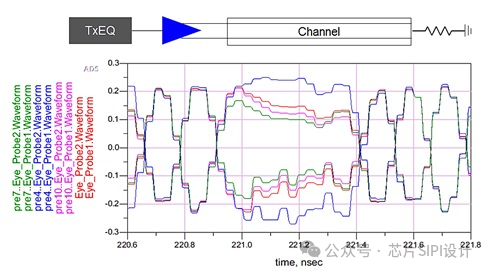

后面跟讲通过瞬态仿真来分析接口性能,其长度由信道损耗量和反射强度决定,PCIe仿真以8Gbps(UI=125ps)运行,在发射器(Tx)和(Rx)上使用IBIS-AMI模型,包括Tx的抖动,通道长度为6in,同时仿真包含决策反馈均衡器(DFE)和前馈均衡器(FFE)。

在串行通信系统中,时钟与传输的数据一起嵌入,时钟数据恢复(CDR)电路用于恢复接收端的时钟,锁存正确的数据在很大程度上取决于数据和时钟之间的对齐。抖动对误码率有重要影响,可分为随机抖动(Random Jitter,RJ)和确定性抖动(Deterministic Jitter,DJ)。为了仿真准确的误码率估计,这两种抖动元素也都包含在仿真中。

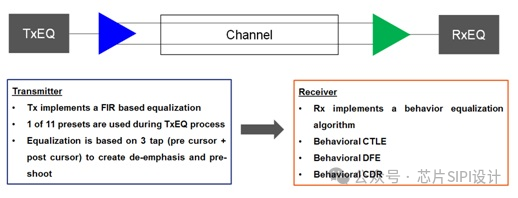

PCIe 3.0规范包括在发送端和/或接收端运行均衡的规定,这样做是为了减轻ISI的影响,从而最小化误码率。在均衡中,信号通过一个频率响应等于信道逆频率响应的滤波器,在较高的频率上,采用高增益来对抗信号衰减,换句话说,均衡是一个自适应过滤器,其系数取决于物理通道(如下图)。

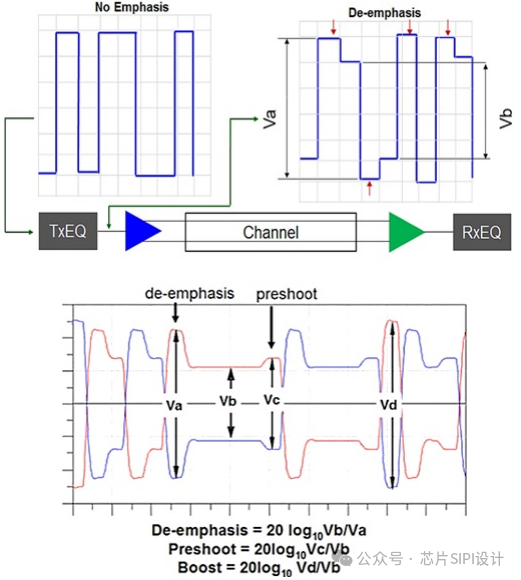

PCIe使用传输去加重来补偿高频信道损失,去加重后的波形是根据电压电平Va(去加重)和Vb(稳定高电平)来定义的,下图显示了当二进制输入流应用于3-tap FIR滤波器时产生的输出信号,在输入比特流极性反转之前和之后,输出的值是不同的。

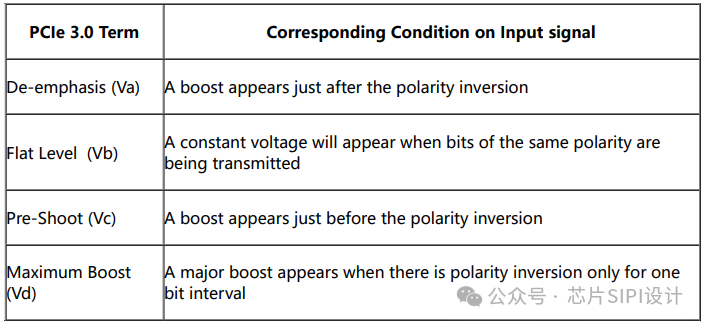

与上述行为波形相对应,PCIe 3.0规范定义了下表所示的新术语,电压Va,Vb,Vc和Vd分别对应于pre-emphasis、flat level、pre-shoot和最大增益。

为了进行SI分析,首先使用对PCIe连接器、9通道数据总线和封装进行仿真模型提取s参数数据;根据这些数据,从SI的角度分析包括:阻抗匹配、反射、衰减、阻抗失配、传播延迟、串扰和连接器。

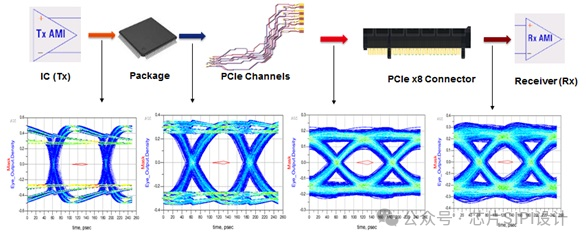

接下来,进行通路时域性能仿真,并以8Gbps的比特率生成伪随机比特序列(PRBS)。全链路仿真结果如下图所示。

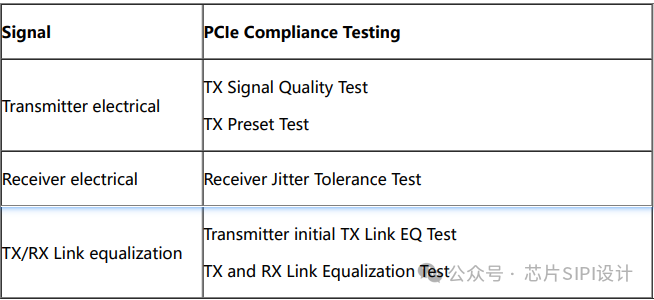

一致性测试是确保产品可互操作的必要条件,它验证PCIe通道是否符合PCIe规范,下表列出了不同的符合性测试参数。

首先来看Tx的SI性能,为了充分表征一个PCIe发射器,单位间隔(UI)时间、电压、眼图、抖动、空闲时间和通道skew是基于PCI-SIG规范测量的。大多数规格要求连续测量超过250个连续的UI。为了精确测量,应使用从发射机的Tx输出到其输入的直接连接,确保最低的噪声测量。下图图显示了发射端传输bit上的眼动和抖动测量。

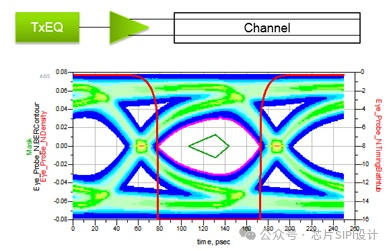

接下来是接收端均衡的电气性能测试,接收机必须测试其灵敏度和抗抖动能力。测试方法是为设备的Rx输入提供激励,并通过Tx引脚观测器件的响应,测量的眼睛与模板配合使用,如下图所示;

当不适用任何均衡时,眼睛是闭着的,在应用Rx均衡后,眼睛是打开的且符合PCIe规范。均衡背后的思想是使用其他位的电压电平来校正当前位的电压电平,由于信道频率相关损失的ISI,接收信号的眼睛完全关闭,时钟和数据无法从严重失真的信号中恢复,经过决策反馈均衡(Decision Feedback Equalization,DFE)均衡器后,均衡信号的眼被打开,数据中心的垂直眼打开在368 mV左右,这个值足够大,判决电路可以在可接受的误码率下恢复该数字数据。

PCIe 3.0规范规定了10个preset的pattern模式。一旦进入compliance模式,100MHz时钟可用于循环通过各种模式设置来执行抖动,电压和定时测量。符合性测试确保被测设备(DUT)能够生成所有presets和equalization电平,以满足规范要求。下图显示了所有preset值的波形。

本文通过上述的评估方法,可以确保PCIe Gen3串行通道的高信号质量传输,满足协议规范。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?