bar 地址转换在xilinx 官方文档 PG194的第四章 Designing with the Core有详细描述

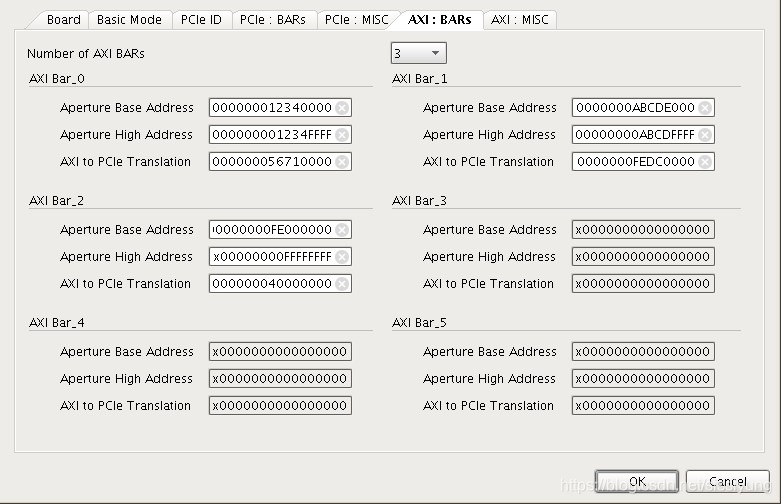

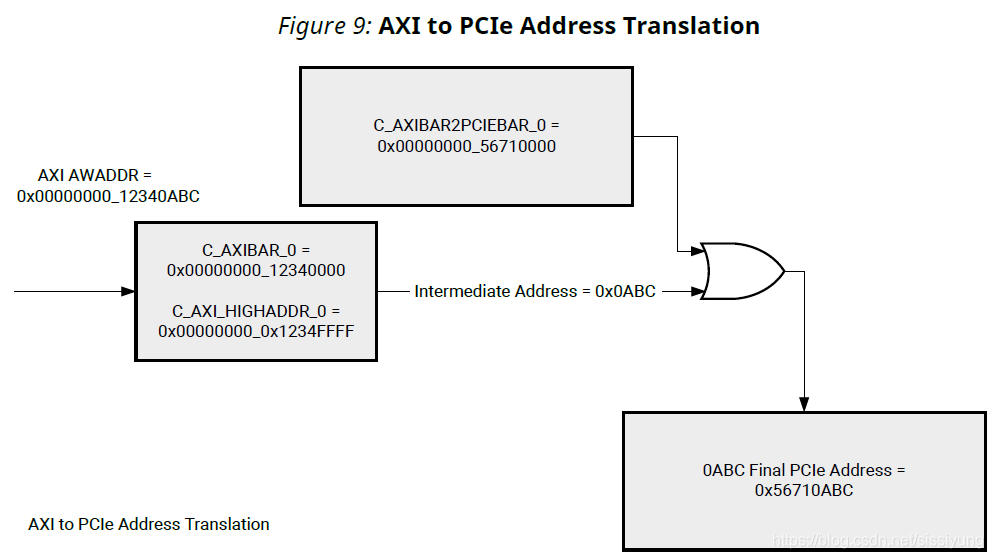

第一个例子是PCIe的地址空间到AXI的地址空间的转换,通过FPGA的bridge发送地址0x0000_12340ABC到远端PCIe设备,这个地址属于BAR0的范围(0x0000_12340000<0x0000_12340ABC<0x1234ffff)。

计算方法是0x0000_12340ABC-0x0000_12340000=0xABC,然后再加上如IP核界面设置AXI to PCIe的转换地址0x56710000等于0x56710ABC。

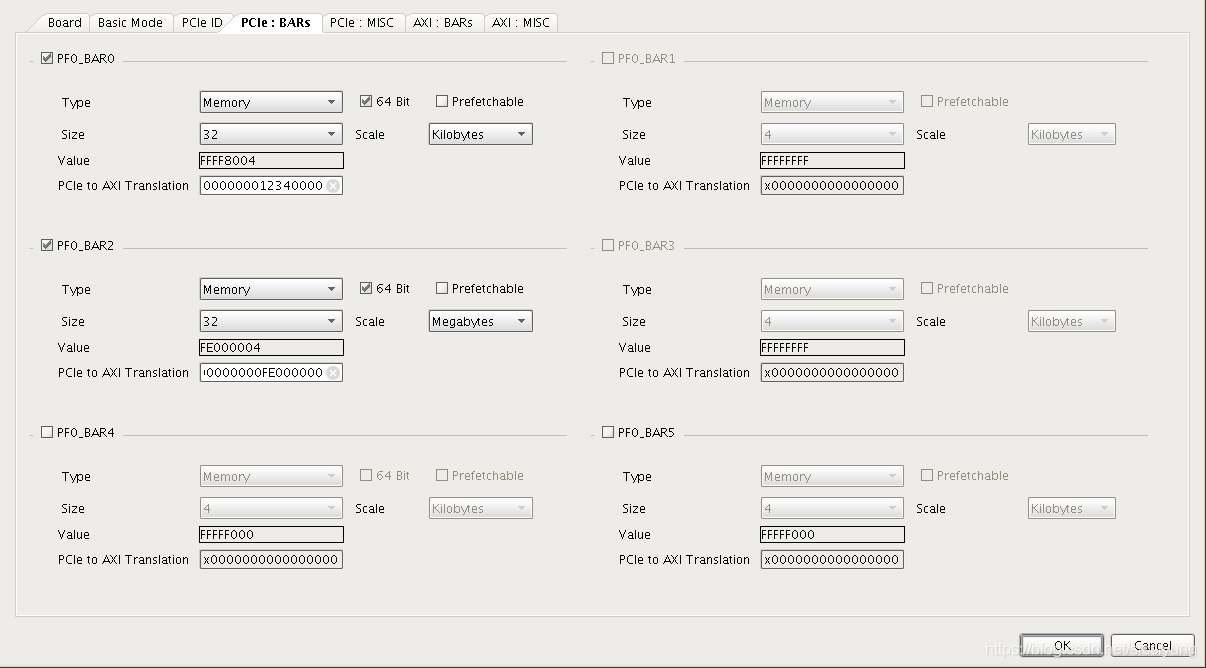

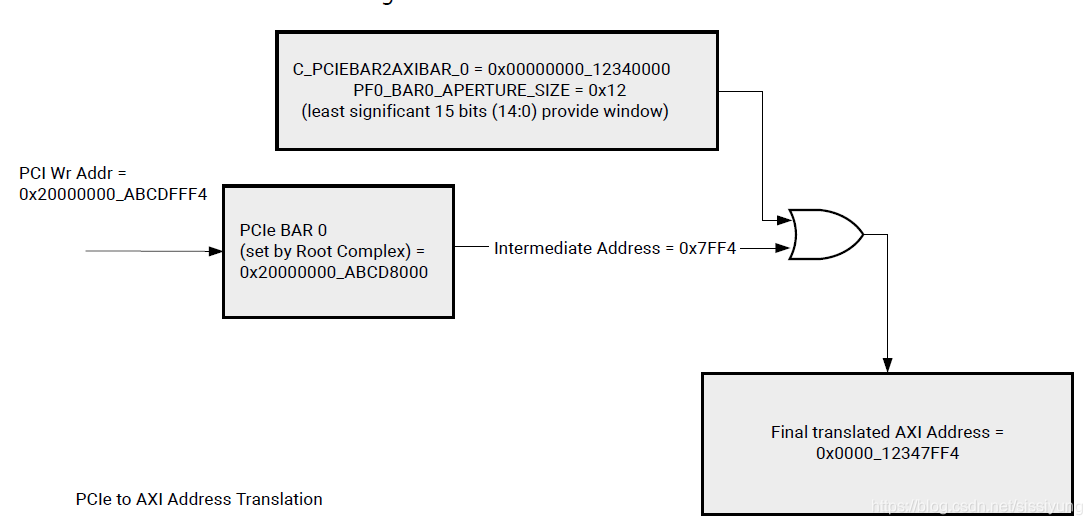

第三个例子是AXI的地址空间到的PCIe地址空间的转换,从远端PCIe发来的地址0x20000000_ABCDFFF4到本地PCIe。该例子中并没有在IP的配置界面出现PCIe的base address,而是在例子描述中表明

BAR 0 is set to 0x20000000_ABCD8000 by the Root Port.

猜测有可能在代码中对bar0的基地址进行了设置。计算方法如下图所示,0x20000000_ABCDFFF4-0x20000000_ABCD8000=0x7ff4,再加上IP核界面设置的PCIe to AXI的转换地址0x12340000等于0x0000_12347FF4

本文详细介绍了PCIe地址空间到AXI地址空间以及AXI到PCIe地址空间的转换过程。通过FPGA桥接,文章阐述了地址转换的计算方法,包括BAR0基地址的设定和转换地址的加减运算。此外,还提及了在实际应用中可能存在的代码设置情况。

本文详细介绍了PCIe地址空间到AXI地址空间以及AXI到PCIe地址空间的转换过程。通过FPGA桥接,文章阐述了地址转换的计算方法,包括BAR0基地址的设定和转换地址的加减运算。此外,还提及了在实际应用中可能存在的代码设置情况。

1083

1083

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?