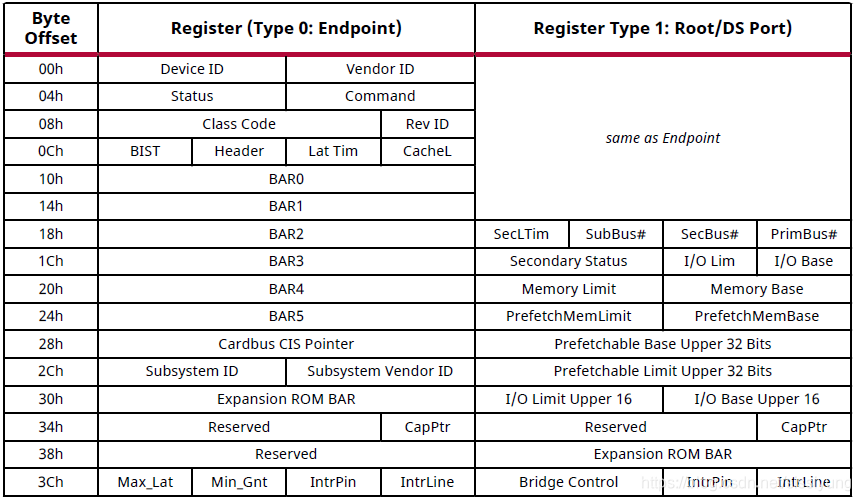

PCI Config Space Header

本问基于xilinx 的xdma IP核内容进行记录

header寄存器如图所示,RC port只有两个BAR可以配置。

以下按照先type0后type1的顺序描述,共同的内容不重复记录

-

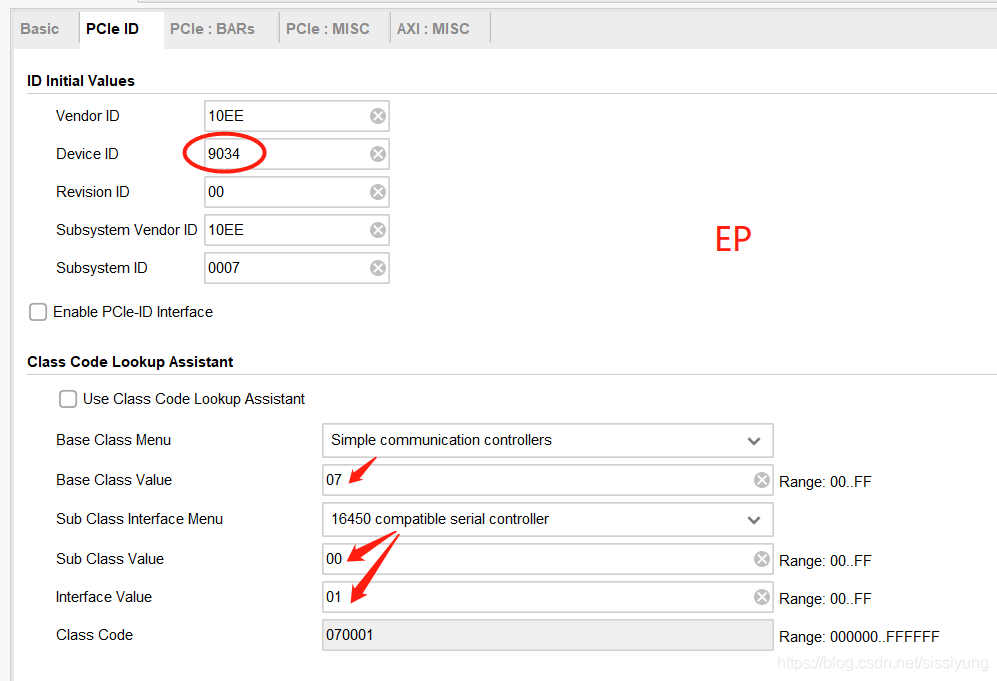

Vendor ID是PCIe设备的生产厂商,Device ID是这个厂商生产的某个具体设备

-

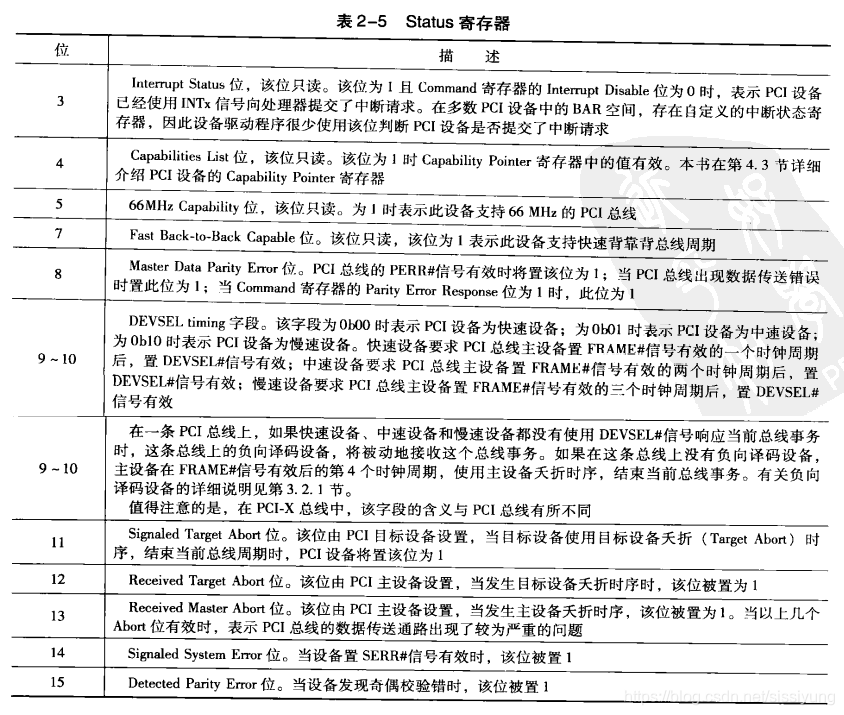

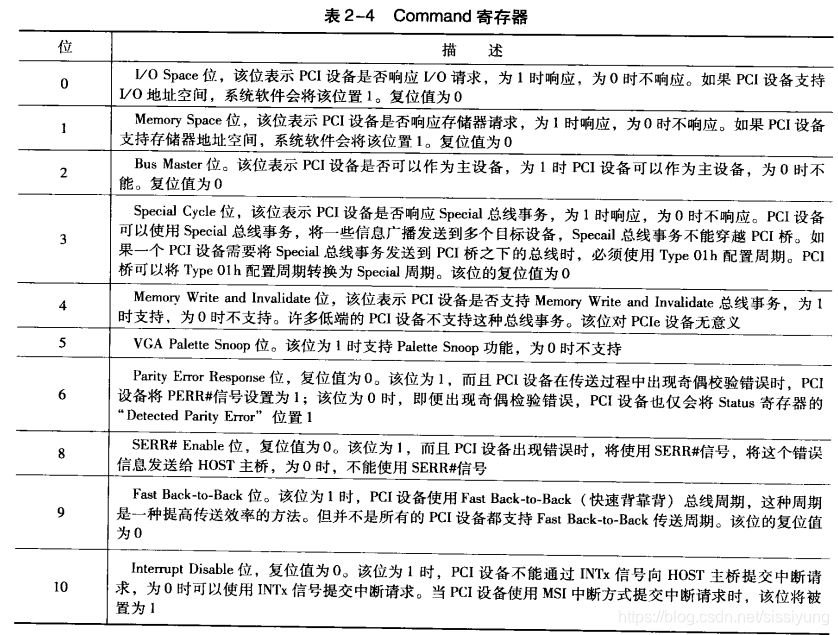

status、commond寄存器内容摘自《PCI Express体系结构导读》。

初始化时,commond寄存器为0,此时只能接收配置总线事务,必须妥善配置commond寄存器,该PCIe的存储或IO空间才能被访问。

-

REV ID(Revision ID)是PCIe设备的版本号(这里是FPGA)。Class Code是PCIe设备的分类。该分类由三个部分组成,分别是base class code 、sub class code和interface。硬件逻辑根据该寄存器识别不同的设备。具体设备对应表见PCIE的Class Code表。

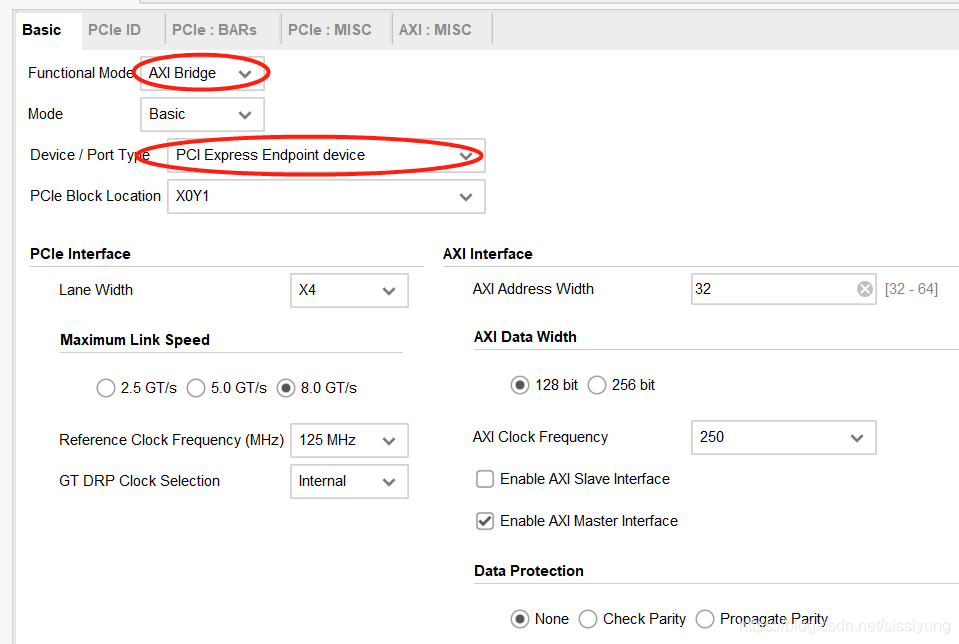

xdma ip核设置页面中选择如下图所示的选项后,第二页默认出现Vendor ID、Device ID、Revision ID、Subsystem Vendor ID、Subsystem ID(下文描述)以及class code配置。

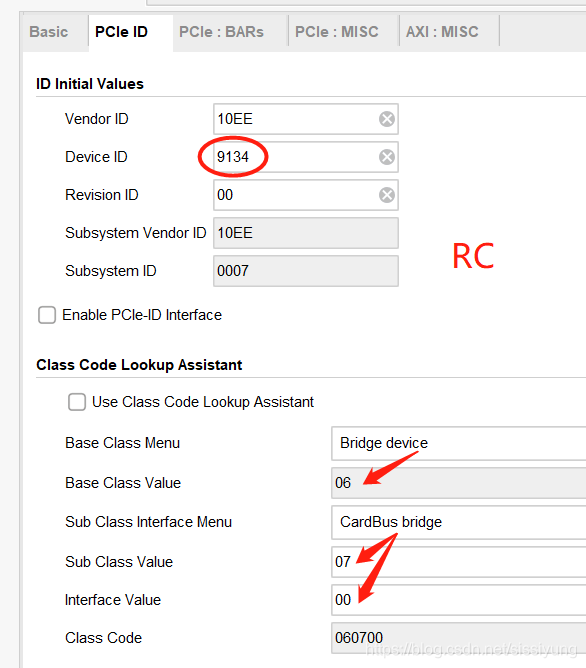

第一页选择Root Port of PCI Express Root Complex后,第二页的参数有所变化。可以看出作为不同的端点,具有不同的Device ID。并且Class ID也不同。下拉框中选择了不同的class,箭头所指的参数也会有相应的变化,和上文链接Class Code表对应。但是箭头所指的填写框也可以自行更改,更改后下拉框并不会变动。

-

BIST:自检功能开启。

-

header type

该寄存器只读,bit7为1表示当前PCIe设备为多功能设备,为0时表示单功能设备。其他bit在PCIe 3.1中没有描述,可以参考《PCI Express体系结构导读》。 -

Lat Tim(Latency Timer):不适用于PCIe设备

-

CacheL(Cache Line Size): 不适用于PCIe设备

-

Cardbus CIS Pointer:只读,用于表明访问CIS(card info structure)的地址空间, 通常不会涉及

-

Subsystem Vendor ID、Subsystem ID

如果使用多个fpga,则仅使用 Vendor ID和Device ID无法区分这些FPGA,所以增加Subsystem Vendor ID和Subsystem ID。 -

Expansion ROM BAR

有些PCIe设备在处理器运行操作系统之前,就要完成基本的初始化设置。该寄存器保存这段初始化ROM程序的基地址。 -

CapPtr:Capabilities Pointer基地址

-

Max_Lat、Min_Gnt:不适用于PCIe设备

-

IntrPin(Interrupt Pin):只读,只用于INIT类型的中断。01 ~ 04对应INITA ~ INITD类型的中断

-

IntrLine(Interrupt Line):记录PCIe设备当前使用的中断向量号(绝大多数处理器系统中不使用)

-

SecLTim(Secondary Latency Timer): 不适用于PCIe设备

-

SubBus#(subordinate Bus Numbers):当前PCIe子树中,最大的PCIe总线号

-

SecBus#(secondary Bus Numbers): 下一级总线号

-

PrimBus#(Primary Bus Number): 上一级总线号

-

Secondary Status:与starus寄存器相似,记录secondary Bus的状态

-

I/O Lim、 I/O Base:访问外部设备寄存器的地址区域,Limit和base一起设置了io空间的地址区域

-

Memory Limi、 Memory Base:访问内存的地址空间

-

PrefetchMemLimit、PrefetchMemBase:可预读的空间,具体机制可参考《PCI Express体系结构导读》

-

Prefetchable Base Upper 32 Bits、Prefetchable Limit Upper 32 Bits:可预读地址高位

-

I/O Limit Upper 16、 I/O Base Upper 16:IO地址高位

-

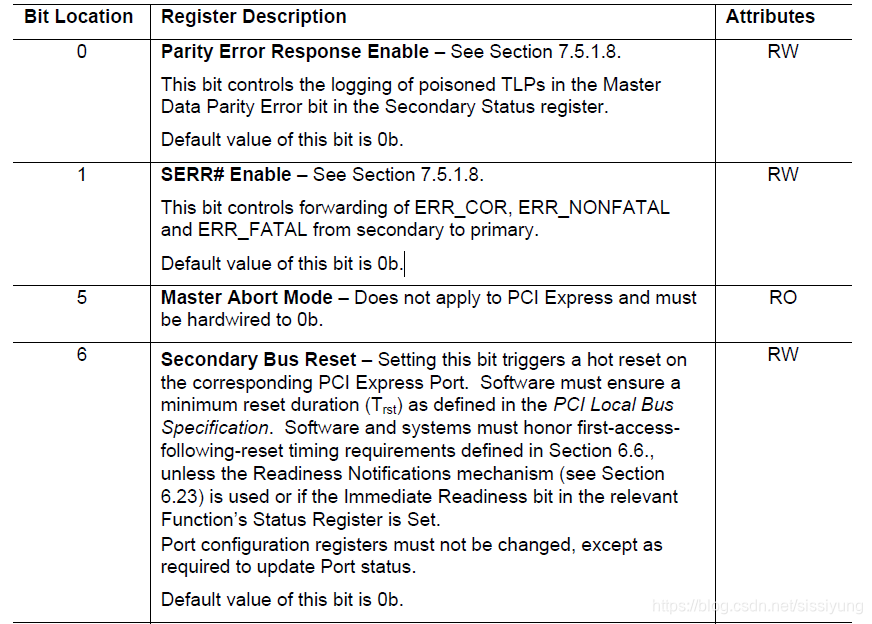

Bridge Control:

-

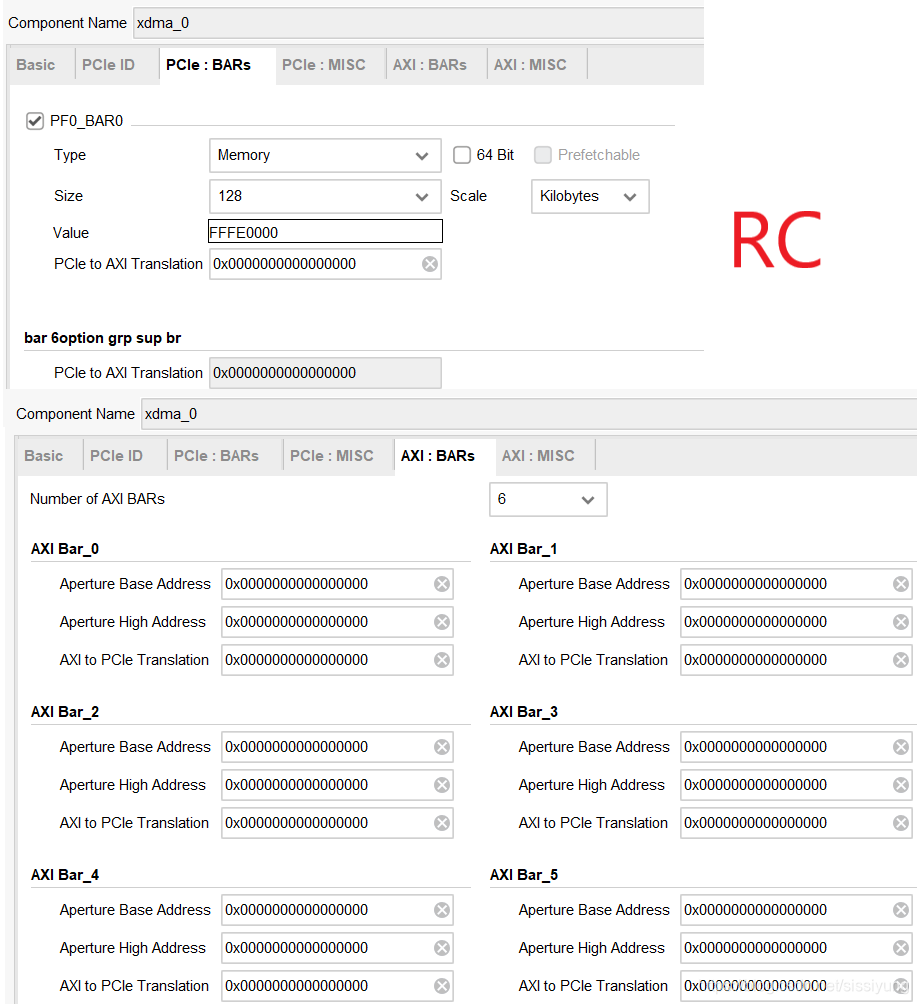

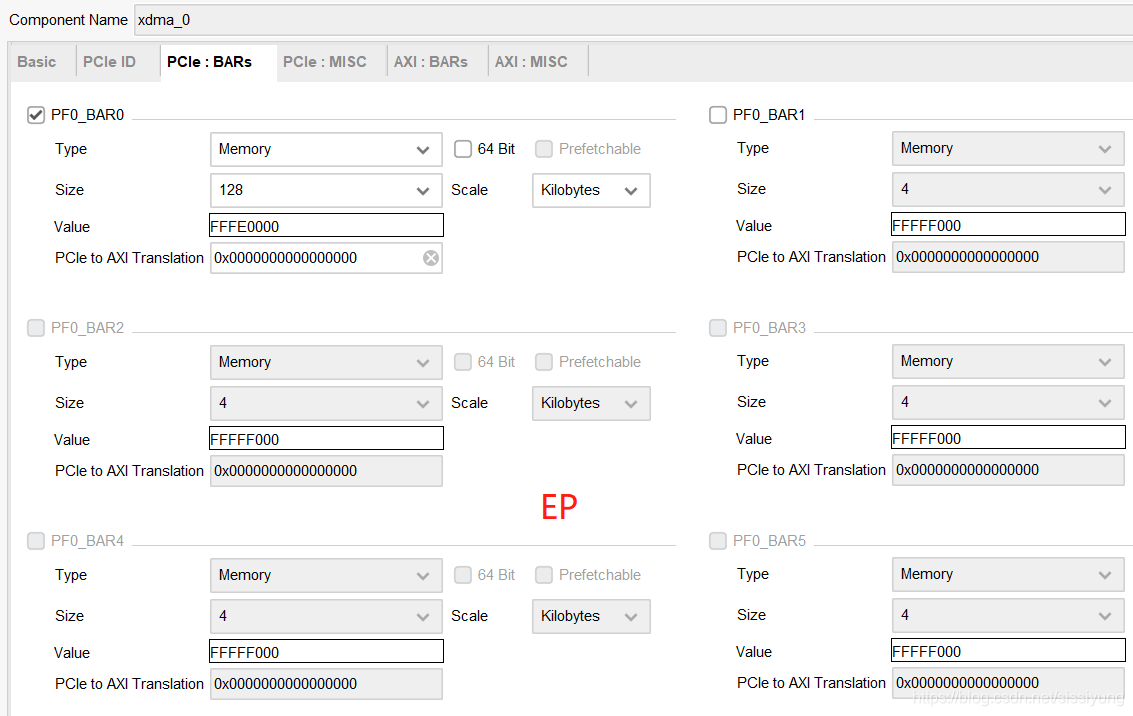

BAR0~5 :基地址寄存器

当选择XDMA为RC模式时有关BAR的界面如图所示,PCIe:BARs应该是设置fpga的BAR,而AXI:BARs应该是设置与之相连的内存分配BAR。这里PCIe只有一个BAR0,是xilinx的ip核限制。而AXI最多有6个BAR可以配置,符合type0的寄存器格式。

当选择XDMA为EP模式时有关BAR的界面如图所示,因为FPGA属于type0模式,所以可以有6个BAR空间。但此时AXI还是有6个BAR空间可以配置,不太理解,有可能对AXI的bar理解有误。

第一页设置中去掉勾选Enable AXI Slave Interface,AXI:BAR这一栏就会消失,应该可以由另外一端PCIe设备自己配置。

除了基础的header配置空间以外,还有Capabilitiy配置空间和扩展配置空间。不是所有都能用到。以后用到了再记录。

272

272

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?