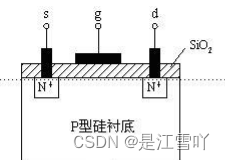

首先,漏电流是什么?N沟三极管示意图如下,在SiO2或者N+上会附着一些自由电子,导致某两级存在微小电流,这一电流就是漏电流。说是某两级是因为它可能是不同二极管的D到D,同一二极管的D到S等。

OS测试和漏电流测试都属于DC测试的一部分,DC测试的目的是尽早筛出结构异常或者不符合要求的芯片。通常来讲,OS是结构问题,Leakage是功耗问题。

VDD就是整体功耗,在指定电压下,需要多少电流来维持它的工作状态,因此有个IDD(Current from Drian to GND)。不同脚的输入输出电流,为了输入/输出指定电平的信号,这个引脚需要的电流是多大,因此根据脚状态的不同又有不同的测试,如IIL/IIH/IOZ/IOS,全称是Input Leakage Low/High此类的缩写,不过为了方便理解说清楚的就是:current of input/output pin when it is at Low/High/High-Z/Short status,当一个输入/输出脚在低/高/高阻态下的电流。

IDD有静态和动态的区别,静态是指芯片没有工作,类似于休眠(低功耗)状态,需要注意的是输入输出脚在这种情况下的状态。例如芯片reset后,输出脚和外部负载断开,输入脚按照要求设定到低电平(通常为0)或者高电平(通常为VDD),这时候去量给VDD提供电流,就是IDD,也是Gross IDD,漏电流总和,即电源到GND的漏电流。动态是指芯片处于工作状态,类似于你的电脑正在使用中,去测量提供的电流,同样要注意引脚状态。

I/O脚的漏电流,input脚和output脚同样要分开来测。

IIL是当芯片上电后,想要给驱动一个输入脚输入低电平所需要的电流大小,the Current to force Input pin to Low,同理,IIH就是驱动输入脚为高电平的电流。IOZ是指当芯片上电后,输出管脚处于高阻态下时,将低电平(L)或者高电平(H)施加到这个输出脚所产生的漏电流(IOZL/IOZH),结合上一次所述的CMOS结构,IOZL实际测的是电源到输出管脚的漏电流,只不过需要注意的是,为了数据更合理,引脚在测试之前徐对管脚进行预处理,例如测试IIL时,将引脚先拉到高电平,再驱动一个低电平给它后量电流,测IIH时,先将引脚预置到低,再驱动高电平量电流。

漏电流基本上也就这些,不过看上面缩写字符,可能会有这样的疑问,IOL和IOH去哪儿了?

IOL/IOH都是和VOL/VOH捆绑出现,和IIL/IIH类似,都是驱使一个脚处于低电平和高电平状态的电流,例如已知参数VOL/IOL,当芯片的输出脚被设定在正确的状态(0),在输出脚灌电流IOL,观察VOL是否达标。已知VOH/IOH,在输出脚是拉电流IOH,量VOH是否达标。所以这两个参数我们通常force I measure V。

最后的最后,我不是很会写这些东西,平时大多在阅读大佬们的文章,所以容易忽略文章的评论和消息,实在抱歉,请见谅。由于本人使用的J750居多,后续计划是讲一讲基于750的测试程序。

PS:为什么CSDN文章标签没有半导体呀,难受难受难受。

1727

1727

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?