JEDEC 技术协会公布新 DDR5 内存规范、更稳定、安全,支持 PRAC 新技术

下载:

https://download.csdn.net/download/tgs2033/89661013

样本下载:

链接:https://pan.baidu.com/s/13-IoepcYxUM4bYvWxQRovQ?pwd=1234

提取码:1234

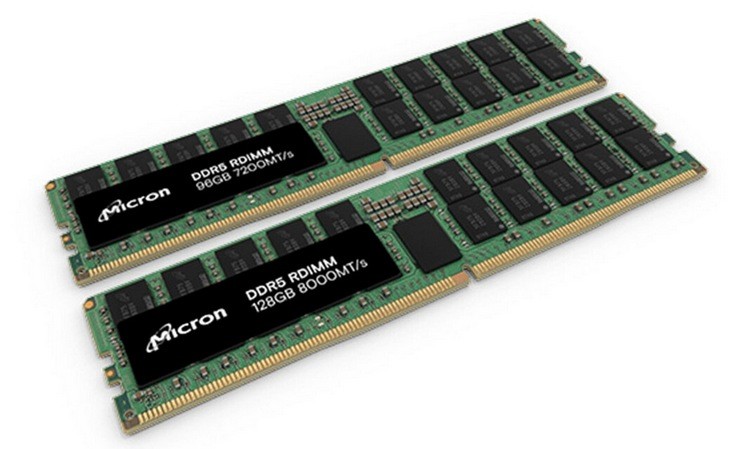

JEDEC 技术协会今天发布了新的 JESD79-5C DDR5 SDRAM 内存技术规范,旨在提高可靠性和安全性,并增强从高性能服务器到人工智能和机器学习等新兴技术的性能。

该规范引入了一种

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

640

640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?